I

Изобретение относится к технике связи для .передачи и приема дискретных сообщений, предназначено для подстройки фазы тактовых импульсов по кодовым информационным посыпкам, поступающим на вход устройства из канала связи, и может быть применено в системах с жестко установленной длительностью кодовых посылок, равно периоду следования кодовых импульсов

Целью изобретения является повышение помехоустойчивости.

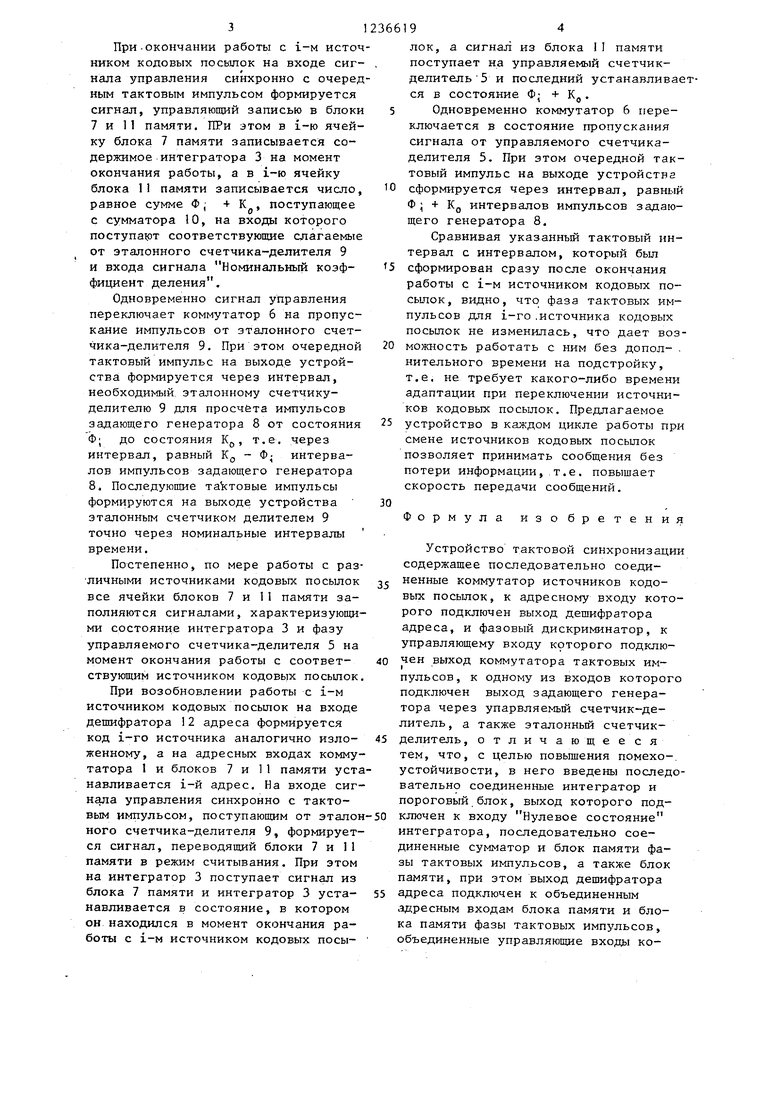

Ба чертеже представлена структурная электрическая схема, устройства тактовой синхронизации.

Устройство тактовой синхронизации содержит коммутатор 1 источников кодовых посыпок, фазовый дискриминатор 2, интегратор 3, пороговый блок 45 управляемый счетчик-делитель 5, коммутатор б тактовых импульсов, .блок 7 памяти, задающий генератор 8, эталонный счетчик-делитель 9, сумматор 10} блок 11 памяти фазы тактовых импульсов и дешифратор 12 адреса

Устройство тактовой синхронизации работает следующим .образом.

При установке на входе сигнапа Номер источника кодовых посылок определенкого з,--го номера источника кодовых посылок дешифратор 12 адреса формирует адресный сигнал, который поступает на адресные входы блоков и 11 памяти и устанавливает комлмутатор 1 в состояние пропускания сигнала от i-ro источника кодовых посылок. На входе сигнала упрления при этом устанавливается сигнал, открывающий коммутатор 6 на прпускание импульсов от управляемого счетчика-делителя 5,, Сигнал от задающего генератора 8 поступает на счетные входы эталонного и управляемого счетчиков-делителей 9 и 5, причем эталонный счетчик-делитель 9 настроен на номинальный коэффициент деления считает импульсы задающего генератора 8 циклически от О до Кд 5 при прохождении через О вырабатывает сигнал на своем импуль ном выходе, а управляемый счетчик- делитель 5 работает в режиме отрицательного счета, считая импульсы задающего генератора 8 от К, (-ши другого, устанавливаемого на него коэффициента К) до 0. В нулевом состоянии управляемый счетчик-делитель 5 вырабатывает импульс, проходящий

2366192

через коммутатор 6, являющийся выходным сигналом устройства и посту- паю1ци:й также на управляющий вход фазового диcкpи шнaтopa 2, на информа- 5 ционный вход которого поступает сигнал от i-ro источника кодовых посы0

S

20

2fi

5055

лок, прошедший через коммутатор I. Фазовый дискриминатор 2 вырабатывает сигнал разности фаз, находящийся в прямой зависимости от интервала времени между тактовым импульсом и границей кодовой посылки. Сигнал разности фаз накапливается в интеграторе 3 и в конце каждого такта сравнивается с заданнььми порогами в поре- говом блоке Д, выходной сигнал которого поступает на управляющий вход управляемого счетчика-делителя 5„ Если содержимое интегратора 3 не пре- вьшает заданных порогов, на управляемый счетчик-делитель 5 устанавливается номинальный коэффициент деления KQ, и длина очередного такта является номинальной. В случае,если, границы кодовых посылок опережают тактовые импульсы н сигнал положительной разности фаз накапливается в интеграторе 3 до величины, превышающей положительный порог, на управ- 30 ляемый счетчик-делитель 5 устанавливается уменьшенный коэффициент деления, например К,.

и очередной

0 5

5

такт укорачивается на один интервал импульсов задающего генератора 8, ОдноЕ1ременно сигнал порогового блока 4 в случае превьштения порога сбрасывает интегратор 3 в нулевое состояние, после чего накопление сигнала возможной разности фаз в иь- теграторе 3 начинается сначала. Аналогичным образом устройство работает при отставании границ кодовых посылок от тактовых импульсов. В этом случае при превышении содержимым интегратора 3 отрицательного порога на управляемый счетчик-делитель 5 устанавливается увеличенньй коэффициент деления, .например К, + 1, и очередной такт удлиняется на один интервал импульсов задающего генератора 8. Так происходит приближение тактовых импульсов к границам кодовых посылок i-ro источника. При этом фаза тактовых импульсов для i-ro источника кодовых посылок определяется состоянием Ф; эталонного счетчика-делителя в момент возникно--- вения тактовых импульсов.

31

При-окончании работы с i-м источником кодовых посылок на входе сигнала управления синхронно с очередным тактовым импульсом формируется сигнал, управляющий записью в блоки 7 и 11 памяти. ПРи этом в i-ю ячейку блока 7 памяти записывается содержимое интегратора 3 на момент окончания работы, а в i-ю ячейку блока II памяти записывается число, равное сумме Ф , К , поступающее с сумматора 10, на входы которого nocTynaipT соответствующие слагаемые от эталонного счетчика-делителя 9 и входа сигнала Номинальный коэффициент деления.

Одновременно сигнал управления переключает коммутатор 6 на пропускание импульсов от эталонного счетчика-делителя 9, При этом очередной тактовый импульс на выходе устройства формируется через интервал, необходимый эталонному счетчику- делителю 9 для просчёта импульсов задающего генератора 8 от состояния Ф; до состояния Кр, т.е. через интервал, равный К,, - Ф; интервалов импульсов задающего генератора 8, Последующие тактовые импульсы формируются на выходе устройства эталонным счетчиком делителем 9 точно через номинальные интервалы времени.

Постепенно, по мере работы с раз- ЛИЧНЫМИ источниками кодовых посылок все ячейки блоков 7 и 11 памяти заполняются сигналами, характеризующими состояние интегратора 3 и фазу управляемого счетчика-делителя 5 на момент окончания работы с соответствующим источником кодовых посылок

При возобновлении работы с i-м источником кодовых посылок на входе дешифратора 12 адреса формируется код i-ro источника аналогично изложенному, а на адресных входах коммутатора 1 и блоков 7 и И памяти устанавливается i-й адрес. На входе сигнала управления синхронно с тактовым импульсом, поступающим от эталон ного счетчика-делителя 9, формирует ся сигнал, переводящий блоки 7 и 11 памяти в режим считывания. При этом на интегратор 3 поступает сигнал из блока 7 памяти и интегратор 3 устанавливается в состояние, в котором он находился в момент окончания работы с i-M источником кодовых посы2366194

лок, а сигнал из блока II памяти поступает на управляемый счетчик- делитель 5 и последний устанавливается в состояние Ф; + Kg. 5 Одновременно коммутатор 6 переключается в состояние пропускания сигнала от управляемого счетчика- делителя 5. При этом очередной тактовый импульс на выходе устройства

10 сформируется через интервал, равный Ф ; + Kg интервалов импульсов задающего генератора 8.

Сравнивая указанный тактовый интервал с интервалом, который бьш

5 сформирован сразу после окончания работы с i-M источником кодовых по- сьшок, видно, что фаза тактовых импульсов для i-ro .источника кодовых посьшок не изменилась, что дает воз20 можность работать с ним без допол- . нительного времени на подстройку, т.е. не требует какого-либо времени адаптации при переключении источников кодовых посылок. Предлагаемое

25 устройство в каждом цикле работы при смене источников кодовых посыпок позволяет принимать сообщения без потери информации, т.е. повышает скорость передачи сообщений.

30

Формула изобретения

Устройство тактовой синхронизации содержащее последовательно соеди3 ненные коммутатор источников кодовых посьшок, к aдpecнo ry входу которого подключен выход дешифратора адреса, и фазовый дискриминатор, к управляющему входу которого подклю40 чен выход коммутатора тактовых импульсов, к одному из входов которого подключен выход задающего генератора через упарвляемый счетчик-делитель , а также эталонный счетчик45 делитель, отличающееся тем, что, с целью повьш1ения помехо-. устойчивости, в него введены последовательно соединенные интегратор и пороговый блок, выход которого под- 50 ключен к входу Нулевое состояние интегратора, последовательно соединенные сумматор и блок памяти фазы тактовых импульсов, а также блок памяти, при этом выход дешифратора

55 адреса подключен к объединенным

адресным входам блока памяти и блока памяти фазы тактовых импульсов, объединенные управляющие входы ко5 12366196

торых и управлякящй вход коммутато-щему входу управляемого счетчикара тактовых импульсов являются вхо-делителя, к управлякщему входу кото

дом сигнала управления, выход задаю-рого подключен выход порогового бло

щего генератора через эталонный счет-„ ка, вход которого объединен с соотчик-делитель подключен к другомуветствующим входом блока памяти, вывходу коммутатора тактовых импульсовход которого подключен к одному из

и к первому входу сумматора, второйвходов интегратора, к другому входу

вход которого является входом сигна-которого подключен выход фазового

ла Номинальный коэффициент деления,JQ дискриминатора, вход дешифратора ад-.

выход блока памяти фазы тактовыхреса является входом сигнала Номер

импульсов подключен к соответствую-источника кодовых посылок.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1988 |

|

SU1596473A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство тактовой синхронизации | 1980 |

|

SU896779A1 |

| Система адресного вызова с позиционным кодированием | 1980 |

|

SU907871A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

Изобретение относится к технике связи. Цель изобретения - повысить помехоустойчивость. Устройство со- держит коммутатор 1 источников кодовых посылок, фазопый дискриминатор 2, интегратор 3, пороговый блок (ПБ) 4, управляемый счетчик-делитель 5, коммутатор 6 тактовых импульсов, блок памяти (БП) 7, задаю шй генератор 8, эталонный счетчик-делитель 9, сумматор (С) 10, БП И фазы тактовых импульсов и дешифратор 12 адреса. В системах кодовых импульсов, данное устройство осуи;ествляет подстройку фазы тактовых импульсов по кодовым информационным посылкам, поступаю1цим на вход устройства из канала связи. Цель достигается введением интегратора 3, ПБ4, БП7, ПиСЮ. 1ил. О Sxoffl. вхо 0- Ю ОО о: со -0 «ijb. --о

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ПЕРЕРЫВОВ ЦИФРОВОГО СИГНАЛА В РАДИОКАНАЛЕ | 0 |

|

SU390676A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU896779A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство групповой тактовой синхронизации | 1980 |

|

SU921107A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-06-07—Публикация

1982-10-01—Подача