Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки цифровой информации повышенной надежности,

Цель изобретения - сокращение объема аппаратуры.

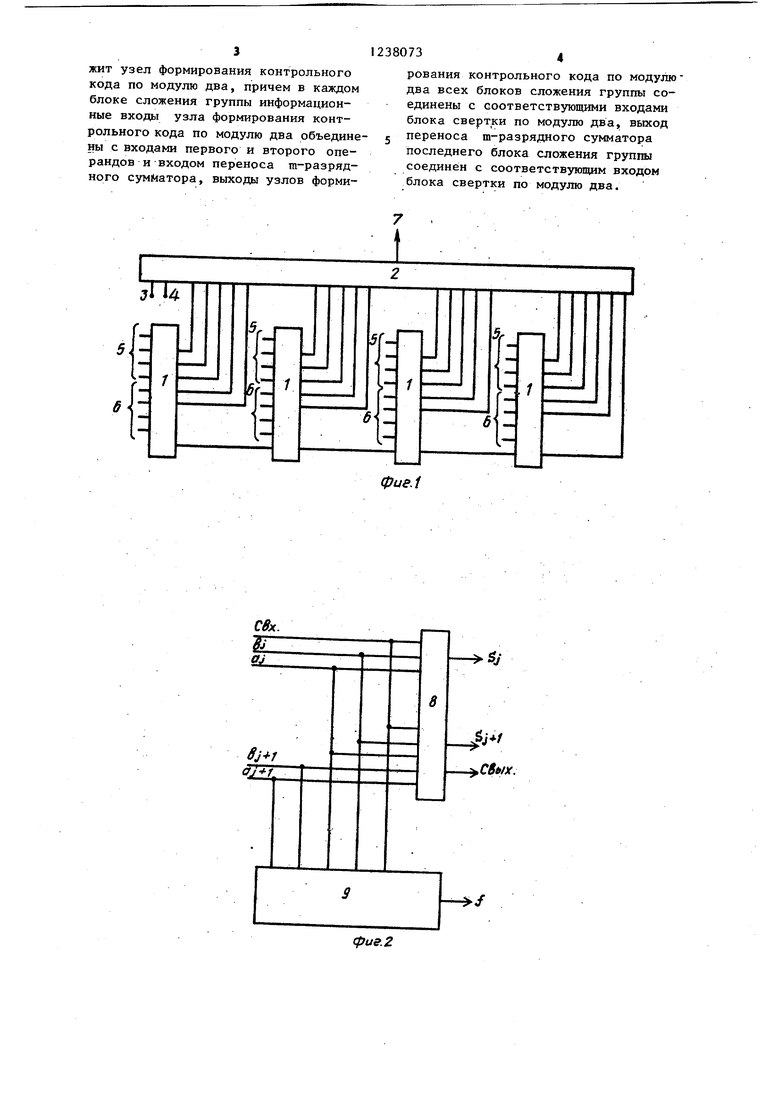

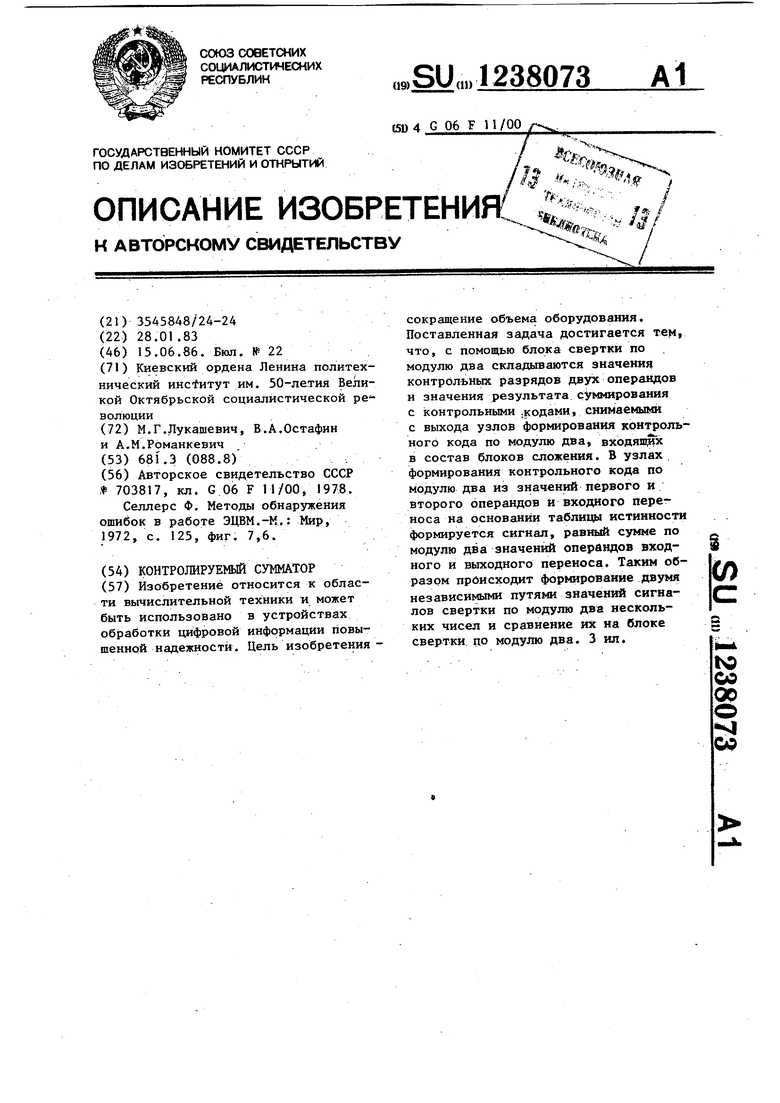

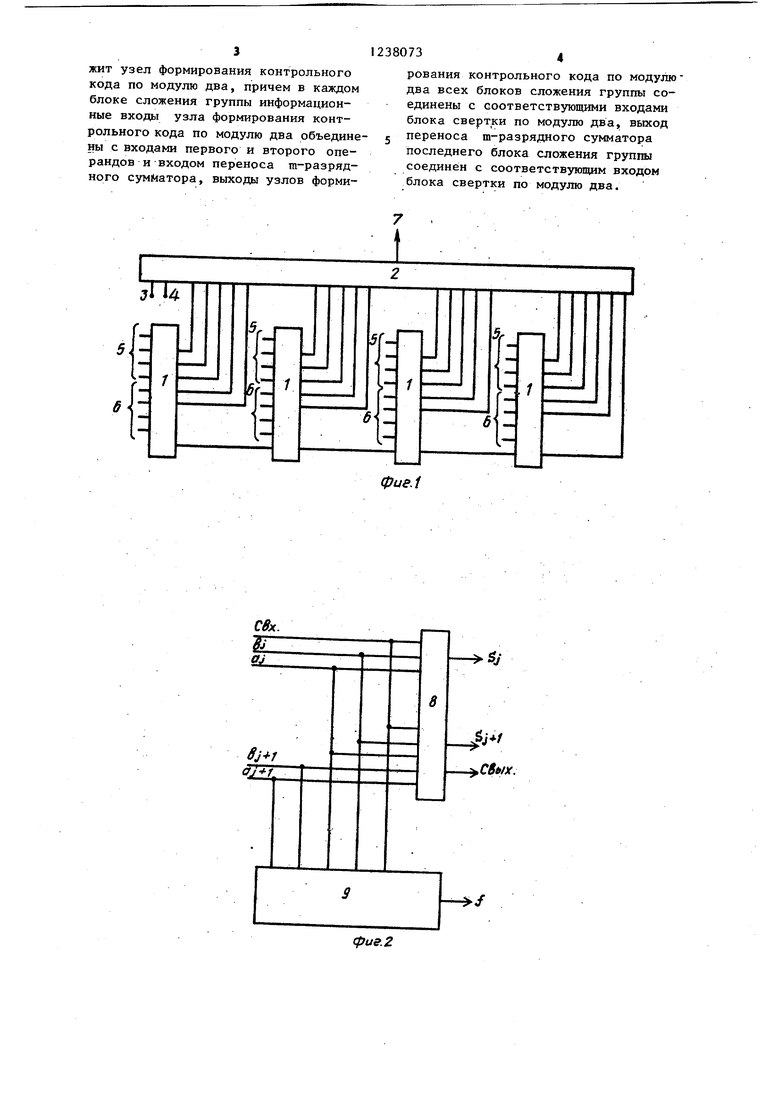

На фиг. 1 приведена структурная схема контролируемого сумматора; на фиг. 2 - функциональная схема блока сложения; на фиг. 3 - то же, узла формирования контрольного кода по модулю два для двухразрядного блока сложения.

Контролируемый сумматор (фиг.1) содержит группу 1 блоков сложения, блок 2 свертки по модулю два, входы 3 и 4 контрольных разрядов первого и второго операндов контролируемого сумматора, группы 5 и 6 входов пер- вого и второго операндов контролируемого сумматора, выход 7 неисправности контролируемого сумматора. Блок сложения группы 1( фиг.2) содержит ш-разрядный сумматор 8 (в данном случае ш 2) и узел 9 формирования контрольного кода по модулю два.

Узел 9 формирования контрольного кода по модулю два (фиг.З) содержит группу элементов И 10, элемент ИЛИ П и группу элементов НЕ 12.

Контролируемый сумматор работает следующим образом.

На входы блока 2 свертки по моду- лю два поступают контрольные разряды двух операндов, сигналы с выходов результата т-разрядных сумматоров 8 всех блоков сложения группы 1, а также выход переноса т-разрядного сумматора 8 последнего блока всложе- ния группы 1.

Узел 9 формирования контрольного кода по модулю два реализует функцию

г,

г; Ь

(±)...® . ® S,.

®

2.;

IT ©...

+ С

bJt,

BwKj

а.

значения разрядов первого операнда; значения разрядов второго операнда; значения разрядов результата сумматора 8;

exi

Вых.

- значения сигналов входного и выходного переносов сумматора 8.

Таким образом формируется контрольный код, равный сумме по модулю два значений операторов, результата и переносов.

При правильной работе контролируемого сумматора на выходе 7 неисправности будет нулевой сигнал. Наличие на этом выходе единичного сигнала говорит об ошибке в работе контролируемого сумматора.

Блок сложения группы 1 может быть выполнен в виде блока памяти, где операнды и входной перенос поступают на адресный вход. В каждой ячейке блока памяти при этом должен храниться результат суммирования, значение выходного переноса и значения f..

Формула изобретения

Контролируемый сумматор, содержащий блок свертки по модулю два и группу блоков сложения, каждый из которых содержит т-разрядный сумматор

V

k

где п - разрядность конт

ролируемого сумматора, К - количество блоков сложения в группе), причем входы первого и второго операндов всех щ-разрядных сумматоров блоков сложения группы образуют соответственно группы входов первого и второго операндов контролируемого сумматора, выходь результата всех т-разрядных сумматоров блоков сложения группы соединены с соответствующими входами блока свертки по модулю два, выход переноса каждого т-разрядного сумматора предьщущего блока сложения группы соединен с входом переноса т-разрядного сумматора последующего блока слозЬения группы, вход переноса т-разрядного сумматора первого блока сложения группы соединен с шиной нулевого потенциала, устройства, входы контрольных разрядов первого и второго операндов контролируемого сумматора соединены с соответствующими входами блока свертки по модулю два, выход которого является выходом неисправности контролируемого сумматора, отличающийся тем, что, с целью сокращения объема аппаратуры, каждый блок сложения содержит узел формирования контрольного кода по модулю два, причем в каждом блоке сложения группы информационные входы узла формирования контрольного кода по модулю два объединены с входами первого и второго операндов и входом переноса т-разряд- ного сумматора, выходы узлов форми5J- -«

рования контрольного кода по модулю два всех блоков сложения группы соединены с соответствующими входами блока свертки по модулю два, выход переноса т-разрядного сумматора последнего блока сложения группы соединён с соответствукицим входом блока свертки по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики группы типовых элементов замены | 1977 |

|

SU857996A1 |

| Устройство для контроля сумматора | 1983 |

|

SU1111167A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1608653A1 |

| Устройство для контроля на четность двоичной информации | 1981 |

|

SU1015388A1 |

| Блок предсказания четности результата арифметико-логического устройства | 1977 |

|

SU684548A1 |

| Устройство для сложения чисел с контролем | 1978 |

|

SU885995A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для контроля умножения двоичных чисел по модулю три | 1988 |

|

SU1774337A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| Устройство для умножения с контролем | 1989 |

|

SU1741128A1 |

Изобретение относится к области вычислительной техники и может быть использовано в устройствах обработки цифровой информации повышенной надежности. Цель изобретения сокращение объема оборудования. Поставленная задача достигается тем, что, с помощью блока свертки по модулю два складываются значения контрольных разрядов двух операндов и значения результата суммирования с контрольными .кодами, снимаемыми с выхода узлов формирования контрольного кода по модулю два, входяпцпс в состав блоков сложения. В узлах формирования контрольного кода по модулю два из значений первого и второго операндов и входного переноса на основании таблихцл истинности формируется сигнал, равный сумме по модулю два значений операндов входного и ВЫХОДНОГО переноса. Таким образом происходит форнированйе двумя независимыми путями значений сигналов свертки по модулю два нескольких чисел и сравнение их на блоке свертки цо модулю два. 3 ил. (П с to со х о СР

cfjf-f

(риг. 2

j4f aj sj свх.

Редактор М.Товтин

Составитель В.Гречнев Техред М.Ходанич

Заказ 3292/49 Тираж 671Подписное

ВН1даПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.А/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная,4

Корректор Л.Натай

| Контролируемый параллельный сумматор | 1977 |

|

SU703817A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Селлерс Ф | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Плуг с фрезерным барабаном для рыхления пласта | 1922 |

|

SU125A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1986-06-15—Публикация

1983-01-28—Подача