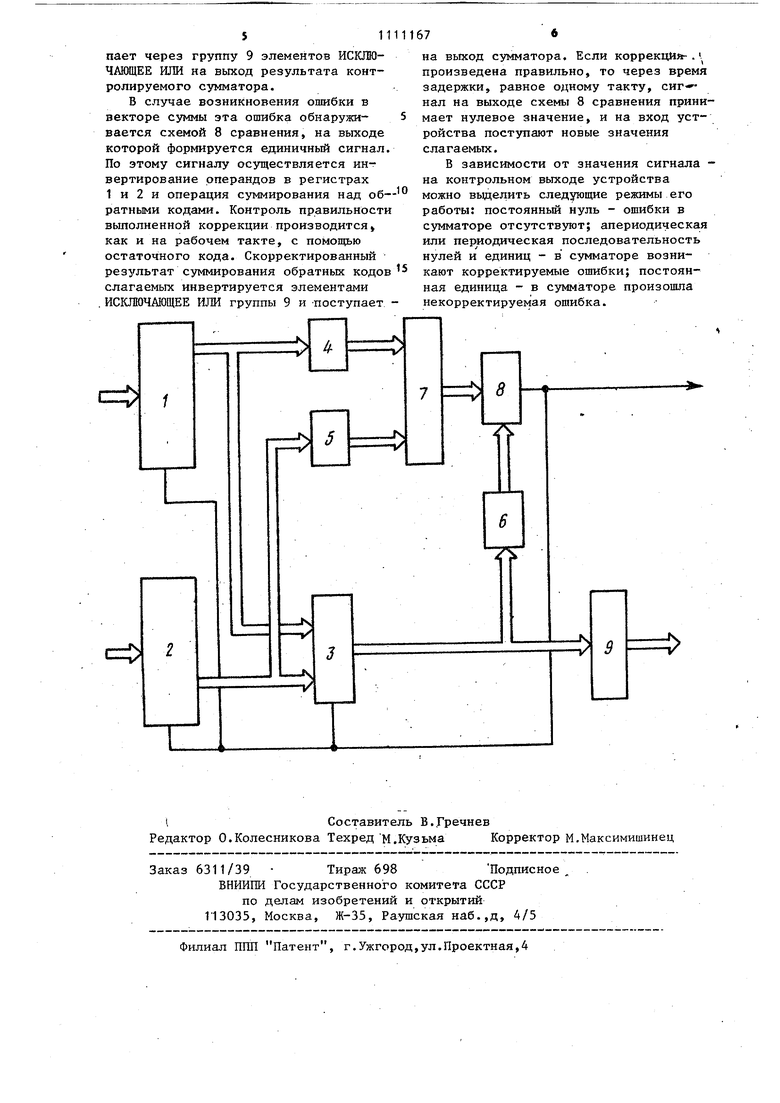

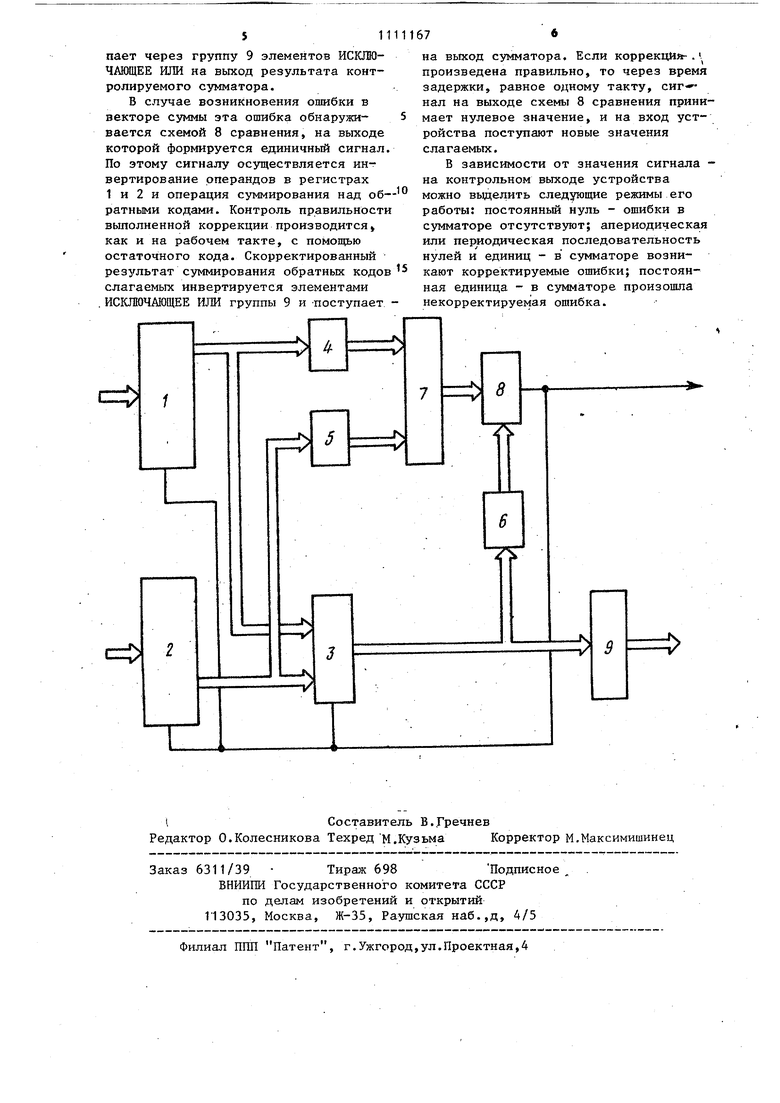

Изобретение относится к области вычислительной техники и может быть использовано в ЦВМ и устройствах обработки цифровой информации новы-, шейной надежности. Известно арифметическое устройство с контролем и коррекцией ошибок, в котором для контроля логических операций производится сравнение результатов, полученных одновременно на сумматоре прямых значений кода и сум маторе инверсных значений кода, содержащее четыре регистра, четырнадтцать групп вентилей прямой и инверс ной передачи кодов, два сумматора схему кодирования, схему сравнения, блок формирования признаков ошибок и блок сверток С11. Недостатком указанного устройства йвляется его сложность и невысокая достоверность контроля из-за большого количества контрольного обору- дования. Наиболее близким по технической сущности к предлагаемому является сумматор, контролируемый с псмяощью остаточного кода, содержащий два регистра слагаемых, выходы каждого из которых подключены к соответствующим входам сумматора слагаемых и соответственно к входам первого и второго блоков вычисления остатка помодулю т, причем выходы itepBoro и второго блоков вбгчисления остатка по модулю ил подключены к входам сум матора остатков, выход которого подключен к первому входу схемы/сравнения, второй вход схемы сравнения соединен с выходом третьего блока вычисления остатка по модулю УГ , вход которого подключен к выходу сусумматора слагаемых, который является выходом результата сумматора, выход схемы сравнения является выходом ошибки сумматора. При m 3 в сумматоре обнаруживаются все одиночные ошибки С 21. Недостатком данного устройства является невозможность корректирования результата при обнаружении опшбо Цель изобретения повьщ1ение достоверности контроля. Поставленная цель Достигается тем что в устройство для контроля сумматора, содержащее регистры первого и второго слагаемых, три блока формиро вания остатка по модулю пл , сут матор слагаемых, сумматор остатков, схему сравнения, причем информационные входы регистров первого и вторрго слагаемых являются соответственно входами первого и второго.слагаемых устройства, выходы регистров первого и второго слагаемых соединены соответственно с первым и вторым информационными входами сумматора слагаемых и входами первого и второго блоков формирования остатка по модулю wi , выходы которых соединены соответственно с первым и вторым информационными входами сумматора остатков, выходы которого соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами третьего блока ормирования остатка по модулю m , входы ко-г торого соединены с выходами сумматора слага емых, выход схемы сравнения является выходом ошибки устройства, введена группа элементов ИСКЛЮЧАЮЩЕЕ ШШ, причем выходы сумматора слагаемых соединены с перВыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, вторые входы которых объединены и соединены с выходом схемы сравнения, входом переноса сумматора слагаемых и управляющими входами регистров первого и второго слагаемых, выходы элементов ИСЮТОЧАЮЩЕЕ ИШ грзгапы являются выходами результата устройства, На чертеже изображена функциональная схема устройства для контроля сумматора, который содержит регистр 1 первого слагаемого, регистр 2 второго слагаемого, сумматор 3 слагаемых, блоки 4-6 формирования остатка по модулю т, сумматор 7 остатков, схему 8 сравнения, группу 9 элемептов ИСКЛОЧАЮЩЕЕ ИЛИ. Информационные входы регистров 1,2 первого и второго слагаемых являются соответственно входами первого и второго слагаемых контролируемого сумматора, выходы регистров 1,2 соединены соответственно с первым и вторым входами сумматора 3 слагаемых и входами первого и второго блоков 4,5 формирования остатка по п.. Выходы сумматора 3 слагаемых соединены с входами третьего блока 6 формирования остатка по модулю П и первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 9, выходы которых являются выходом результата контролируемого сумматора. Выходы блоков 4 и 5 соеди нены с соответствуюпщми информационными входами сумматора 7 остатков Выходы сумматора 7 остатков и третьего блока 6 формирования остатка по модулю соединены соответственно с первой и второй группами входов схемы 8 сравнения, выход которой является выходом ошибки контролируемого сумматора и соединен с вторыIми входами всех элементов ИСКЛЮЧАЩЕЕ ИЛИ, входом переноса с.умматора 3 сла гаемых и управляющими входат-ги регист ров 1,2. Регистры 1 и 2 могут быть построены на триггерах со счетчным входом, подключенным к управляющему входу регистра, либо на Т) -триггерах и содержать элементы ИСКЛОЧАЮЩЕЕ ИЛИ, первые входы которых соединены с прямыми выходами разрядных триггеров а вторые - с управляющим входом регистра Схема 8 сравнения должна обладать внутренней задержкой на один такт, реализуемой на Т)-триггерах. Для обеспечения правильного корректирования ошибок необходимо, чтобы отказы в dxeMe формирования суммы и переносов вызывали асимметричные ;ошибки, т.е. ошибки постоянного типа С этой целью сумматор 3 слагаемых, а та:кже сумматор 7 остатков могут быть построены на элементах И, ИЛИ, НЕ. При корректировании операции сложения используются следующие соотношения между прямыми и инверсными кодами операндов: , А и В - прямые п-разрядные коды слагаемых; А, В - инверсные ,1 -разрядные двоичные коды слагаемых CY 11.... . . ..1. Сложим почленно первое и второе уравнения (А + В) + + (А + В) 2Сп. Так как ..10 то, прибавив к левой и правой частям последнего равенства единицу, получим (А + В) + (А + В )- 1) С«, , где С,4.1 11 IO-I-L,I Отсуда следует. что А+В А+В+1. Указанное свойство используется для корректирования ошибок в контролируемом сумматоре. Ошибки, возникающие в сумматоре в результате неисправностей, вызваны неисправностью схемы формирования суммы или неисправностью схемы форми рования переносов. Неисправность, возникающая в схеме формирования i-ro разряда суммы, к одиночной ошибке типа 5( Si . Поскольку неисправности в сумматоре вызывают, асимметричные ошибки, то после подачи на входы сумматора инверсных значений слагаемых на всех его выходах установятся инверсные значения вектора суммы, при этом разряд суммы с ошибкой совпадает с инверсным значением суммы в этом разрядеJ X. е удовлетворяется зависимость Зтощ ST . После инверсии значения суммы на входе блока управляемых инверторов устанавливается скорректированный прямой код результата суммирования. Неисправность, возникающая в схе- ме формирования Переноса I, в зависимости от кода слагаемых может вызвать групповую ошибку в последующих разрядах. При этом Ci . Однако поскольку в сумматоре после подачина его входы инверсных значений слагаемых вектор переноса инвертируется, то удовлетворяется условие С-1ощ и , следовательно, осуществляется коррекция указанной ошибки и не происходит её распространения в стастаршие разряды. После инвертирования значения суммы на выходе устройства получаем скорректированный прямой код результата суммирования. Следует отметить, что кратность корректируемых ошибок в контролируемом сумматоре определяется обнаруживающей способностью остаточного кода и при модуле 1 3 равна единице. Устройство работает следующим образом. Слагаемые, с выходов регистров 1 и 2 поступают на соответствующие входы сумматора 3, а также на входы блоков 4,5 формирования остатка по модулю m. Соответствующие коды остатков с выходов блоков 4 и 5 Поступают на вход сумматора 7 остатков. Блоком 6 формирования остатка по мрдулю irn производится определение остатка по модулю m сумьял входных операндов. Схема 8 сравнения осуществляет сравнение кодов на выходах сумматора 7 и блока 6. При правильном функционировании сумматора 3 на выходе схемы 8 сравнения вьфабатьшается нулевой сигнал, по которому код суммы операндов с выхода сумматора 3 без изменения посту51111

пает через группу 9 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ на выход результата контролируемого сумматора.

В случае возникновения ошибки в векторе суммы эта ошибка обнаружи- 5 вается схемой 8 сравнения, на выходе которой формируется единичный сигнал. По этому сигналу осуществляется инвертирование операндов в регистрах 1 и 2 и операция суммирования над об- ратными кодами. Контроль правильности выполненной коррекции производится как и на рабочем такте, с помощью остаточного кода. Скорректированный результат суммирования обратных кодов5 слагаемых инвертируется элементами ИСГСПЮЧАЮЩЕЕ ИЛИ группы 9 и -поступает 676

на выход сумматора. Если коррекция-. произведена правильно, то через время задержки, равное одному такту, сиг -нал на выходе схемы 8 сравнения принимает нулевое значение, и на вход устройства поступают новые значения слагаемых.

В зависимости от значения сигнала на контрольном выходе устройства можно выделить следующие режимы его работы: постоянный нуль - ошибки в сумматоре отсутствуют; апериодическа я или периодическая последовательность нулей и единиц - в сумматоре возникают корректируемые ошибки; постоянная единица - в сумматоре произошла некорректируемая ошибка.

| название | год | авторы | номер документа |

|---|---|---|---|

| Контролируемое арифметическое устройство | 1982 |

|

SU1076906A1 |

| Устройство для контроля делительного блока | 1983 |

|

SU1115056A1 |

| Устройство для контроля на четность двоичной информации | 1981 |

|

SU1015388A1 |

| Устройство цифрового интегрирования | 1986 |

|

SU1345192A1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

| Контролируемый сумматор | 1983 |

|

SU1238073A1 |

| Устройство для контроля делителя по модулю | 1988 |

|

SU1566352A1 |

| Устройство для контроля последовательного сумматора | 1985 |

|

SU1264188A1 |

| Устройство для деления чисел | 1989 |

|

SU1711151A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СУММАТОРА, содержащее регистры первого и второго слагаемых, три блока формирования остатка по модулю |Y. , сумматор слагаемых, сумматор остатков, схему сравнения, причем информационные входы регистров первого и второго слагаемых являются соответственно входами первого и второго слагаемых устройства, выходы регистров первого и второго слагаемых соединены соответственно с первым и вторым информационными входами сумматора слагаемых и входами первого и второго блоков формирования остатка по модулю m , выходы которых соедийены соответстпенно с первым и вторым информацнояными входами сусумматора остатков, выходы которото соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами третьего блока формирования остатка по модулю т, входы которого соединены с выходами сумматора слагаемых, выход схемы сравнения является выходом ошибки устройства, отлиi чающееся тем, что, с целью повьш1ения достоверности контроля, в (Л него введена группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выходы сумма,тора слагаемых соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы,вторые входы которых объединены и соединены с выходом схемы сравнения, входом переноса сумматора слагаемых и управляющими входами регистров первого и второго слагаемых, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы являются выа ходами результата устройства.

.N

--V

8

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО С КОНТРОЛЕМ И КОРРЕКЦИЕЙ ОШИБОК | 0 |

|

SU387362A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| М.,Мир, с | |||

| Аппарат для электрической передачи изображений без проводов | 1920 |

|

SU144A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-08-30—Публикация

1983-04-25—Подача