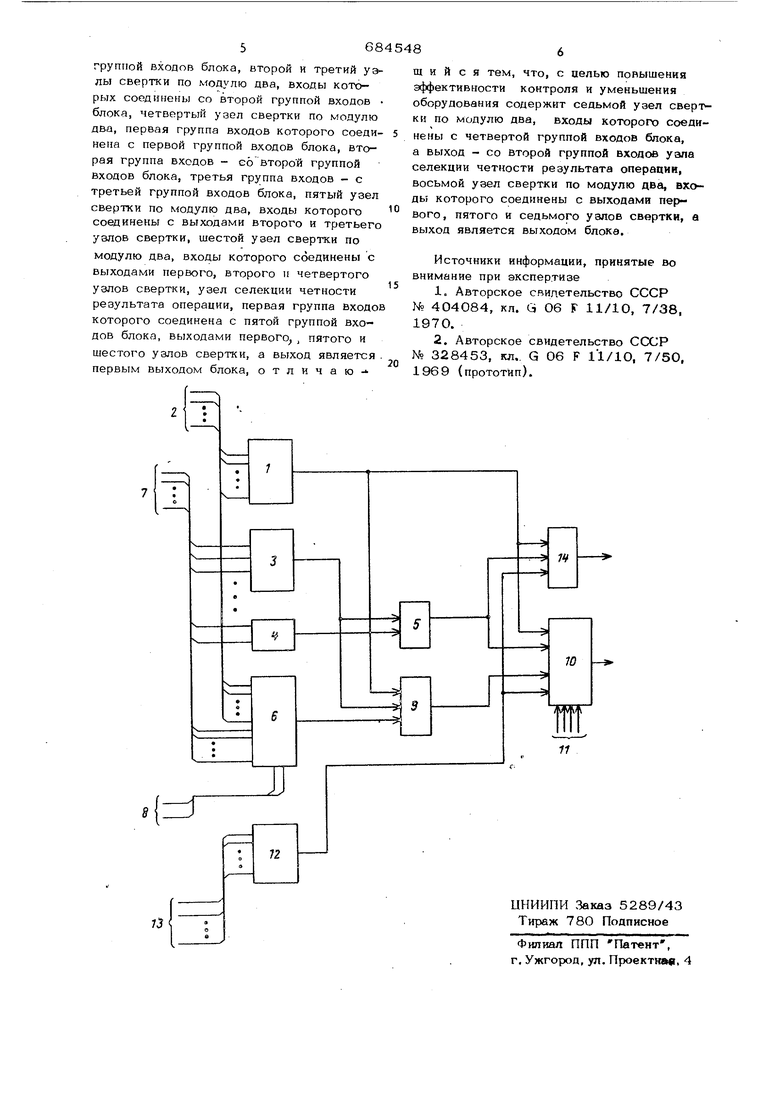

Иаобретение относится к области вычислительной техники и может быть ис- польвовано для контроля двоичных арифметико-логических устройств (АЛУ). Известно арифметическое устройство (АУ), позволяющее осуществить контроль суммирования путем предсказания четнос ти результата 1 . Однако блок контроля не содержит сх мы контроля логических операций. Наиболее близким к данному техническим решением является бяок предсказа ния четности, содержащий два регистра операндов, выходы которых соединены с входами сумматора и входами узлов свертки по модулю два четности результата, узел свертки по модулю два, вход KoToposjo соединен с выходом сумматора, и схему сравнения, входы которой подключены к выходам узла формирования четности результата и узла свертки по модулю деа, позволяющий обнаруживать 100% одиночных ошибок 2 . Однако предполагаемое наличие контрольных разря дов входных операндов может привести к увеличению оборудования блока контроля, кроме того не предусмотрена возможность обнаружения групповых ьшибок арифметико-логических операций. Целью изобретения является повышение эффективности и уменьшение оборудования контроля АЛУ. Поставленная цель достигается тем, что блок предсказания четности результата АЛУ содержит седьмой узел свертки по модулю два, входы которого соединены с четвертой группой входов блока, а выходсо второй группой входов узла селекции четности результата операции, восьмой узел свертки по модулю два, входы которого соединены с выходами первого, пятого и седьмого узлов свертки, а выход является выходом блока. Схема блока .предсказания четности результата АЛУ приведена на чертеже, причем для определенности формат обрабатываемой информации принят однобайтный, а сумматор АЛУ - параллельИс -последовотельный, состоящий из двух групп по четыре разряда в каждой. 1)Лок предсказания четности результата содержит узел .1. свертки по модулю два, первую 2 группу входов устройства, несущую функцию сумматора исключающее ИЛИ , узлы 3,4,5,6 свертки по модулю два вторую 7 группу входов устройства, несущую функцию сумматора И, третью 8 группу входов устройства, несущую сигналы входных переносов для групп сумматора, узел 9 свертки по модулю два, узел 10 селекции четности результата операции, пятую 11 группу Входов устройства, несущую признаки операций АЛУ, узел 12 свертки по модулю два; четвертую группу входов 13 устройства, несущую функцию сумматора ИЛИ, узел 14 свертки по модулю два. Ниже приведены все логические функции, реализуемые узлами блока предсказания четности результата АЛУ, причем нумерация индексов при буквенных обозначениях принята Возрастающей в направлении старших разрядов, т.е. разрядов с более высокими весовыми коэффициентами . Узел Н V- Hg V- HgV-H V- HS V , где Н ap,Vb - полусумма п -го разряда, а ,1 , Ь., - разрядные слагаемые FH - четность операции исключающее ИЛИ . Узел (4,vG2.(3sG6Vq7 где G- а Ьп. - функция И сумматора 1(параллельный перенос из п -го разряда). Увел 4 -Q V Gg, . узел S-PQ Pjv (), где Pj. - четность параллельных переносов в группах для всех разрядов, кроме старщих, F - четность операции И, Узел ечэ {Q, HP Н, + vCGg-HgR i-Q Н,) V-С (Н 4-Н Н W АхЛ/и , где Со, С4 - входные переносы соответ ственно в первую и вторую группы-1тетра ды) сумматора, Р - четность последовательных переносов в группах сумматоров. Узел 9-Pg РН PS где R .. - косвенно предсказываемая чет ность операции сложение. Узел. 12-fV Т V TV ТдУ ТдУ TgV .,. . , + Т V -I. где Tn ИЛИ. Рт - четность операции Увел 14 F РнУР V Рт О, Увел 14 -«-F PHV где F - функция сбоя АЛУ. Узел с1-Рс4)Э Рт + у (1 +& Fg , где сЧ,, /S ,J,d-- признаки операций соответственно И, ИЛИ, исключающие ИЛИ , сложение, Рр - предсказываемая четность результата. Блок предсказания четности результата АЛУ работает следующим образом. Узел 10 :Селекции результата выбирает формируемые в блоке предсказания четности в соответствии с выполняемой в АЛУ операцией.. Так, например, пусть в АЛУ выполняется операция И. Тогда выход узла 5 свертки по модулю два селекционируется на выход узла 10 под действием признака операции И. При этом любая одиночная ощибка при выполнении операции И в АЛУ будет обнаружена либо узлом 14 обнаружения групповых ошибок в работе сумматора, если она вызвана неисправностью ;хемь/ формирования И сумматора, либо посредством сравнения прелскавываемой четности операций И с непосредственно формируемой на выходе АЛУ четностью результата, если она вызвана неисправностью схемы селекции или регистра результата АЛУ, Аналогично формируются предсказываемые четности и органиауегся контроль при выполнении в АЛУ других операций. Здесь следует только отметить, что контроль за выполнением в АЛУ операции сложение фактически разделяется на два уровня: l) обнаружение групповых ошибок в работе сумматора с помощью узла 14; 2) обнаружение одинбчных ошибок путем сравнения формируемой и косвенно предсказываемой четностей суммы (косвенно предсказание четкости суммы производится с помощью функций, проверенных на первом уровне контроля). Итак, блок предсказания четности результата АЛУ позволяет организовать контроль арифметико-логического устройства без явного примене 1ия контрольных разрядов, что в свою очередь исключает использование специальных схем, форми Т ТТ1- Г7Т га/Мао НПО ТТОЯМ Д nT-itTf l Y OVOXX /К ПКХЫн рующих входные паритеты, осуществляет выявление некоторых групповых ошибок, что определяет повыщение эффективности контроля АЛУ в целом. Формула изобретения Блок предсказания четности результата арифметико-логического устройства, содержащий первый узел свертки по модулю два, входы которого соединены с первой

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1683016A1 |

| Устройство для деления | 1989 |

|

SU1667077A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Устройство для умножения | 1986 |

|

SU1368882A1 |

| Устройство для деления | 1989 |

|

SU1633395A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2021632C1 |

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| Параллельный сумматор с контролем по четности | 1977 |

|

SU739535A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1989 |

|

SU1656526A2 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

Авторы

Даты

1979-09-05—Публикация

1977-05-03—Подача