«

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики цифровых устройств с двумя и тремя устойчивыми состояниями.

Цель изобретения - повьшение бысродействия анализатора.

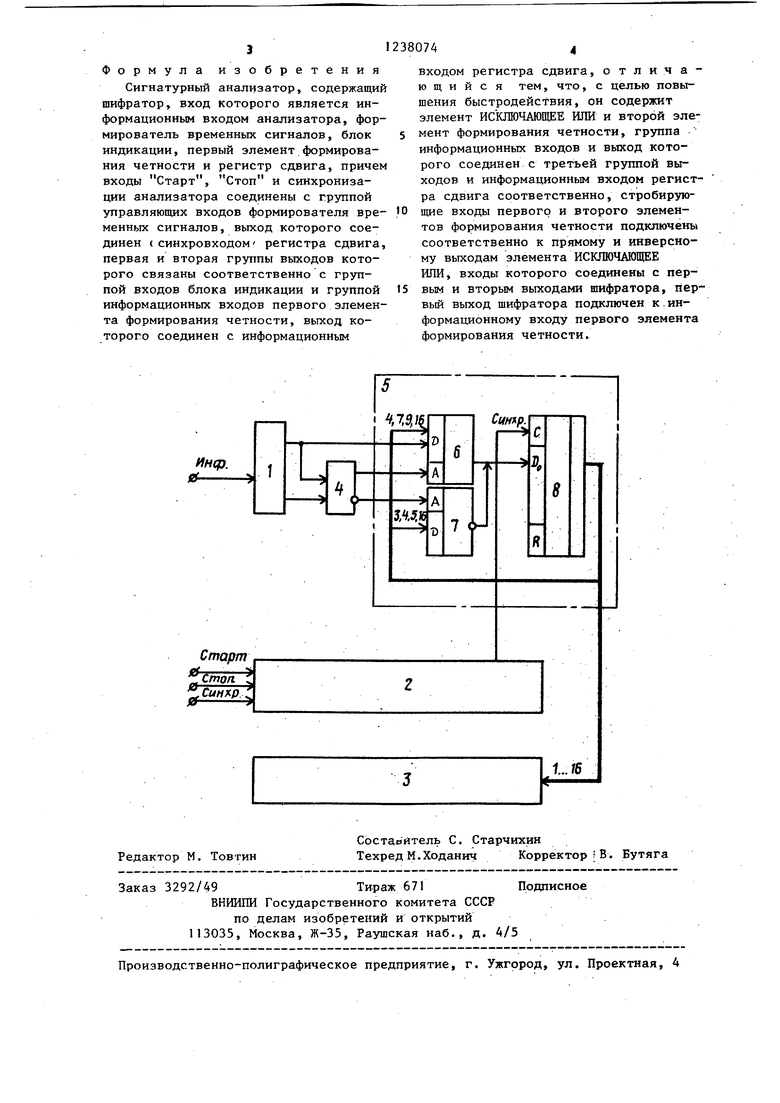

На чертеже приведена структурная схема сигнатурного анализатора для частного случая двух образующих по- линоМов шестнадцатой степени

. Ф (x) и . Ф(х).

Сигнатурный анализатор содержит шифратор 1, формирователь 2 временных сигналов, блок 3 индикации, элемент ИСКЛЮЧАЮЩЕЕ РШИ 4, формирователь 5 сигнатур, который в свою очередь содержит первый 6 и второй 7 элементы формирования четности и регистр 8 сдвига.

Элементы 6 и 7 формирования четности имеют управляющие входы А , .при подаче на которые сигнала О их работа разрешена, при подаче сигнала 1 - запрещена. Логика работы шифратора следующая:

Вход Выход 1 Выход 2 000

1

1

О 1

Группа информационных входов первого элемента 6 формирования четнос- ги соединена с выходами четвертого, седьмого, девятого и шестнадцатого разрядов регистра 8 сдвига, что соответствует образующему полиному

Ф,(х).

Группа информационных входов второго элемента 7 формирования четности соединена с выходами третьего, четвертого, пятого и шестнадцатого разрядов регистра 8 сдвига, что соответствует образующему полиному

Ф(х)х - +х -М .

Сигнатурный анализатор работает Следующим образом.

Информационная последовательность поступающая на вход шифратора 1 и состоящая из сигнала с тремя состояниями, преобразуете на выходах шифратора в двухбитовую последовательность . Формирователь 2 временных сигналов по управляющим сигналам Старт, Стоп и Синхр. формирует пачку синхроимпульсов в пределах ок380742

на измерения, определяемого сигналами Старт (начало окна) и Стоп (конец окна). Входная информационная последовательность синхронизирована

5 управляющим сигналом Синхр.. Если на информационном входе анализатора в данный момент присутствует сигнал О или 1, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 формируются сигна10 лы, разрешающие работу элемента 6 формирования четности и запрещающие ; работу элемента 7 формирования четности. В этом случае в младший разряд регистра 8 сдвига записывается

15 информация, являющаяся суммой по модулю два входной информации и информации с выходов разрядов регистра 8, определяемых первым образующим полиномом . Если же на информационном

20 входе анализатора присутствует сигнал с третьим состоянием, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 формируются сигналы, разрешающие работу элемента 7 формирования четности и

25 запрещающие работу элемента 6 формирования четности. В этом случае регистр 8 сдвига с обратйыми связями через элемент 7 формирования четности представляет собой генератор

30 псевдослучайной последовательности с вторым образующим полино - мом.

В процессе работы происходит по35 .следовательное переключение элемен- тов 6 и 7 формирования четности, причем результат, накопленный в регистре 8 сдвига до момента переключения, сохраняется и после переключения эле40 ментов 6 и, 7 генератор псевдослучайной последовательности продолжает работу с накопленного состояния. После прихода управляющего сигнала Стоп в регистре 8 сдвига фиксирует45 ся комплексная сигнатура, отражающая наличие и местоположение сигналов О, 1 и третьего состояния во входной информационной последовательности. Эта сигнатура отображается

50 блоком 3 индикации.

В предлагаемом анализаторе фиксация любого из трех возможных состояний входной информационной шины про- 55 исходит за один период внешнего синхросигнала, что обеспечивает повышенное быстродействие по сравнению с прототипом.

Формула изобретения

Сигнатурный анализатор, содержащий шифратор, вход которого является информационным входом анализатора, формирователь временных сигналов, блок индикации, первый элемент формирования четности и регистр сдвига, причем входы Старт, Стоп и синхронизации анализатора соединены с группой управляющих входов формирователя временных сигналов, выход которого соединен ( синхровходом регистра сдвига, первая и вторая группы выходов которого связаны соответственно с группой входов блока индикации и группой информационных входов первого элемента формирования четности, выход которого соединен с информационным

.

ГБ

Старт

Стоп.

а , Синхр

Редактор М. Товтин

Заказ 3292/49Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5

входом регистра сдвига, отличающийся тем, что, с целью повышения быстродействия, он содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и второй элемент формирования четности, группа информационных входов и выход которого соединен с третьей группой выходов и информационным входом регистра сдвига соответственно, стробирую- щие входы первого и второго элементов формирования четности подключены соответственно к прямому и инверсному выходам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого соединены с первым и вторым выходами шифратора, первый выход шифратора подключен к информационному входу первого элемента формирования четности.

5

Cuffxp.

1Ч.5.КСоставитель С. Старчихин

Техред М.Ходанич Корректоров. Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

| Сигнатурный анализатор | 1986 |

|

SU1361555A1 |

| Сигнатурный анализатор | 1985 |

|

SU1280635A1 |

| Сигнатурный анализатор | 1982 |

|

SU1108452A1 |

| Сигнатурный анализатор | 1984 |

|

SU1223231A1 |

| Сигнатурный анализатор | 1986 |

|

SU1343413A1 |

| Сигнатурный анализатор | 1982 |

|

SU1065857A1 |

| СИГНАТУРНЫЙ АНАЛИЗАТОР | 1991 |

|

RU2017209C1 |

| Сигнатурный анализатор | 1985 |

|

SU1367016A1 |

| Сигнатурный анализатор | 1989 |

|

SU1624455A1 |

Изобретение относится к вычислительной технике н может быть ис- ользовано для контроля и диагнос- ики цифровых устройств с двумя и тремя устойчивыми состояниями. Целью «зобретения является повьшение быстродействия анализатора. Сигнатурный анализатор содержит шифратор, формирователь временных, сигналов, блок индикации, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и формирователь сигнатур, который содержит первый и второй элементы формирования четности и регистр сдвига. Сущность функционирования андли- затора заключается в том, что в зависимости от того, присутствует ли на его входе бинарная информация или информация о третьем состоянии, осуществляется ее свертка по двум различным образующим номиналам. Полученная комплексная сигнатура отражает наличие и местоположение сигналов логического О, логической 1 и третьего состояния во .входной информационной последовательности. Фиксация любого из трех возможньпс состояний входной-информационной шш}ы происходит за один период внешнего синхросигнала, что обеспечивает повышенное быстродействие. I ил. § (Л to со 00 о 4ib

| Chan А., Easy to use signature analyzer accurately troublesheets complex logic circuits | |||

| - Hewlett Packard I., 1977, v | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| Раздвижной паровозный золотник со скользящими по его скалке поршнями и упорными для них шайбами | 1923 |

|

SU914A1 |

| , | |||

| . | |||

| Сигнатурный анализатор | 1980 |

|

SU903898A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-05-04—Подача