со

С

Изобретение относится к вычислительной технике и может быть использовано для технического диагностирования дискретных объектов.

Целью изобретения является увеличение достоверности контроля.

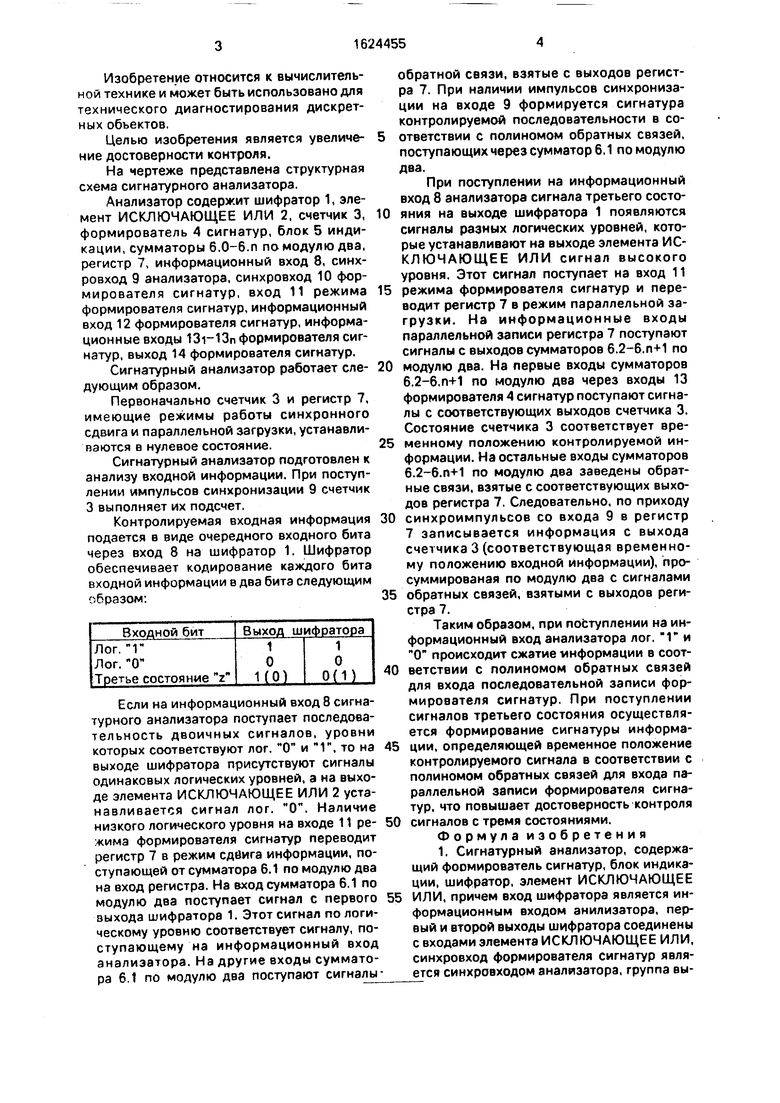

На чертеже представлена структурная схема сигнатурного анализатора.

Анализатор содержит шифратор 1, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2. счетчик 3, формирователь 4 сигнатур, блок 5 индикации, сумматоры 6.0-б.п по модулю два, регистр 7, информационный вход 8, синх- ровход 9 анализатора, синхровход 10 формирователя сигнатур, вход 11 режима формирователя сигнатур, информационный вход 12 формирователя сигнатур, информационные входы 13i-13n формирователя сигнатур, выход 14 формирователя сигнатур.

Сигнатурный анализатор работает следующим образом.

Первоначально счетчик 3 и регистр 7, имеющие режимы работы синхронного сдвига и параллельной загрузки, устанавливаются в нулевое состояние.

Сигнатурный анализатор подготовлен к анализу входной информации. При поступлении импульсов синхронизации 9 счетчик 3 выполняет их подсчет.

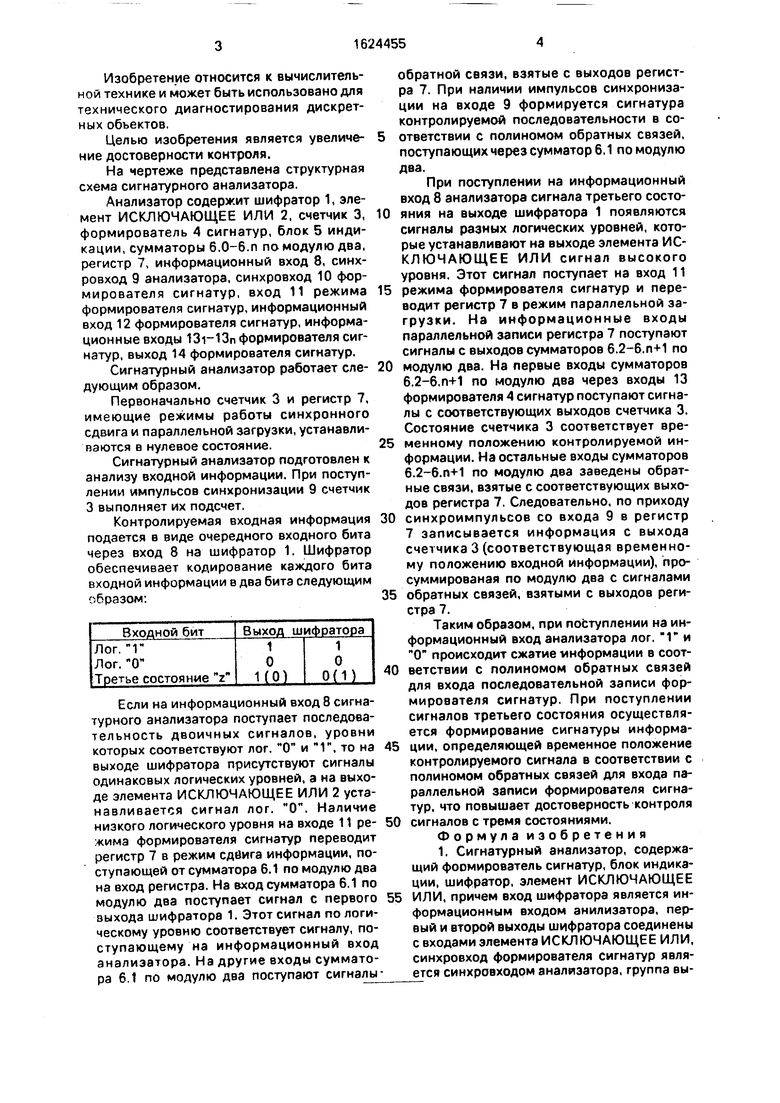

Контролируемая входная информация подается в виде очередного входного бита через вход 8 на шифратор 1. Шифратор обеспечивает кодирование каждого бита входной информации в два бита следующим образом:

Если на информационный вход 8 сигнатурного анализатора поступает последовательность двоичных сигналов, уровни которых соответствуют лог. О и Г, то на выходе шифратора присутствуют сигналы одинаковых логических уровней, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 устанавливается сигнал лог. О. Наличие низкого логического уровня на входе 11 режима формирователя сигнатур переводит регистр 7 в режим сдвига информации, поступающей от сумматора 6.1 по модулю два на вход регистра. На вход сумматора 6.1 по модулю два поступает сигнал с первого выхода шифратора 1. Этот сигнал по логическому уровню соответствует сигналу, поступающему на информационный вход анализатора. На другие входы сумматора 6.1 по модулю два поступают сигналы

обратной связи, взятые с выходов регистра 7. При наличии импульсов синхронизации на входе 9 формируется сигнатура контролируемой последовательности в соответствии с полиномом обратных связей, поступающих через сумматор 6.1 по модулю два.

При поступлении на информационный вход 8 анализатора сигнала третьего состо0 яния на выходе шифратора 1 появляются сигналы разных логических уровней, которые устанавливают на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ сигнал высокого уровня. Этот сигнал поступает на вход 11

5 режима формирователя сигнатур и переводит регистр 7 в режим параллельной загрузки. На информационные входы параллельной записи регистра 7 поступают сигналы с выходов сумматоров 6.2-6.П+1 по

0 модулю два. На первые входы сумматоров 6.2-6.п+1 по модулю два через входы 13 формирователя 4 сигнатур поступают сигналы с соответствующих выходов счетчика 3. Состояние счетчика 3 соответствует вре5 менному положению контролируемой информации. На остальные входы сумматоров 6.2-6.П+1 по модулю два заведены обратные связи, взятые с соответствующих выходов регистра 7. Следовательно, по приходу

0 синхроимпульсов со входа 9 в регистр 7 записывается информация с выхода счетчика 3 (соответствующая временному положению входной информации), про- суммированая по модулю два с сигналами

5 обратных связей, взятыми с выходов регистра 7.

Таким образом, при поступлении на информационный вход анализатора лог. 1 и О происходит сжатие информации в соот0 ветствии с полиномом обратных связей для входа последовательной записи формирователя сигнатур. При поступлении сигналов третьего состояния осуществляется формирование сигнатуры информа5 ции, определяющей временное положение контролируемого сигнала в соответствии с полиномом обратных связей для входа параллельной записи формирователя сигнатур, что повышает достоверность контроля

0 сигналов с тремя состояниями.

Формула изобретения 1. Сигнатурный анализатор, содержащий фоомирователь сигнатур, блок индикации, шифратор, элемент ИСКЛЮЧАЮЩЕЕ

5 ИЛИ, причем вход шифратора является информационным входом анилизатора, первый и второй выходы шифратора соединены с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, синхровход формирователя сигнатур является синхровходом анализатора, группа выходов формирователя сигнатур соединена с группой входов блока индикации, о т л и ч a root и и с я тем. что, с целью увеличения достоверности контроля, он содержит-счетчик, синхровход которого соединен с синх- ровходом анализатора, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом режима формирователя сигнатур, первый информационный вход которого соединен с первым выходом шифратора, 1-е разрядные выходы счетчика соединены с (1+1)-ми ин- формационными входами формирователя сигнатур, где I 1,п, n-разрядность сигнатуры.

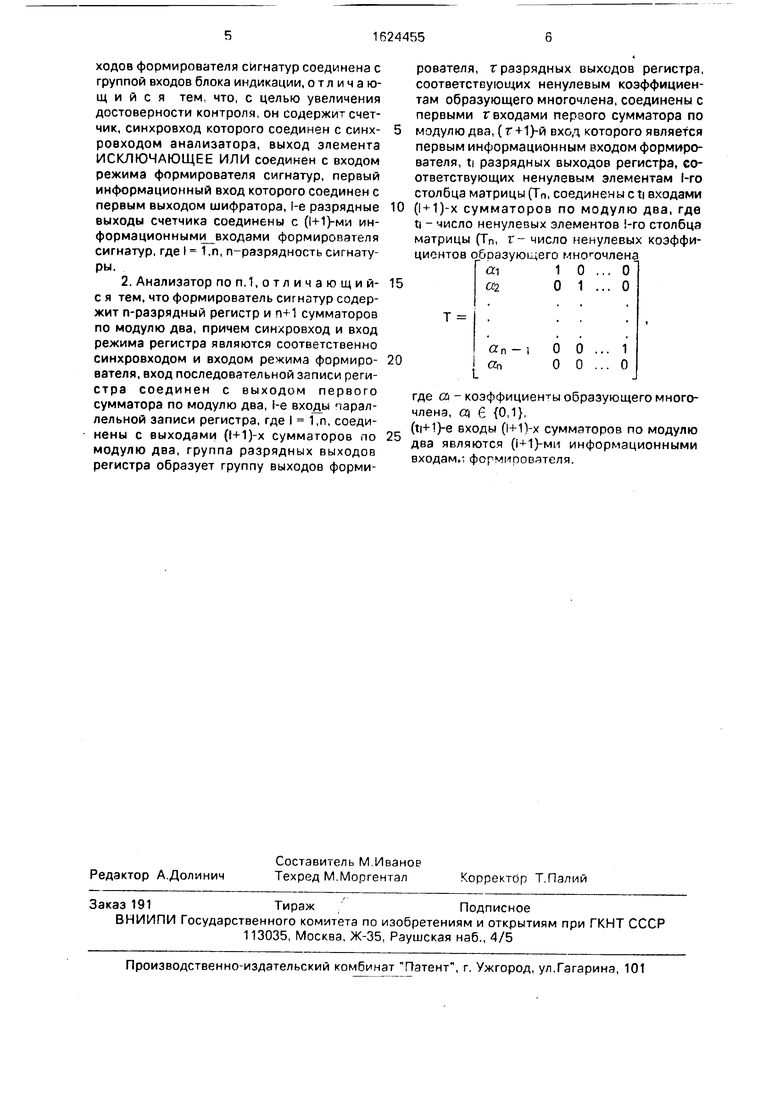

2. Анализатор по п.1, о т л и ч а ю щ и й- с я тем, что формирователь сигнатур содержит n-разрядный регистр и п+1 сумматоров по модулю два, причем синхровход и вход режима регистра являются соответственно синхровходом и входом режима формиро- вателя, вход последовательной записи регистра соединен с выходом первого сумматора по модулю два, 1-е входы параллельной записи регистра, где i 1,n, соединены с выходами (1+1)-х сумматоров по модулю два, группа разрядных выходов регистра образует группу выходов формирователя, г разрядных выходов регистра, соответствующих ненулевым коэффициентам образующего многочлена, соединены с первыми г входами первого сумматора по модулю два, (т+1}-й вход которого является первым информационным входом форми-ро- вателя, ti разрядных выходов регистра, соответствующих ненулевым элементам 1-го столбца матрицы (Тл, соединены с ti входами (1+1)-х сумматоров по модулю два, где ti - число ненулевых элементов 1-го столбца матрицы (Тп, г- число ненулевых коэффициентов образующего многочлена ai1 0 ... О

020 1 ... О

т

ал On

О О

о о

где а - коэффициенты образующего многочлена, а 6 {0,1},

(ti+1)-e входы (1+1 Vx сумматоров по модулю два являются (1+1)-ми информационными входами формиоовятеля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1987 |

|

SU1427370A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1795459A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Сигнатурный анализатор | 1985 |

|

SU1280635A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Сигнатурный анализатор | 1986 |

|

SU1472907A1 |

| Сигнатурный анализатор | 1990 |

|

SU1748154A1 |

| Сигнатурный анализатор | 1986 |

|

SU1383360A1 |

Изобретение относится к вычислительной технике и может использоваться в системах тестового диагностирования дискретных объектов. Цель изобретения-увеличение достоверности контроля. Анализатор содержит шифратор 1, элемент 2 ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик 3, формирователь 4 сигнатур, блок 5 индикации. Поставленная цель достигается за счет формирования сигнатуры, определяющей временное положение сигнала третьего состояния. 1 з.п. ф-лы, 1 ил.

| Сигнатурный анализатор | 1986 |

|

SU1361555A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

Авторы

Даты

1991-01-30—Публикация

1989-01-25—Подача