13

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля дискретных объектов.

Целью изобретения является упрощение анализатора.

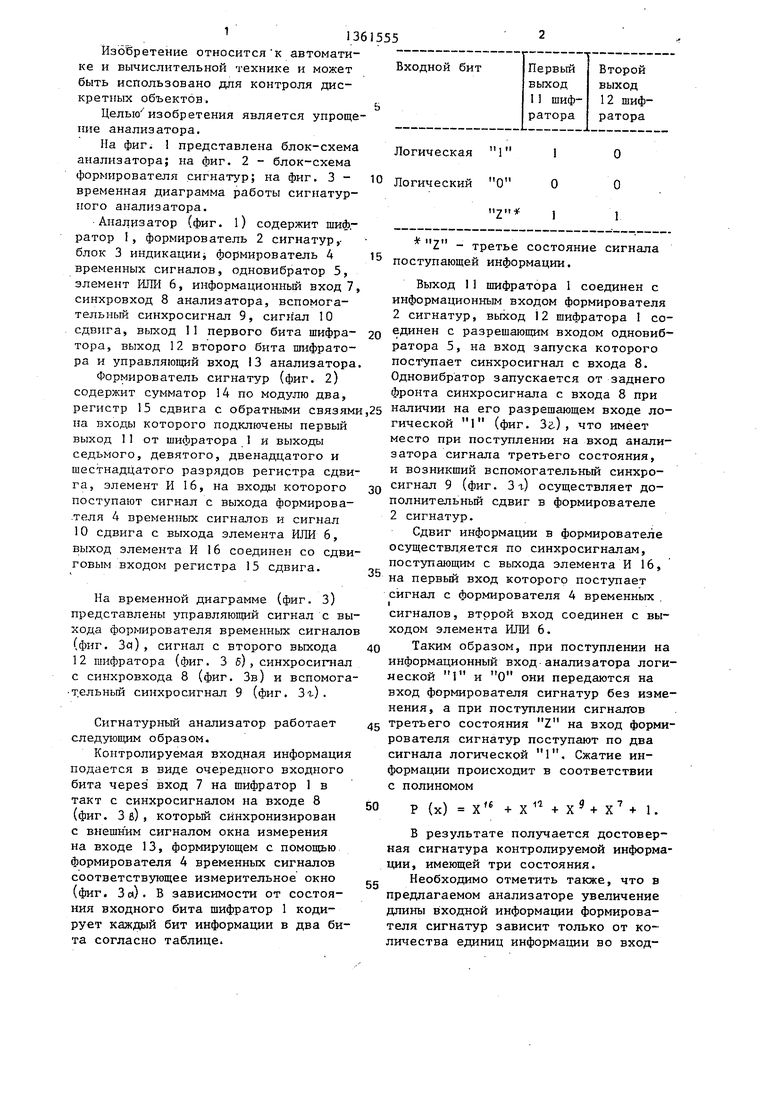

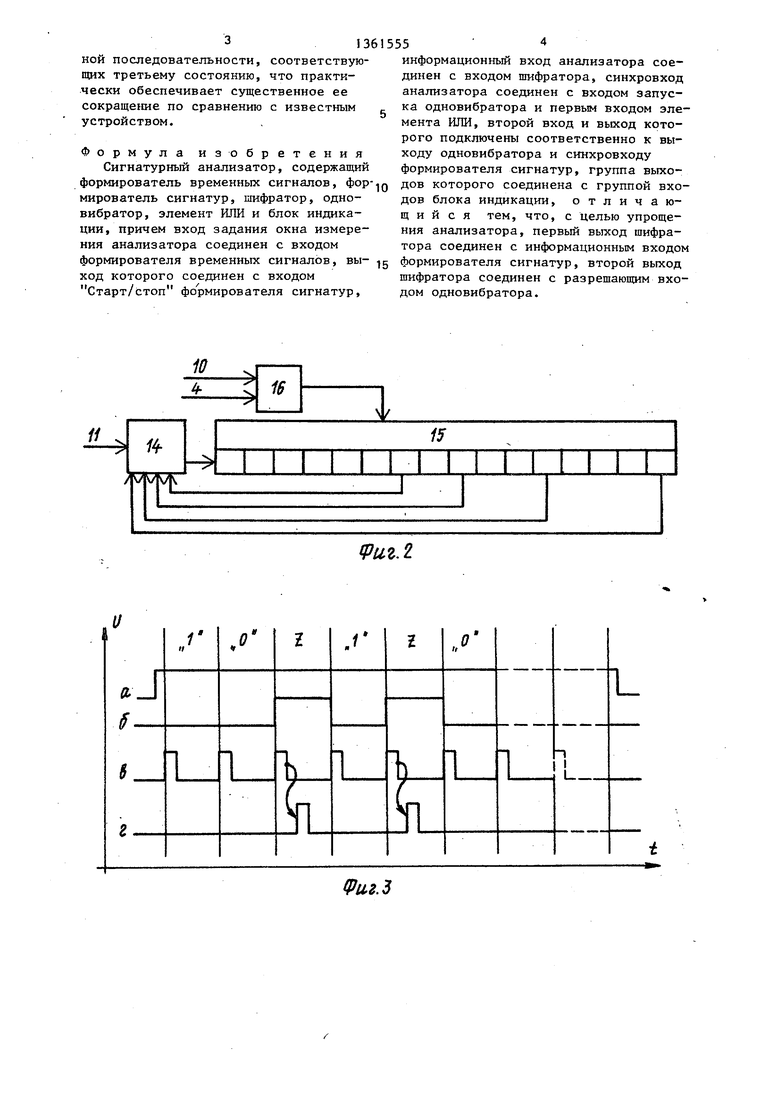

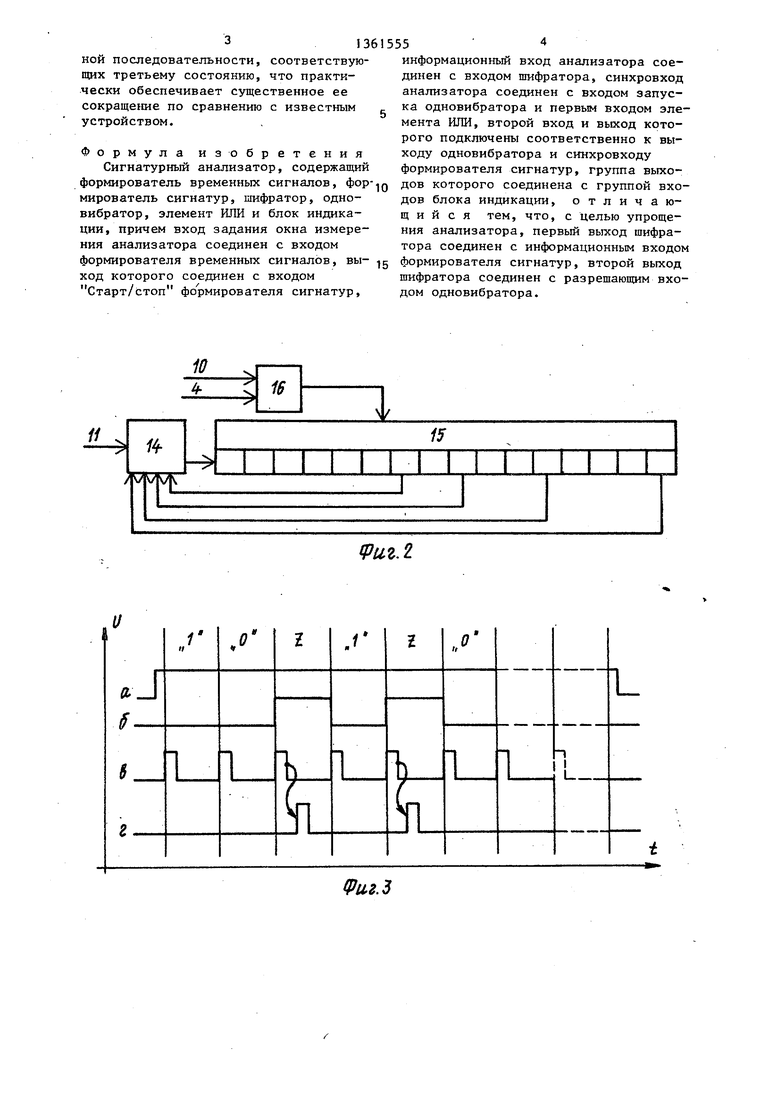

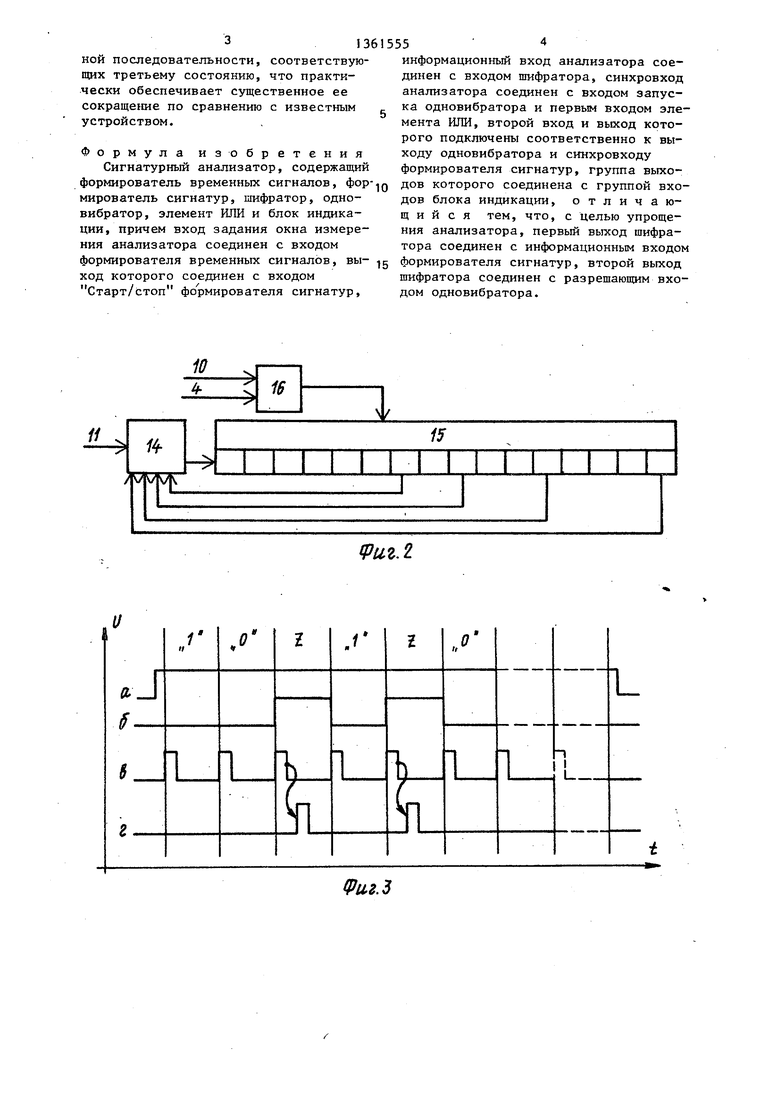

На фиг. представлена блок-схема анализатора; на фиг. 2 - блок-схема формирователя сигнатур; на фиг. 3 - временная диаграмма работы сигнатурного анализатора.

Анализатор (фиг. l) содержит шиф,- ратор 1, формирователь 2 сигнатур ,- блок 3 индикацииi формирователь 4 временных сигналов, одновибратор 5, элемент ИЛИ 6, информационньш вход 7, синхровход 8 анализатора, вспомогательный синхросигнал 9, сигйал 10 сдвига, выход I1 первого бита шифратора, выход 12 второго бита шифратора и управляющий вход 13 анализатора

Формирователь сигнатур (фиг. 2) содержит сумматор 14 по модулю два, регистр 15 сдвига с обратными связями на входы которого подключены первый выход 11 от шифратора 1 и выходы седьмого, девятого, двенадцатого и шестнадцатого разрядов регистра сдвига, элемент И 16, на входы которого поступают сигнал с выхода формирова- .теля 4 временных сигналов и сигнал 10 сдвига с выхода элемента ИЛИ 6, выход элемента И 16 соединен со сдвиговым входом регистра 15 сдвига.

На временной диаграмме (фиг. З) представлены управляющий сигнал с выхода формирователя временных сигналов (фиг. За), сигнал с второго выхода 12 шифратора (фиг. 3 б), синхросигнал с синхровхода 8 (фиг. Зв) и вспомога- т.ельный синхросигнал 9 (фиг. Зг) .

Сигнатурный анализатор работает следующим образом.

Контролируемая входная информация подается в виде очередного входного бита через вход 7 на шифратор 1 в такт с синхросигналом на входе 8 (фиг. 3 б), который синхронизирован с внешним сигналом окна измерения на входе 13, формирующем с помощью формирователя 4 временных сигналов соответствзпощее измерительное окно (фиг. 3ct). В зависимости от состояния входного бита шифратор 1 кодирует каждый бит информации в два бита согласно таблице.

1555

Z - третье состояние сигнала поступающей информации.

Выход 11 шифратора 1 соединен с информационным входом формирователя 2 сигнатур, выход J2 шифратора 1 соединен с разрешающим входом одновиб- ратора 5, на вход запуска которого поступает синхросигнал с входа 8. Одновибратор запускается от заднего фронта синхросигнала с входа 8 при

наличии на его разрешающем входе логической 1 (фиг. Зг), что имеет место при поступлении на вход анализатора сигнала третьего состояния, и возникший вспомогательный синхросигнал 9 (фиг. 3 г) осуществляет дополнительный сдвиг в формирователе 2 сигнатур.

Сдвиг информации в формирователе осуществляется по синхросигналам, поступающим с выхода элемента И 16,

на первый вход которого поступает

сигнал с формирователя 4 временных I

сигналов, второй вход соединен с выходом элемента ИЛИ 6.

Таким образом, при поступлении на информационный вход-анализатора логи- яеской 1 и О они передаются на вход формирователя сигнатур без изменения, а при поступлении сигналов

третьего состояния Z на вход формирователя сигнатур поступают по два сигнала логической 1. Сжатие информации происходит в соответствии с полиномом

50

55

Р (к) X + X + Х + Х + 1.

В результате получается достоверная сигнатура контролируемой информации, имеющей три состояния.

Необходимо отметить также, что в предлагаемом анализаторе увеличение длины входной информации формирователя сигнатур зависит только от количества единиц информации во входной последовательности, соответствующих третьему состоянию, что практически обеспечивает существенное ее сокраще1ше по сравнению с известным устройством.

Формула изобретения Сигнатурный анализатор, содержащий формирователь временных сигналов, формирователь сигнатур, шифратор, одно- вибратор, элемент ИЛИ и блок индикации, причем вход задания окна измерения анализатора соединен с входом формирователя временных сигналов, вы- ход которого соединен с входом Старт/стоп формирователя сигнатур.

информационный вход анализатора соединен с входом шифратора, синхровход анализатора соединен с входом запуска одновибратора и первым входом элемента ИЛИ, второй вход и выход которого подключены соответственно к выходу одновибратора и синхровходу формирователя сигнатур, группа выходов которого соединена с группой входов блока индикации, отличающийся тем, что, с целью упрощения анализатора, первый выход шифратора соединен с информационным входом формирователя сигнатур, второй выход шифратора соединен с разрешающим входом одновибратора.

Vuz. i

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1980 |

|

SU903898A1 |

| Сигнатурный анализатор | 1982 |

|

SU1108452A1 |

| Сигнатурный анализатор | 1984 |

|

SU1223231A1 |

| Сигнатурный анализатор | 1985 |

|

SU1297052A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624459A1 |

| Сигнатурный анализатор | 1982 |

|

SU1065857A1 |

| Сигнатурный анализатор | 1985 |

|

SU1298771A2 |

| Сигнатурный анализатор | 1989 |

|

SU1624455A1 |

| Сигнатурный анализатор | 1984 |

|

SU1354194A1 |

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля дискретных объектов. Целью изобретения является упрощение анализатора. Сигнатурный анализатор содержит шифратор 1, формирователь 2 сигнатур, блок 3 индикации, формирователь 4 временных сигналов., одновибратор 5, элемент ИЛИ 6. Алгоритм работы ана-- лизатора следующий: при поступлении на его информационный вход логической 1 или О они передаются на вход формирователя сигнатур без изменений, а при поступлении сигналов третьего состояния Z на вход формирователя сигнатур поступают по два сигнала логической 1. Упрощение конструкции по сравнению с прототипом заключается в отсутствии триггера и коммутатора. 3 ил., 1 табл. :оо 05 ел ел СП

| Электроника, 1977, № 5, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-05-30—Подача