канала 1-3, каждый из которых содержит регистры конфигурации 4, дайньк 5, ошибки 6, блок 7 управления, блок 8 сравнения, узлы сравнения

16,17, коммутаторы 20,26, мультиплексор 32, мажоритарный блок 33, группы 34,35,36 элементов И, элемент 37 ИЛИ. 1 з.п.ф-лы, 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для программного управления резервированными объектами и их диагностирования | 1989 |

|

SU1741295A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Устройство для контроля резервированной системы | 1984 |

|

SU1256028A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для обмена информацией | 1986 |

|

SU1322299A1 |

| Резервированное устройство для контроля и управления | 1991 |

|

SU1830535A1 |

| Интегрирующее устройство (его варианты) | 1982 |

|

SU1233147A1 |

Изобретение относится к области вычислительной техники и может быть i использовано в устройствах контроля и коммутации данных микропроцессорных систем с повышенной надежностью. Целью изобретения является повышение достоверности за счет мажоритарной обработки информации и контроля за напряжением. Устройство содержит три сл с

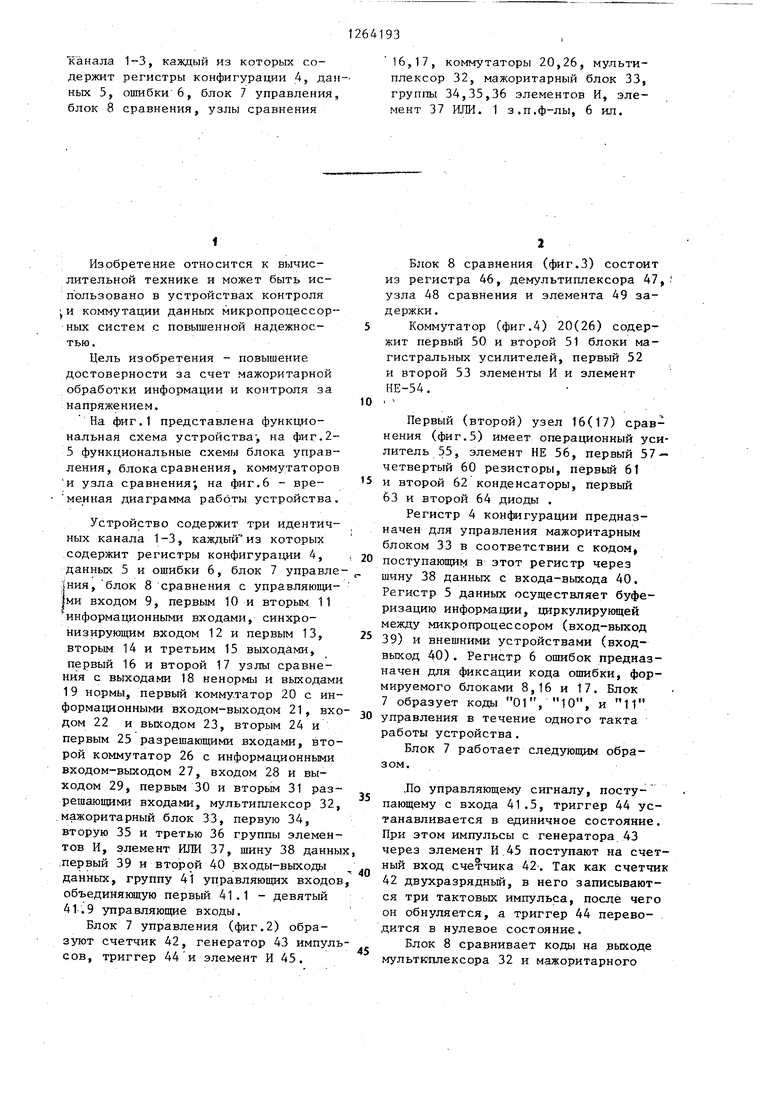

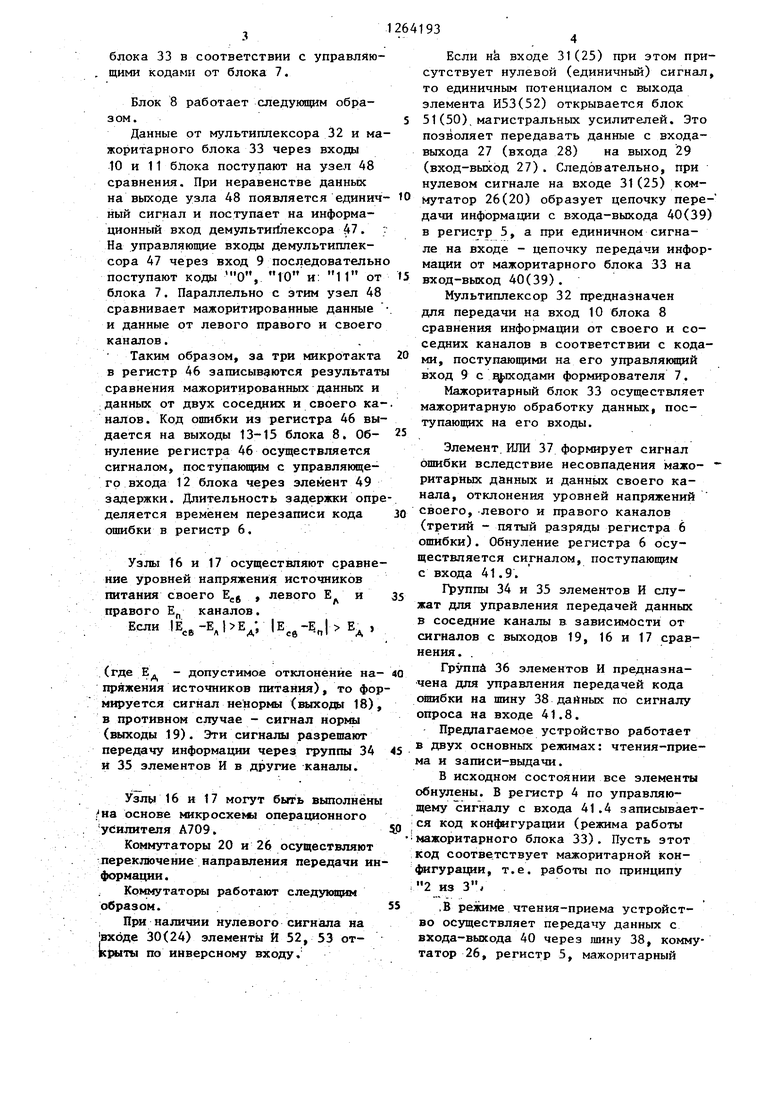

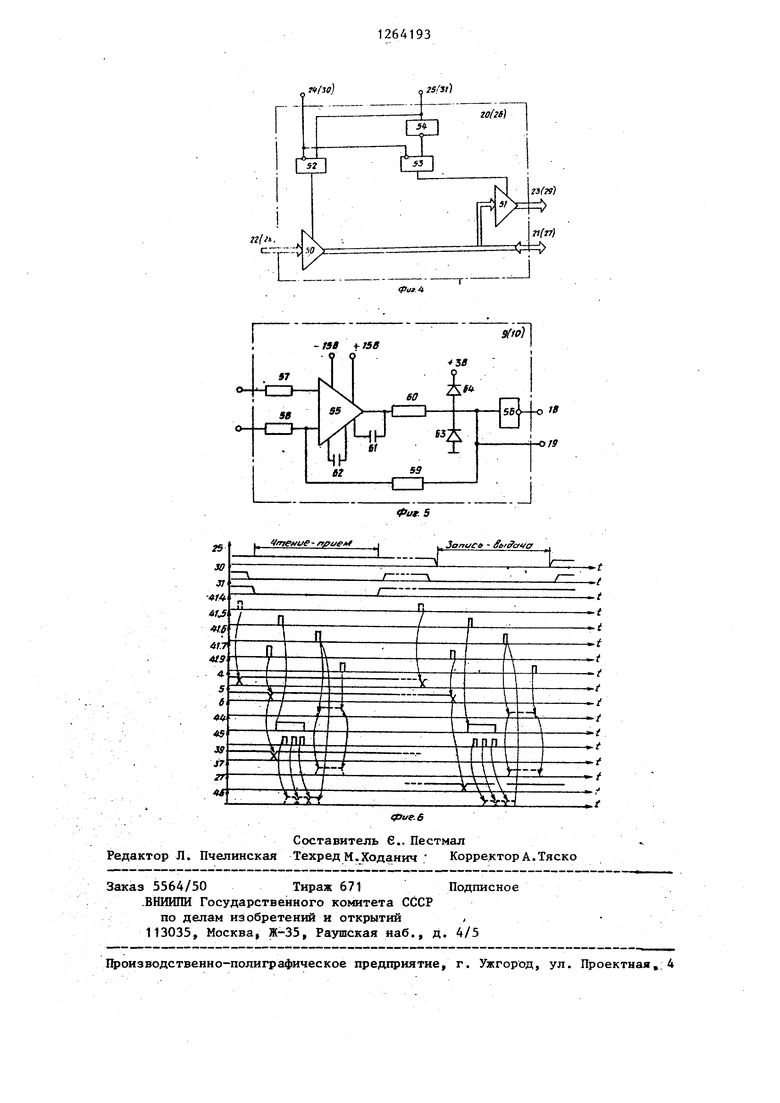

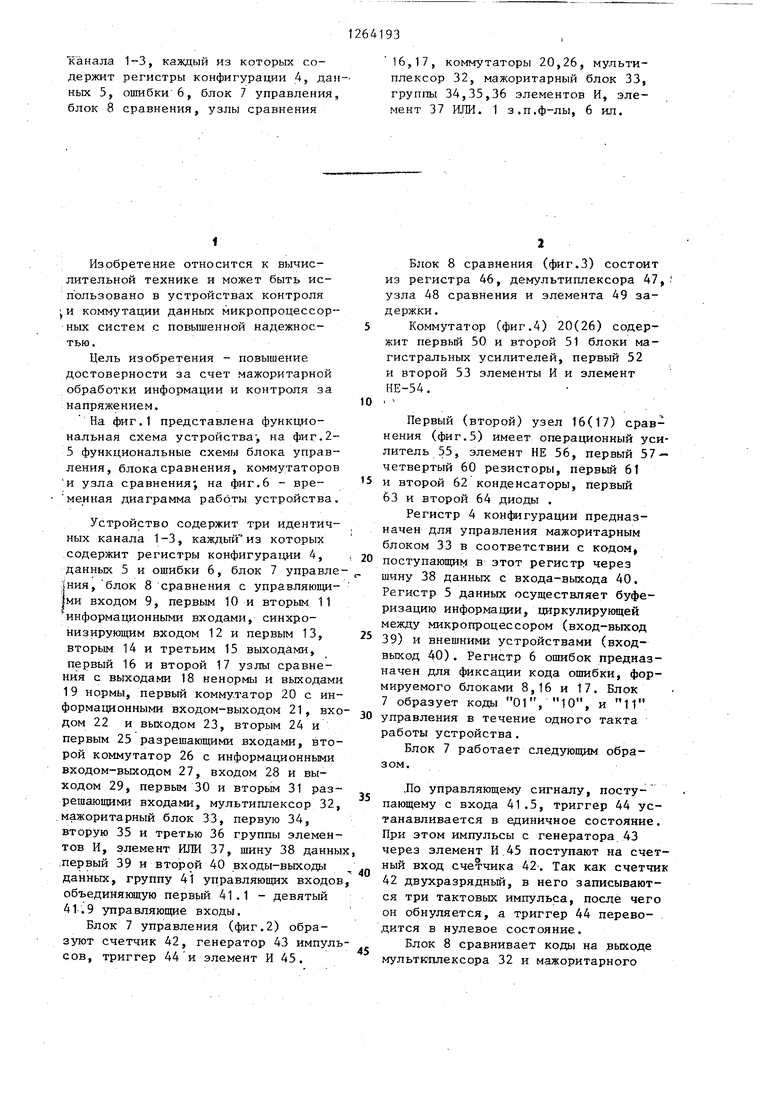

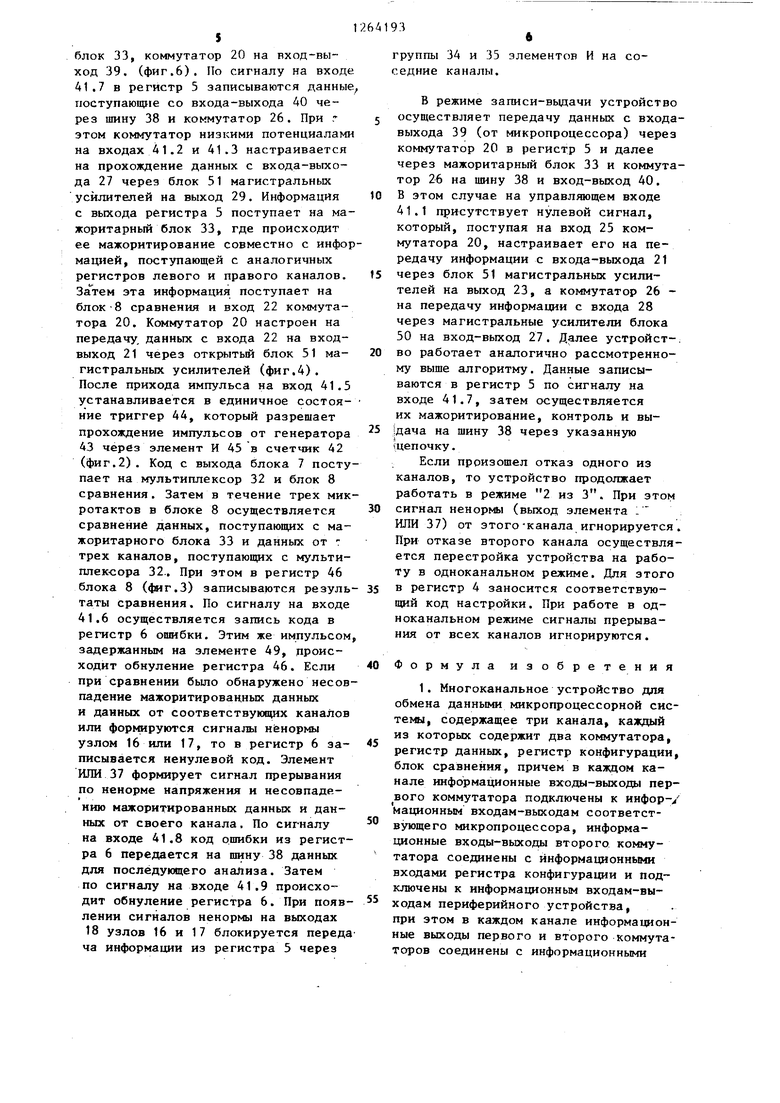

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля и коммутации данных микропроцессорных систем с повышенной надежностью . Цель изобретения - повышение достоверности за счет мажоритарной обработки информации и контроля за напряжением. На фиг.1 представлена функциональная схема устройства, на фиг.25 функциональные схемы блока управления, блока сравнения, коммутаторов и узла сравнения, на фиг.6 - временная диаграмма работы устройства. Устройство содержит три идентичных канала 1-3, каждый из которых содержит регистры конфигурации 4, данных 5 и ошибки 6, блок 7 управле ния, блок 8 сравнения с управляющими входом 9, первым 10 и вторым 11 информационными входами, синхронизирующим входом 12 и первым 13, вторым 14 и третьим 15 выходами, первый 16 и второй 17 узлы сравнения с выходами 18 ненормы и выходами 19 нормы, первый коммутатор 20 с ин формационными входом-выходом 21, вх дом 22 и выходом 23, вторым 24 и первым 25 разрешающими входами, вто рой коммутатор 26 с информационньми входом-выходом 27, входом 28 и выходом 29, первым 30 и вторым 31 разрешающими входами, мультиплексор 32 .мажоритарный блок 33, первую 34, вторую 35 и третью 36 группы элемен тов И, элемент ИЛИ 37, шину 38 данны :первый 39 и второй 40 входы-выходы данных, группу 41 управляюшзнх входо объединяющую первый 41.1 - девятый 41.9 управляющие входы. Блок 7 управления (фиг.2) образуют счетчик 42, генератор 43 импул сов, триггер 44и элемент И 45. Блок 8 сравнения (фиг.З) состоит из регистра 46, демультиплексора 47,; узла 48 сравнения и элемента 49 задержки. Коммутатор (фиг.4) 20(26) содержит первый 50 и второй 51 блоки магистральных усилителей, первый 52 и второй 53 элементы И и элемент НЕ-54. Первый (второй) узел 16(17) сравнения (фиг.5) имеет операционный усилитель 55, элемент НЕ 56, первый 57 - четвертый 60 резисторы, первый 61 и второй 62 конденсаторы, первый 63 и второй 64 диоды . Регистр 4 конфигурации предназначен для управления мажоритарным блоком 33 в соответствии с кодом, поступающим в этот регистр через шину 38 данных с входа-выхода 40. Регистр 5 данных осуществляет буферизацию информации, циркулирующей между микропроцессором (вход-выход 39) и внешними устройствами (входвыход 40). Регистр 6 ошибок предназначен для фиксации кода ошибки, формируемого блоками 8,16 и 17. Блок 7 образует коды 01, 10, и 11 управления в течение одного такта работы устройства. Блок 7 работает следующим образом. .По управляющему сигналу, поступающему с входа 41 .5, триггер 44 устанавливается в единичное состояние. При этом импульсы с генератора 43 через элемент И.45 поступают на счетный вход счетчика 42-. Так как счетчик 42 двухразрядньй, в него записываются три тактовых импульса, после чего он обнуляется, а триггер 44 переводится в нулевое состояние. Блок 8 сравнивает коды на выходе мультиплексора 32 и мажоритарного блока 33 в соответствии с управляю. щими кодами от блока 7. Блок 8 работает следующим образом. Данные от мультиплексора 32 и ма жоритарного блока 33 через входы 10 и 11 блока поступают на узел 48 сравнения. При неравенстве данных на выходе узла 48 появляется единич ный сигнал и поступает на информационный вход демультийлексора 47. На управляющие входы демультиплексора 47 через вход 9 последовательн поступают коды , 10 и: 11 от блока 7. Параллельно с этим узел 48 сравнивает мажоритированные данные и данные от левого правого и своего каналов.. Таким образом, за три микротакта в регистр 46 записываются результат сравнения мажоритированных данных и данных от двух соседних и своего ка налов. Код ошибки из регистра 46 вы дается на выходы 13-15 блока 8. Обнуление регистра 46 осуществляется сигналом, поступающим с управляющего входа 12 блока через элемент 49 задержки. Длительность задержки опр деляется временем перезаписи кода ошибки в регистр 6. Узлы 16 и 17 осуществляют сравне ние уровней напряжения источников левого Е. и питания своего Е, правого Е каналов. |Е.«-Е,, |ЕС., .(где Ед - допустимое отклонение на- пряжения источников питания), то фор мируется сигнал не нормы (выходы 18) в противном случае - сигнал нормы (выходы 19). Эти сигналы разрешают передачу информации через группы 34 и 35 элементов И в другие каналы. Узлы 16 и 17 могут быть выполнены |на осноне микросхе14 1 операционного усилителя А709. Коммутаторы 20 и 26 осуществляют переключение направления передачи ин формации. Коммутаторы работают следукицим образом. При наличии нулевого сигнала на входе 30(24) элементы И 52, 53 отKiMdTbi по инверсному входу, 193 Если Hk входе 31(25) при этом присутствует нулевой (единичный) сигнал, то единичным потенциалом с выхода элемента И53(52) открывается блок 51(50), магистральных усилителей. Это позволяет передавать данные с входавыхода 27 (входа 28) на выход 29 (вход-выход 27). Следовательно, при нулевом сигнале на входе 31(25) KCWмутатор 26(20) образует цепочку передачи информации с входа-выхода 40(39) в регистр 5, а при единичном сигнале на входе - цепочку передачи информации от мажоритарного блока 33 на вход-выход 40(39). Мультиплексор 32 предназначен для передачи на вход 10 блока 8 сравнения информации от своего и соседних каналов в соответствии с кодами, поступающими на его управлякяций вход 9 с Ч4 1ходами формирователя 7. Мажоритарный блок 33 осуществляет мажоритарную обработку данных, поступающих на его входы. Элемент. ИЛИ 37 формирует сигнал ошибки вследствие несовпадения мажо- ритарных данных и данных своего канала, отклонения уровней напряжений своего, -левого и правого каналов (третий - пятый разряды регистра 6 ошибки). Обнуление регистра 6 осуществляется сигналом, поступающим с входа 41.9. Группы 34 и 35 элементов И служат для управления передачей данных в соседние каналы в зависимости от сигналов с выходов 19, 16 и 17 сравнения. . ГРУППА 36 элементов И предназначена для управления передачей кода ошибки на шину 38 дайных по сигналу опроса на входе 41.8. Предлагаемое устройство работает в двух основных режимах: чтения-приеа и записи-выдачи. В исходном состоянии все элементы обнулены. В регистр 4 по управляющему сигналу с входа 41.4 записывается код конфигурации (режима работы мажоритарного блока 33). Пусть этот КОД соответствует мажоритарной кон4я1гурации, т.е. работы по принципу 2 из ,В режиме чтения-приема устройство осуществляет передачу данных с входа-выхода 40 через пмну 38, коммутатор 26, регистр 5, мажоритарный блок 33, коммутатор 20 на вход-выход 39. (фиг.6). По сигналу на входе 41.7 в регистр 5 записываются данные поступающие со входа-выхода 40 через шину 38 и коммутатор 26. При г этом коммутатор низкими потенциалами на входах 41.2 и 41.3 настраивается на прохождение данных с входа-выхода 27 через блок 51 магистральных усилителей на выход 29. Информация с выхода регистра 5 поступает на ма жоритарный блок 33, где происходит ее мажоритирование совместно с инфо мацией, поступающей с аналогичных регистров левого и правого каналов. Зачтем эта информация поступает на блок-8 сравнения и вход 22 коммутатора 20. Коммутатор 20 настроен на передачу, данных с входа 22 на входвыход 21 через открытый блок 51 магистральных усилителей (фиг.4). После прихода импульса на вход 41.5 устанавливается в единичное состояние триггер 44, который разрешает прохождение импульсов от генератора 43 через элемент И 45 в счетчик 42 (фиг.2). Код с выхода блока 7 посту пает на мультиплексор 32 и блок 8 сравнения. Затем в течение трех мик ротактов в блоке 8 осуществляется сравнение данных, поступающих с мажоритарного блока 33 и данных от : трех каналов, поступающих с мультиплексора 32., При этом в регистр 46 блока 8 (фиг.З) записываются резуль таты сравнения. По сигналу на входе 41.6 осуществляется запись кода в регистр 6 ошибки. Этим же импульсом задержанным на элементе 49, происходит обнуление регистра 46. Если при сравнении бьто обнаружено несов падение мажоритированных данных и данных от соответствующих каналов или форкируются сигналы нёнормы УЗЛОМ 16 или 17, то в регистр 6 записывается ненулевой код. Элемент ИЛИ 37 формирует сигнал прерывания по ненорме напряжения и несовпадению мажоритированных данных и данных от своего канала. По сигналу на входе 41.8 код ошибки из регист ра 6 передается на шину 38 данных для последующего анализа. Затем по сигналу на входе 41.9 происходит обнуление регистра 6. При появ лении сигналов ненормы на выходах 18 узлов 16 и 17 блокируется перед ча информации из регистра 5 через руппы 34 и 35 элементов И на соедние каналы. В режиме записи-выдачи устройство осуществляет передачу данных с входавыхода 39 (от микропроцессора) через коммутатор 20 в регистр 5 и далее через мажоритарный блок 33 и коммутатор 26 на шину 38 и вход-выход 40. В этом случае на управляющем входе 41.1 присутствует нулевой сигнал, который, поступая на вход 25 коммутатора 20, настраивает его на передачу информации с входа-выхода 21 через блок 51 магистральньпс усилителей на выход 23, а коммутатор 26 на передачу информации с входа 28 через магистральные усилители блока 50 на вход-выход 27. Далее устройство работает аналогично рассмотренному выше алгоритму. Данные записываются в регистр 5 по сигналу на входе 41.7, затем осуществляется их мажоритирование, контроль и вы|дача на шину 38 через указанную (цепочку. Если произошел отказ одного из каналов, то устройство продолжает работать в режиме 2 из 3. При этом сигнал ненормы (выход элемента . ИЛИ 37) от этого-канала игнорируется. При отказе второго канала осуществляется перестройка устройства на работу в одноканальном режиме. Для этого в регистр 4 заносится соответствующий код настройки. При работе в одноканальном режиме сигналы прерывания от всех каналов игнорируются. Формула изобретения 1. Многоканальное устройство для обмена данными микропроцессорной системы, содержащее три канала каждый из которых содержит два коммутатора, регистр данных, регистр конфигурации, блок сравнения, причем в каждом канале информационные входы-выходы первого коммутатора подключены к инфор-/ мационным входам-выходам соответствующего микропроцессора, информационные входы-выходы второго, коммутатора соединены с информационными входами регистра конфигурации и подключены к информационным входам-выходам периферийного устройства, при этом в каждом канале информационные выходы первого и второго коммутаторов соединены с информационными входами регистра данных, отличающееся тем, что, с целью повышения достоверности работы, в кахсцый из каналов введены блок упра ления, мультиплексор, регистр ошиб ки, мажоритарный блок, два узла сравнения, три группы элементов И, элемент ИЛИ, причем в каждом канале парвый управляющий Ьход первого ком мутатора, первый и второй управляющ входы второго коммутатора, вход установки блока управления, синхровхо ды регистра конфигурации, регистра ошибки, блока сравнения, регистра данных, вход сброса регистра ошибки, первые входы элементов И первой группы подключены к группе управ ляющих выходов микропроцессора, вы ходы элементов И группы и выход эле мента ИЛИ подключены к информационным входам периферийных устройств, при этом выходы элементов И второй и третьей групп образуют первую и вторую группы информационных выходов каждого канала соответственно, первые и вторые группы информационных входов мультиплексора и мажоритарного блока образуют первую и вторую группы информационных входов каждого канала, первые входы первого и второго узлов сравнения объединены и подключены к шине питания своего канала, вторые входа первого и второго узлов сравнения j подключены к шинам питания соседних I каналов, при этом в каждом канале группа информационных выходов регистра данных соединена с первыми входами элементов И второй и третье групп и третьими группами информационньк входов мультиплексора и мажоритарного блока, группа стробирую щих входов которого соединена с гру пой выходов регистра конфигурации, группа информационных выходов мажоритарного блока соединена с группам информационных входов первого и вто |рого коммутаторов и с первой группой информационных входов Ьлока сравнения, вторая группа информационных входов которого соединена с группой информационных выходов мультиплексора, группа управляющих входов которого соединена с группой выходов блока управления и третьей группой информационных входов блока сравнения, группа информационных выходов которого соединена с группой информационных входов регистра ошибок, первый, второй, третий, чет ертый и пятый выходы которого соединены с вторыми входами элементов И первой группы, первый, второй и третий входы элемента ИЛИ соединены с третьим, четвертым и пятым выходами регистра ошибок, четвертый и пятый информационные входы которого соединены с выходами несравнения первого и второго узлов сравнения соответственно, выходы сравнения которых соединены с вторыми входами элементов И второй и третьей групп соответственно, причем первая группа информационных выходов первого канала соединена с первой группой информационных входов третьего канала, вторая группа информационных входов которого соединена со второй группой информационных выходов второго канала, первая группа информационньк выходов которого соединена с первой группой информационных входов первого канала, вторая группа информационных входов которого соединена с второй группой информационных выходов третьего канала, первая группа информационных выходов которого соединена с второй группой информационных входов второго канала, первая группа информационных выходов которого соединена с второй группой информационных входов первого канала, причем в каждом канале второй разрешающий вход первого коммутатора подключен к шине нулевого потенциала устройства, а первые входы nepBdro и второго узлов сравнеия подключены к шине единичного отенциала канала. 2. Устройство по П.1, отличающееся тем, что блок управления содержит триггер, счетчик, генератор импульсов и элемент И, причем единичный вход триггера является входом установки блока управления, группа разрядных выходов счетчик|1. образует группу выходов блока управления, при этом в блоке управления выход триггера соединен с первьы входом элемента И,. второй вход которых соединен с выходом генератора импульсов, а выход - со счетным входом счетчика, выход переполнения которого, соединен с нулевым входом триггера.

фие.2

.

effve.3

г

Sf3ll

| Микропрограммное устройство управления | 1981 |

|

SU1015383A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропроцессорные комплексы БИС .на основе интегральной инжекционной логики (Под ред | |||

| Э.М | |||

| Калошкина H.I Радио и связь,М984, с.58-61, рис.2.30. | |||

Авторы

Даты

1986-10-15—Публикация

1985-04-22—Подача