I

Изобретение относится к вычислительной технике, предназначено для вывода информаоди из ЭВМ и может использоваться в системах автоматизации проектирования и конструирования, при автоматизированной обработке дан- ньпс, в диалоговых системах.

Цель изобретения - повышение быстродействия устройства.

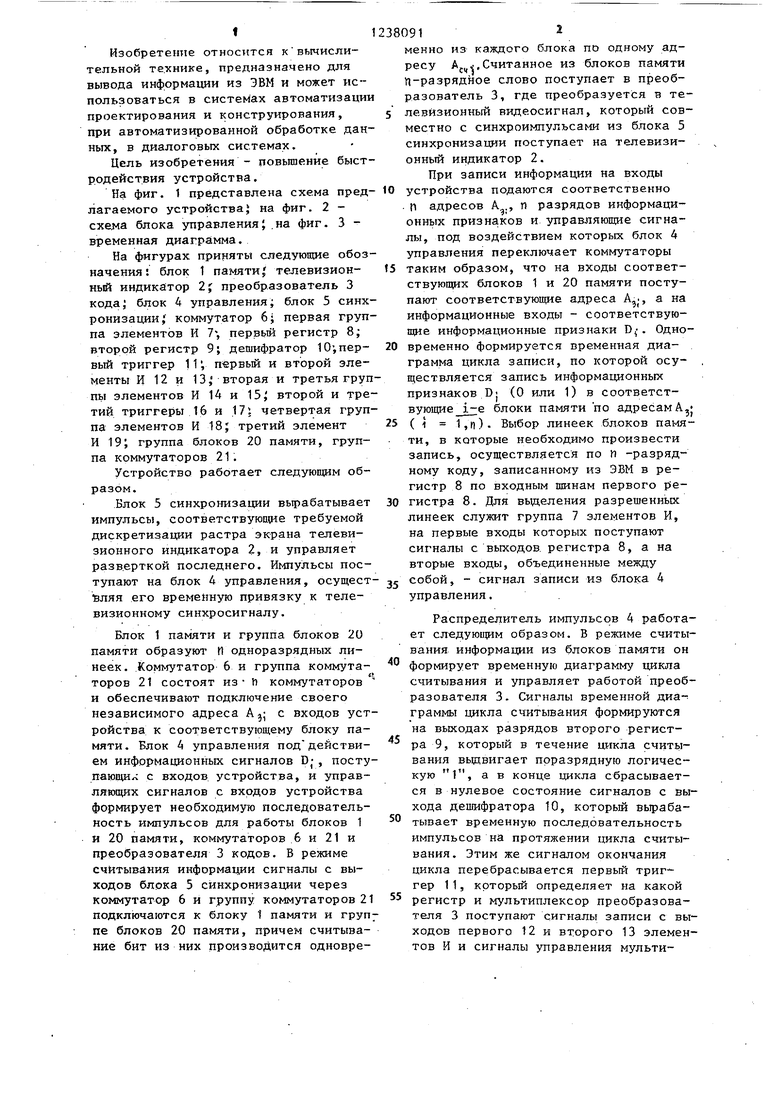

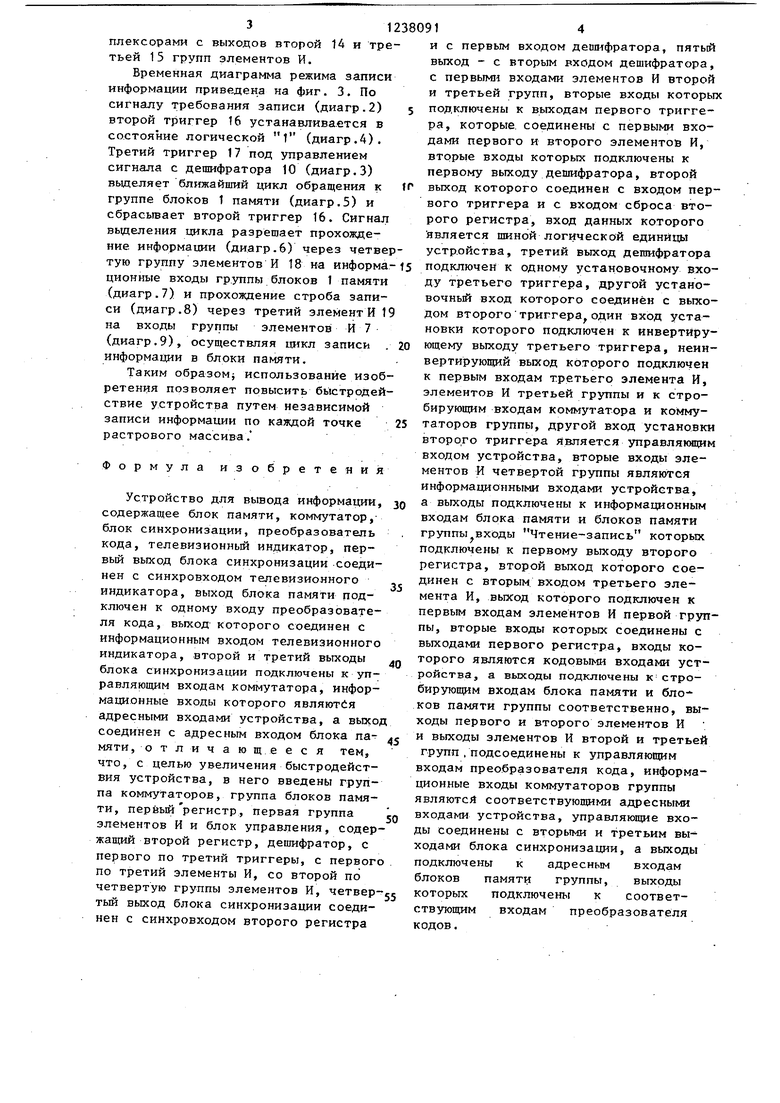

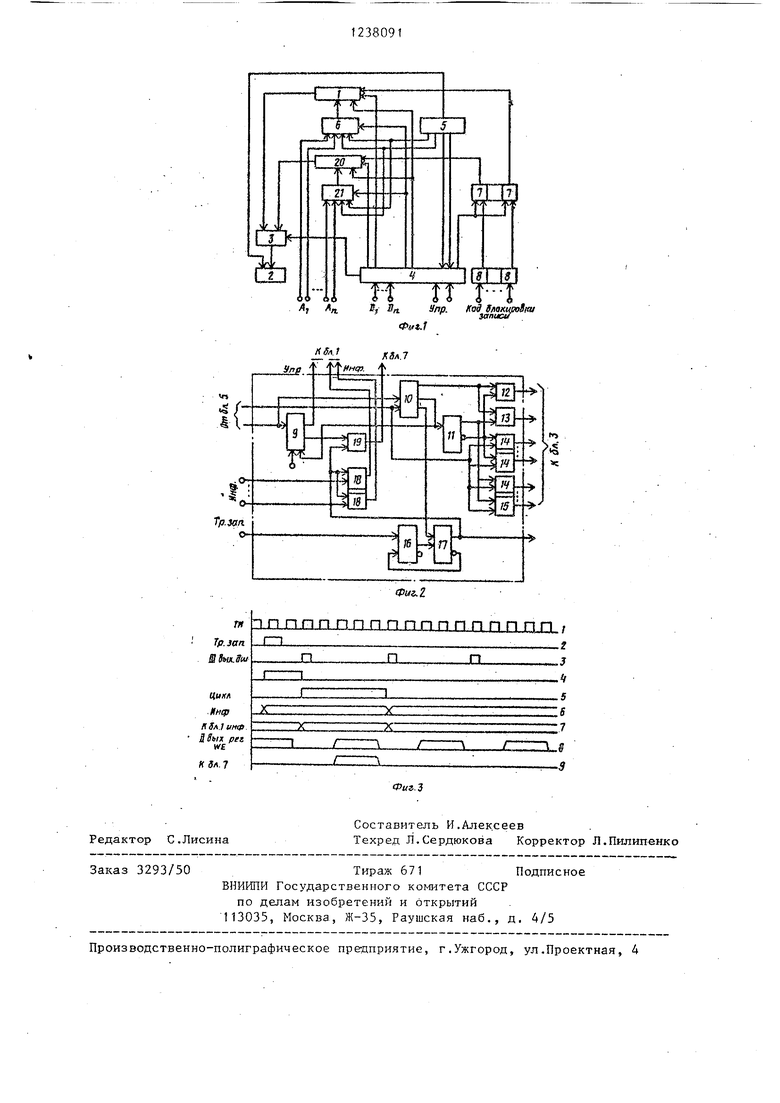

На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 - схема блока управления;,на фиг. 3 - временная диаграмма.

На фигурах приняты следующие обозначения: блок 1 памяти, телевизионный индикатор 2j преобразователь 3 кода; блок 4 управления; блок 5 синхронизации; коммутатор 6; первая группа элементов И 7, первый регистр 8; второй регистр 9; дешифратор 10,первый триггер 11, п«рвьй и второй элементы И 12 и 13 вторая и третья группы элементов И 14 и 15; второй и третий триггеры 16 и 17: четвертая группа элементов И 18; третий элемент И 19; группа блоков 20 памяти, группа коммутаторов 21.

Устройство работает следующим образом.

Блок 5 синхронизации вырабатывает импульсы, соответствуюЕ е требуемой дискретизации растра экрана телевизионного индикатора 2, и управляет разв.ерткой последнего. Импульсы поступают на блок 4 управления, осущест- впяя его временную привязку к телевизионному синхросигналу.

Блок 1 памяти и группа блоков 20 памяти образуют П одноразрядных линеек. Коммутатор 6 и группа коммутаторов 21 состоят из- и коммутаторов и обеспечивают подключение своего независимого адреса с входов устройства к соответствующему блоку памяти. Блок 4 управления под действием информационных сигналов D;, посту- паюгцих с входов устройства, и управляющих сигналов с входов устройства формирует необходимую последовательность Импульсов для работы блоков 1 и 20 памяти, коммутаторов 6 и 21 и преобразователя 3 кодов. В режиме считывания информации сигналы с выходов блока 5 синхронизации через коммутатор 6 и группу коммутаторов 21 подключаются к блоку 1 памяти и груп пе блоков 20 памяти, причем считывание бит VI3 них производится одновре380912

менно из каждого блока по одному адресу ,Считанное из блоков памяти П-разрядное слово поступает в преобразователь 3, где преобразуется в те5 левйзионный видеосигнал, который совместно с синхроимпульсами из блока 5 синхронизации поступает на телевизи- oHHbrfi индикатор 2.

При записи информации на входы

0 устройства подаются соответственно . (1 адресов А , п разрядов информационных признаков и управляющие сигналы, под воздействием которьпх блок 4 управления переключает коммутаторы

5 таким образом, что на входы соответствующих блоков 1 и 20 памяти поступают соответствующие адреса , а на информационные входы - соответствующие информационные признаки D{. Одно0 временно формируется временная диаграмма цикла записи, по которой осуществляется запись информационных признаков DJ (О или 1) в соответст- вующие гзе блоки памяти по адресамА 5 (i 1,п). Выбор линеек блоков памя ти, в которые необходимо произвести запись, осуществляется по и -разрядному коду, записанному из ЭВМ в регистр 8 по входным шинам первого ре0 гистра 8. Для вьщеления разрешенных линеек служит группа 7 элементов И, на первые входы которых поступают сигналы с выходов, регистра 8, а на вторые входы, объединенные между

5 собой, - сигнал записи из блока 4 управления. .

Распределитель импульсов 4 работает следующим образом. В режиме считывания информации из блоков памяти он

формирует временную диаграмму цикла считывания и управляет работой преобразователя 3. Сигналы временной диаграммы цикла считьгоания формируются на выходах разрядов второго регистра 9, который в течение цикла считывания вьщвигает поразрядную логическую 1, а в конце цикла сбрасывается в нулевое состояние сигналов с выхода дешифратора 10, который выраба5 тывает временную последовательность импульсов на протяжении цикла считывания. Этим же сигналом окончания цикла перебрасывается первый триг- гер 11, который определяет на какой

55 регистр и мультиплексор преобразователя 3 поступают сигналы записи с выходов первого 12 и второго 13 элементов И и сигналы управления мультиплексорами с выходов второй 14 и третьей 15 групп элементов И.

Временная диаграмма режима записи информации приведена на фиг. 3. По сигналу требования записи (диагр.2) второй триггер 16 устанавливается в состояние логической 1 (диагр.4). Третий триггер 17 под управлением сигнала с дешифратора 10 (диагр.З) выделяет ближайший цикл обращения к группе блоков 1 памяти (диагр.5) и сбрасьгеает второй триггер 16. Сигнал вьщеления цикла разрешает прохождение информации (диагр.6) через четветую группу элементов И 18 на информа ционные входы гр.уппы блоков 1 памяти (диагр.7) и прохождение строба записи (диагр.8) через третий элемент И 1 на входы группы элементов И 7 (диагр,9), осуществляя цикл записи . информации в блоки памяти.

Таким образом; использование изобретения позволяет повысить быстродействие устройства путем независимой записи информации по каждой точке растрового массива.

Формула изобретения

Устройство для вывода информации, содержащее блок памяти, коммутатор,- блок синхронизации, преобразователь кода, телевизионный индикатор, пер- вьй выход блока синхронизации соединен с синхровходом телевизионного индикатора, выход блока памяти подключен к одному входу преобразователя кода, выход которого соединен с информационным входом телевизионного индикатора, второй и третий выходы блока синхронизации подключены к управляющим входам коммутатора, информационные входы которого являются адресными входами устройства, а вьпсод соединен с адресным входом блока па- мяти, отличающееся тем, что, с целью увеличения быстродействия устройства, в него введены группа коммутаторов, группа блоков памяти, перйый регистр, первая группа элементов И и блок управления, содержащий второй регистр, дешифратор, с первого по третий триггеры, с первого по третий элементы И, со второй пс четвертую группы элементов И, четвертый выход блока синхронизации соединен с синхровходом второго регистра

5ff 1520

25

зо р п r

5

и с первым входом депптфратора, пятый выход - с вторым входом дешифратора, с первыми входами элементов И второй и третьей групп, вторые входы которых подключены к выходам первого триггера, которые, соединены с первыми входами первого и второго элементов И, вторые входы которых подключены к первому выходу дешифратора, второй выход которого соединен с входом первого триггера и с входом сброса второго регистра, вход данных которого является шиной логической единицы устройства, третий выход дешифратора подключен к одному установочному входу третьего триггера, другой установочный вход которого соединён с выходом второго триггера один вход установки которого подключен к инвертирующему выходу третьего триггера, неинвертирующий выход которого подключен к первым входам третьего элемента И, элементов И третьей группы и к стро- бирующим входам коммутатора и коммутаторов группы, другой вход установки второго триггера является управляющим входом устройства, вторые входы элементов И четвертой группы являются информационными входами устройства, а выходы подключены к информационным входам блока памяти и блоков памяти группы входы Чтение-запись которых подключены к первому выходу второго регистра, второй выход которого соединен с вторым входом третьего элемента И, выход которого подключен к первым входам элементов И первой rpjm- пы, вторые входы которых соединены с выходами первого регистра, входы которого являются кодовыми входами устройства, а выходы подключены к- стро- бирующим входам блока памяти и блоков памяти группы соответственно, выходы первого и второго элементов И и выходы элементов И второй и третьей групп .подсоединены к управляющим входам преобразователя кода, информационные входы коммутаторов группы являются соответствующими адресными входами устройства, управляющие входы соединены с вторыми и третьим вы- ходами блока синхронизации, а выходы подключены к адресным входам блоков памяти группы, выходы которых подключены к соответствующим входам преобразователя кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| Устройство для отображения графической информации на телевизионном индикаторе | 1986 |

|

SU1374272A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1403091A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1339625A1 |

Изобретение относится к области вычислительной техники. Целью изобретения является повьппение быстродействия за счет записи массива изображения в блок памяти путем одновременной записи нескольких точек изображения, расположенных по разным адресам. Цель достигается введением в устройство группы блоков памяти и коммутатор ов. 3 ил.

| Устройство для отображения информации | 1975 |

|

SU543960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для предотвращения ошибок в системах передачи данных | 1979 |

|

SU930335A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-11-10—Подача