Изобретение относится к преобразовательной технике и может быть использовано для управления преобразователями с широтно-импульсной модуляцией (ШИМ) выходного напряжения.

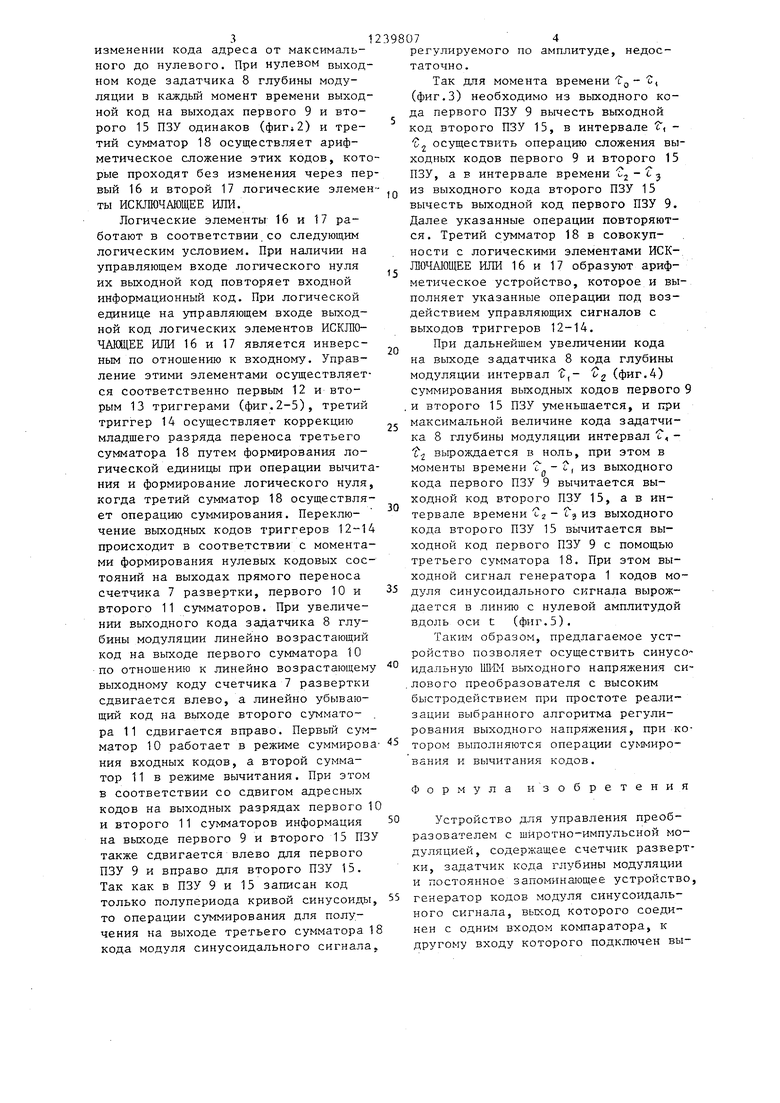

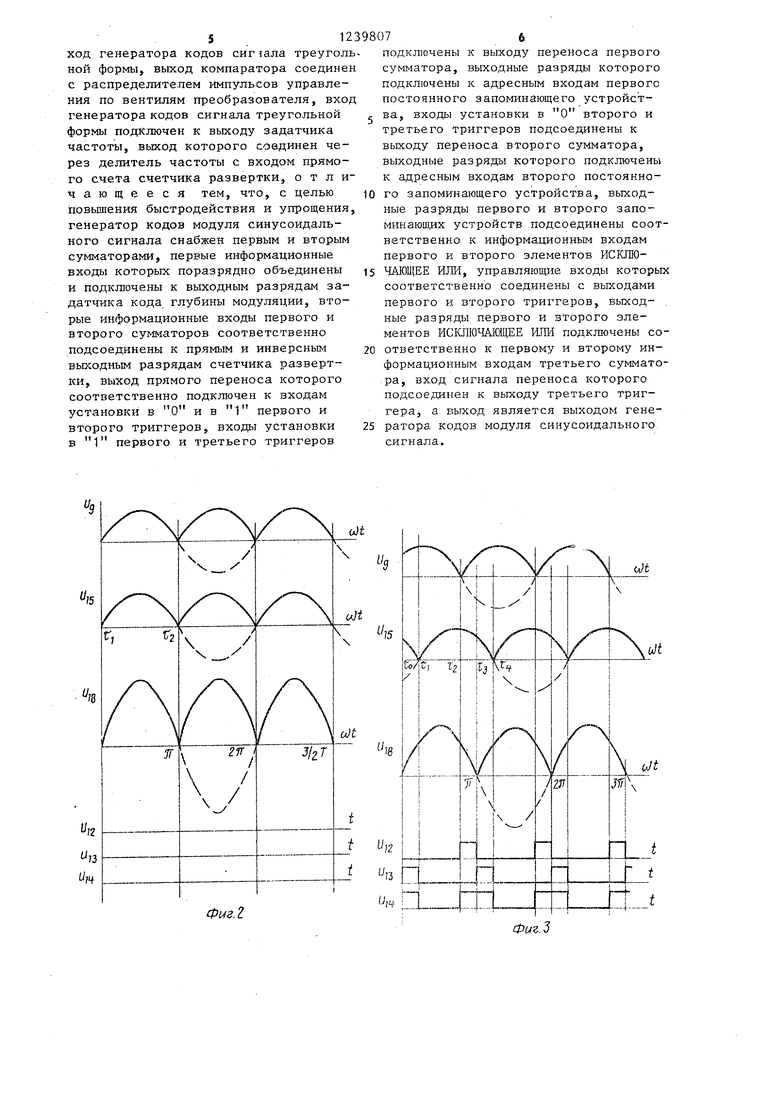

Целью изобретения является повышение быстродействия и упрощение, На фиг.1 представлена функциональная схема устройства; на фиг.2диаграммы на выходных элементах генератора кода модуля синусоидальног сигнала с последовательным уменьшенем амплитуды выходного сигнала (кодовая информация на выходах элементов показана в виде прямопропорцио- нальных им напряжений).

Устройство содержит генератор 1 кодов модуля синусоидального сигнала, выход которого соединен с одним из входов компаратора 2, к другому входу которого подключен выход генератора 3 кодов сигнала треугольной формы, а выход компаратора 2 соединен с распределителем 4 импульсов управления по вентилям преобразователя, причем вход генератора 3 кодов сигнала треугольной формы подключен к выходу задатчика 5 частоты, выход которого соединен через Делитель 6 частоты с входом прямого счета счетчика 7 развертки, а также задат чик 8 кода глубины модуляции и первое постоянное запоминающее устройство (ПЗУ) 9, при этом генератор 1 кодов модуля синусоидального сигнала содержит первьш 10 и второй 11 сумматоры, первые информационные входы которых поразрядно объединены и подключены к выходным разрядам задатчика 8 кода глубины модуляции, вторые информационные входы первого 10 и второго 11 сумматоров соответственно подсоединены к прямым и инверсным выходным разрядам счетчика 7 развертки, выход прямого переноса которого соответственно подключен к входам установки в ноль и в единицу первого 12 и второго 13 триггеров, входы установки в единицу первого 12 и третьего 14 триггеров подключены к выходу переноса первого сумматора 10, выходные разряды которого подключены к адресным входам первого постоянного запоминаю щего устройства 9, входы установки в ноль второго 13 и третьего 14 триггеров подсоединены к выходу переноса второго сумматора 11, выходные разряды .которого подключены к адресным

)

5

0

5

0

5

0

5

входам второго постоянного запоминающего устройства 15, выходные разряды первого 9 и второго 15 запоминающего устройства подсоединены соответственно к информационным входам первого 16 и второго 17 элементов ИСКЛЮЧАЮЩЕЕ ШН, управляющие входы которых соответственно соединены с выходами первого 12 и второго 13 триггеров, выходные разряды первого 16 и второго.17 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены соответственно к первому и второму информационным входам третьего сумматора 18, вход сигнала переноса которого подсоединен к выходу третьего триггера 14.

Устройство работает следующим образом.

Компаратор 2 сравнивает коды, поступающие на его входы с выхода генератора 1 кодов модуля синусоидаль- ного сигнала и с выхода генератора 3 кодов сигнала треугольной формы, и формирует в моменты их равенства импульсы, которые распределяет по вентилям преобразователя распределитель 4 импульсов управления. При изменении выходной частоты задатчика 5 происходит регулирование частоты выходного напряжения. Делитель 6 определяет кратность частоты развертки модулируемого кода сигнала треугольной формы на выходе генератора 3 по отношвнию к выходному сигналу генератора 1 кодов модуля синусоиды.

С выхода задатчика 5 частоты через делитель 6 импульсы высокой часг тоты поступают на вход счетчика 7 развертки, на выходных разрядах инверсного кода присутствует линейно yбывaюE ий код в этом же интервале времени. При нулевом выходном коде задатчика 8 кода глубины модуляхдаи, который соответствует максимальному выходному напряжению силового пре- образозателя., выходной код первого 10 и второго 11 сумматоров повторяет код соответственно на выходных разрядах прямого и инверсного кода счетчика 7 развертки, в соответствии с которым из первого 9 и второго 15 ПЗУ считывается код предварительно записанной кривой полупериода синусоид, причем из первого ПЗУ 9 выходной код считывается при изменении кода адреса от нулевого до максимального, а из второго ПЗУ 15 наоборот - выходной код считывается при

31

изменении кода адреса от максимального до нулевого. При нулевом выходном коде задатчика 8 глубины модуляции в каждый момент времени выходной код на выходах первого 9 и второго 15 ПЗУ одинаков () и третий сумматор 18 осуществляет арифметическое сложение этих кодов, которые проходят без изменения через первый 16 и второй 17 логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.

Логические элементы 16 и 17 работают в соответствии со следующим логическим условием. При наличии на управляющем входе логического нуля их выходной код повторяет входной информационный код. При логической единице на управляющем входе выходной код логических элементов ИСКЛЮ- ЧАЩЕЕ ИЛИ 16 и 17 является инверсным по отношению к входному. Управление этими элементами осуществляется соответственно первым 12 и вторым 13 триггерами (фиг.2-5), третий триггер 14 осуществляет коррекцию младшего разряда переноса третьего сумматора 18 путем формирования логической единицы при операции вычитания и формирование логического нуля, когда третий сумматор 18 осуществляет операцию суммирования. Переключение выходных кодов триггеров 12-14 происходит в соответствии с моментами формирования нулевых кодовых состояний на выходах прямого переноса счетчика 7 развертки, первого 10 и второго 11 сумматоров. При увеличении выходного кода задатчика 8 глубины модуляции линейно возрастающий код на выходе первого сумматора 10 по отношению к линейно возрастающему выходному коду счетчика 7 развертки сдвигается влево, а линейно убывающий код на выходе второго суммато- . ра 11 сдвигается вправо. Первый сумматор 10 работает в режиме суммирования входных кодов, а второй сумматор 11 в режиме вычитания. При этом в соответствии со сдвигом адресных кодов на выходных разрядах первого 10 и второго 11 сумматоров информация на выходе первого 9 и второго 15 ПЗУ также сдвигается влево для первого ПЗУ 9 и вправо для второго ПЗУ 15. Так как в ПЗУ 9 и 15 записан код только полупериода кривой синусоиды, то операции суммирования для получения на выходе третьего сумматора 18 кода модуля синусоидального сигнала.

074

регулируемого по амплитуде, недостаточно.

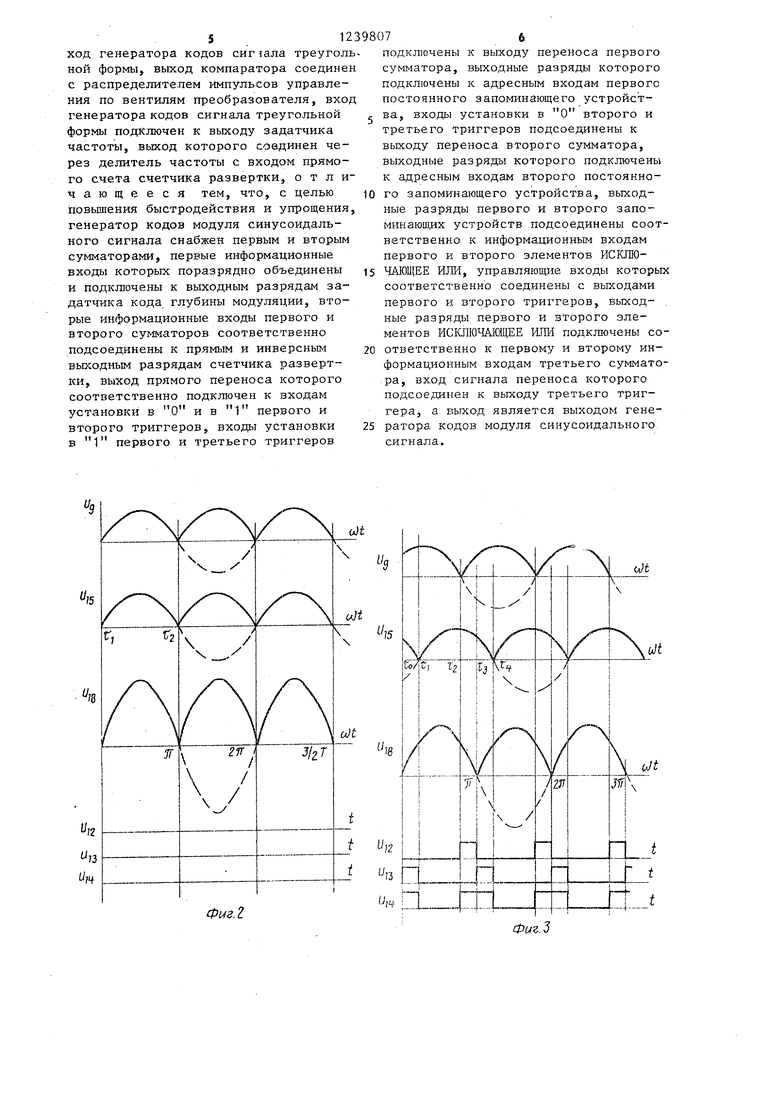

Так для момента времени Т., - С, (фиг.З) необходимо из выходного кода первого ПЗУ 9 вычесть выходной код второго ПЗУ 15, в интервале t, - о осуществить операцию сложения выходных кодов первого 9 и второго 15 ПЗУ, а в интервале времени С - t j

из выходного кода второго ПЗУ 15 вычесть выходной код первого ПЗУ 9. Далее указанные операции повторяются. Третий сумматор 18 в совокупности с логическими элементами ИСК- ЛЮЧА10ЩЕЕ ИЛИ 16 и 17 образуют арифметическое устройство, которое и выполняет указанные операции под воздействием управляющих сигналов с выходов триггеров 12-14.

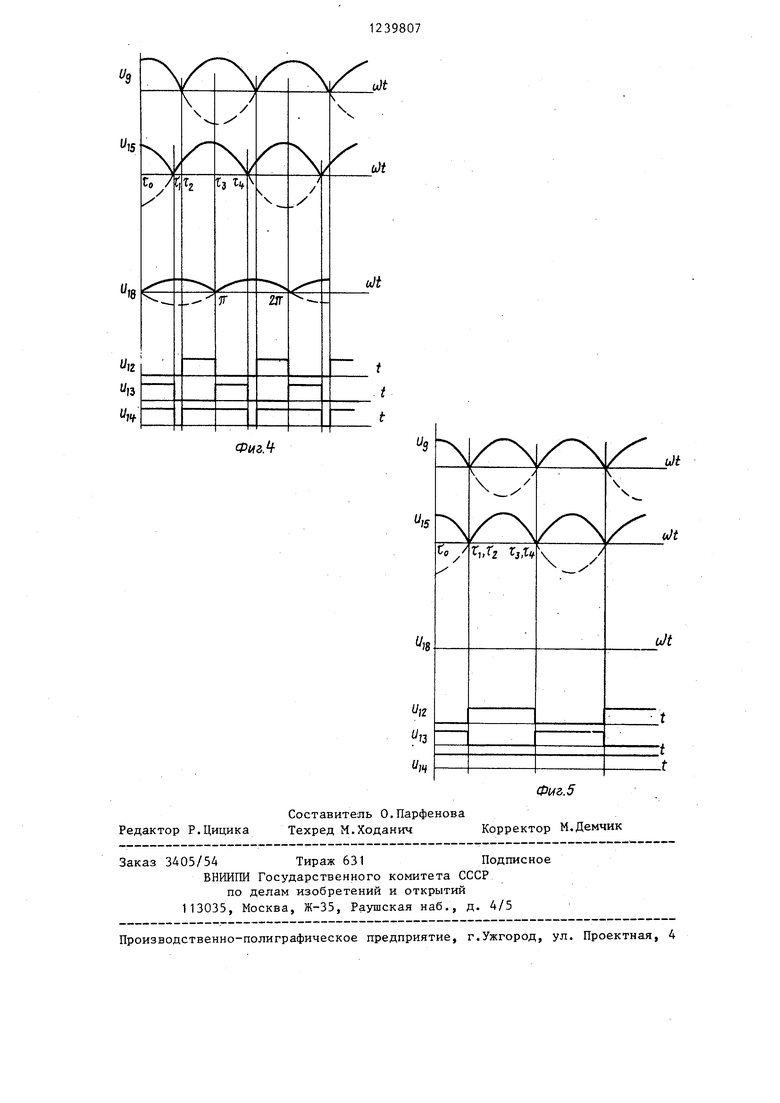

При дальнейшем увеличении кода на выходе задатчика 8 кода глубины модуляции интервал t,- (фиг.4) суммирования выходных кодов первого 9 .и второго 15 ПЗУ уменьшается, и при

максимальной величине кода задатчика 8 глубины модуляции интервал С , - вырождается в ноль, при этом в моменты времени Г - , из выходного

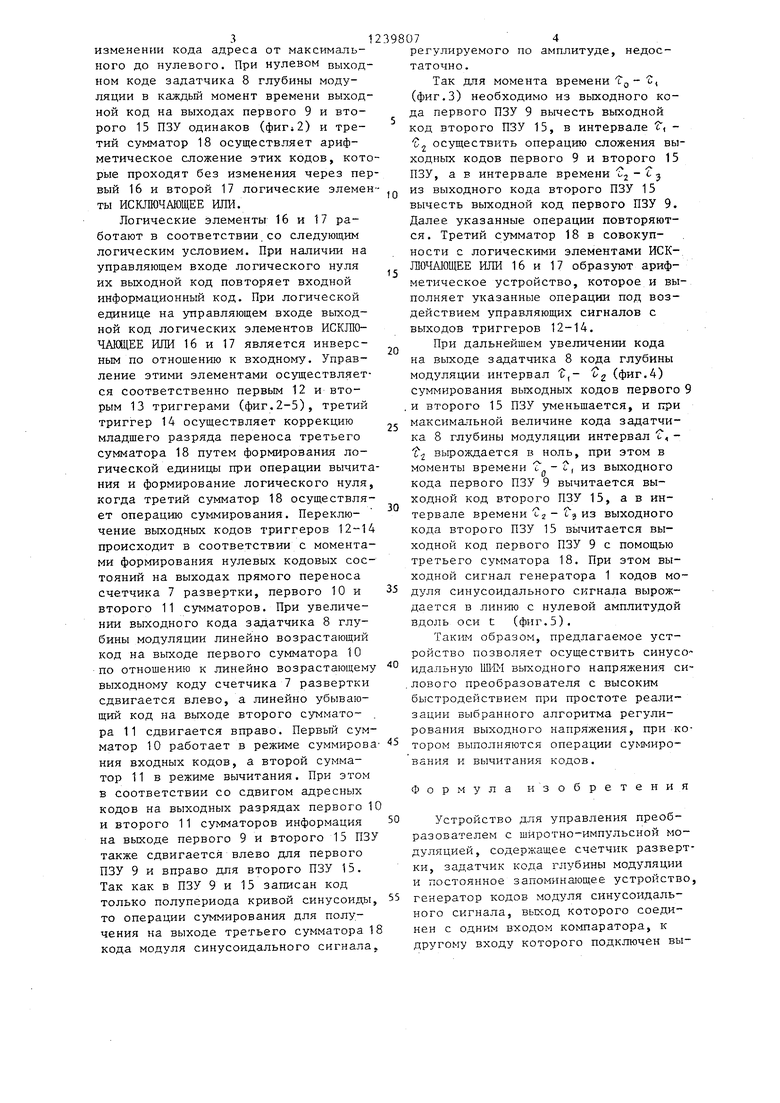

кода первого ПЗУ 9 вычитается выходной код второго ПЗУ 15, а в интервале времени cj- с 3 из выходного кода второго ПЗУ 15 вычитается выходной код первого ПЗУ 9 с помощью третьего сумматора 18. При этом выходной сигнал генератора 1 кодов модуля синусоидального сигнала вырождается в линию с нулевой амплитудой вдоль оси t (фиг.5).

Такн-м образом, предлагаемое устройство позволяет осуществить синусоидальную IIII M выходного напряжения си- .левого преобразователя с высоким быстродействием при простоте реализации выбранного алгоритма регулирования выходного напряжения, при котором выполняются операции суммирования и вычитания кодов.

Формула изобретения

Устройство для управления преобразователем с шйротно-импульсной модуляцией, содержащее счетчик развертки, задатчик кода глубины модуляции и постоянное запоминающ.ее устройство,

генератор кодов модуля синусоидального сигнала, выход которого соединен с одним входом ко таратора, к другому входу которого подключен вы

51

ход генератора кодов сиг lana треугол ной формы, выход компаратора соедине с распределителем импульсов управления по вентилям преобразователя, вхо генератора кодов сигнала треугольной формы подключен к выходу задатчика частоты, выход которого соединен через делитель частоты с входом прямого счета счетчика развертки, отличающееся тем, что, с целью повьшения быстродействия и упрощения генератор кодов модуля синусоидального сигнала снабжен первым и вторым сумматорами, первые информационные входы которых поразрядно объединены и подключены к выходным разрядам задатчика кода глубины модуляции, вторые информационные входы первого и второго сумматоров соответственно подсоединены к прямым и инверсным выходным разрядам счетчика развертки, выход прямого переноса которого соответственно подключен к входам установки в О и в 1 первого и второго триггеров, входы установки в 1 первого и третьего триггеров

10

807

подключены

6

к вьгкоду переноса первого сумматора, выходные разряды которого подключены к адресным входам первого постоянного запоминающего устройства, входы установки в О второго и третьего триггеров подсоединены к выходу переноса второго сумматора, выходные разряды которого подключены к адресным входам второго постоянного запоминающего устройства, выходные разряды первого и второго запоминающих устройств подсоединены соответственно к информационным входам первого и второго элементов ИСКЛЮ- 15 ЧАЮЩЕЕ ИЛИ, управляющие входы которых соответственно соединены с выходами первого и второго триггеров, выходные разряды первого и второго элементов ИСКЛЮЧМЩЕЕ И11И подключены соответственно к первому и второму информационным входам третьего сумматора, вход сигнала переноса которого подсоединен к выходу третьего триггера, а выход является выходом генератора кодов модуля синусоидального сигнала.

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления синусоидальными вибрациями | 1985 |

|

SU1269112A1 |

| Устройство для управления автономным инвертором | 1990 |

|

SU1810973A1 |

| Электронные часы | 1980 |

|

SU928169A1 |

| Дискретный регулятор уровня | 1984 |

|

SU1262461A1 |

| Измеритель глубины модуляции | 1989 |

|

SU1737370A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Устройство поиска шумоподобного сигнала | 1988 |

|

SU1540020A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1149266A1 |

| Цифровой генератор базисных функций | 1980 |

|

SU968796A1 |

| Калибратор переменного напряжения | 1983 |

|

SU1115031A1 |

Изобретение относится к электротехнике и может быть использовано во вторичных источниках питания с широтно-импульсной модуляцией выходного напряжения. Цель изобретения повьшение быстродействия и упрощение. Устройство содержит генератор кодов модуля синусоидального сигнала (ГКМСС) 1, компаратор 2, генератор 3 кодов сигнала треугольной формы, распределитель 4 импульсов управления, задатчик 5 частоты, делитель 6 частоты. ГКМСС 1 выполнен на счетчике 7 развертки, задатчике 8 кода глубины модуляции, запоминающем устройстве (ЗУ) 9. При этом введение в ГКМСС 1 сумматоров 10, 11 и 18 и выполнение его на триггерах 12, 13 и 14 и втором ЗУ 15 и исключающих элементах ИЛИ 16 и 17 позволяет осуществить синусоидальное выходное напряжение устройства при простоте реализации выбранного алгоритма регулирования выходного напряжения, при котором выполняются операции суммирования и вычитания кодов . 5 ил. Q е

Фиг. г

Ув

/

/

/

3

У

Г8

7Г

2П

Фиг.

Редактор Р.Цицика

Составитель О.Парфенова

Техред М.Ходанич Корректор М.Демчик

Заказ 3405/54 Тираж 631Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

, - - .-«в-- - - ,м.-««

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

0/

J

/

/

/

ч

/5

ft/f

tn /

1/2 t:j,

х

iJ

t

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2011 |

|

RU2462812C1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-06-23—Публикация

1984-11-01—Подача