тора по модулю два (п +1)-го генератора псевдослучайных кодов, информационный выход регистра сдвига которого связан с входом первого блока индикации, первые и вторые выходы первого и второго переключателей блока управления подключены соответственно к первым и вторым входам второго и третьего триггеров, выход третьего триггера соединен с первым входом первого элемента ИЛИ, вход первого элемента задержки соединен со счетным входом первого счетчика, выход переполнения которого подключен к второму входу первого триггера, о тличающееся тем, что, с целью увеличения глубины контроля, в него введены третий, четвертьй, пятый, шестой, седьмой, восьмой и девятый элементы И, второй, третий и четвертый элементы ИЛИ, второй и третий счетчики, четвертьй триггер, второй блок индикации и третий переключатель, причем выход третьего триггера соединен с первым входом четвертого триггера, выход которого подключен к первому входу третьего элемента И, второй вход которого свя зан с выходом второго элемента, а выход - с входом первого элемента задержки, вторым входом первого элемента И, вторым входом, первого элемента ИЛИ и первым входом четвертого элемента И, выход первого элемента ШШ подключен к входу второго элемента задержки, выход первого элемента задержки соединен с первым ;входом второго элемента И, второй вход которого связан с нулевым выходом первого триггера и с вторым входом четвертого элемента И, выход .которого подключен к счетному входу

49266

второго счетчика, выход третьего переключателя связан с входом элемента НЕ, первыми входами пятого, шестого и седьмого элементов И, выход элемента НЕ связан с первыми входами восьмого и девятого элементов И, второй вход пятого элемента И соединен с выходом переполнения второго счетчика и с счетным входом третьего счетчика, а выход пятого элемента И связан с первым входом второго элемента ИЛИ, второй вход которого связан с первым вькодом переполнения третьего счетчика, а третий вход второго элемента ИЛИ подключен к входам начальной установки второго и третьего счетчиков и к выходу второго триггера, выход второго элемента ИЛИ соединен с вторым входом четвертого триггера, информационнъш выход третьего счетчика подключен к входу второго блока индикации, второй выход регистра сдвига (ц + 1)-го генератора псевдослучайных кодов подключен к второму входу седьмого элемента И, информационный вход регистра сдвига подключен к выходу третьего элемента ИЛИ, третий вход сумматора по модулю два (п+ 1)-го генератора псевдослучайных кодов соединен с вторыми входами шестого И девятого элемента И, выход сумматора по модулю два связан с вторым входом восьмого элемента И, выходы шестого и восьмого элементов И подключены к входам третьего элемента ИЛИ, а выходы седьмого и девятого элемента И - к входам четвертого элемента ИЛИ, выход котороп подключен к вторым входам элементов И второй группы первого генератора псевдослучайных кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ., содержащее задатчик тестов, блок управления, включающий в себя первый, второй и третий триггеры, элемент НЕ, первый элемент ИЛИ, первый и второй элементы задержки, первый элемент И, первый счетчик и первый и второй переключатели, п генераторов псевдослучайных кодов ( п- число выходов контролируемого логического блока), каждый из которых включает в себя сумматор по модулю два, первую и вторую группы элементов И, элемент ИЛИ и регистр сдвига, (п + 1)-й генератор псевдослучайных кодов, содержащий сумматор по модулю два и регистр сдвига, а также блок индикации и второй элемент И, причем выходы первого и последнего регистров сдвига всех генераторов псевдослучайньк кодов соединены с первыми и вторыми входами сумматоров по модулю два, выход сумматора по модулю два в калсдом генераторе псевдослучайных кодов соединен с первыми. входами элементов И первой группы, информационный вход регистра сдвига в каждом генераторе псевдослучайных кодов свяэан с выходом элемента ИЛИ, первые и вторые входы которого соединены с выходами элементов И первой и второй групп соответственно, вторые входы элементов И первой группы подключены к единичному выходу первого триггера и к первому входу первого элемента И блока управления, первые входы второй группы элементов И соединены с нулевым выходом первого триггера блока управления, выход первого элемента И блока упо 9 равления подключен к задатчиkn ка тестов., выходы которого соединены с входами контролируемого логического блока, соединенного виходами соответственно с третьим входом каж|Дого сумматора по модулю два, вторые входы элементов И второй группы i -х генераторов псевдослучайных кодов соединены соответственно с вторым ;о вькодом каждого регистра сдвига ( 1 - 1)-х генераторов псевдослучайND ных кодов, второй вход каждого регист а ра сдвига связан с выходом второго Эд триггера блока управления, первым входом первого триггера блока управления, входом начальной установки первого счетчика и входом начальной установки регистра сдвига (И+ 1)-го генератора псевдослучайных кодов, информационный вход которого соединен с выходом элемента И, первый вход которого подключен к входу сдвига каждого регистра сдвига, выход последнего разряда регистра сдвига Ъ-го генератора псевдослучайных кодов соединен с третьим входом сумма

Изобретение относится к вычислительной технике и может быть использовано для контроля логических блоков автоматики .и цифровой вычислительной техники.

Известно устройство для контроля логических блоков, содержащее генератор тестов, выходы которого заведены на входы проверяемого логического блока, выходами соединенного с информационными входами сигнатурных анализаторов. Для получения обобщенной сигнатуры выходы сумматоров, которые входят в состав сигнатурных анализаторов, соединены че.рез сумматор с информационным входом общего сигнатурного анализатора И.

В результате одного сеанса контроля получаются обобщенная сигнатура, по которой можно судить о ра|боте способности проверяемого логического блока, и сигнатуры по каждо му его выходу.

Диагностические возможности данного устройства заключаются в том, что каждую из полученных сигнатур через коммутаторы и соединенный с их выходами селектор можно проанализировать на индикаторном элементе.

Недостатком этого устройства является большое количестао оборудования, требуемое для создания ri коммутаторов, селектора и узла управления блоком индикации.

Наиболее близким техническим решением к предлагаемому является устройство для контроля логических блоков, содержащее блок индикации, соединенный с выходами общего генератора псевдослучайных кодов, содержащего регистр сдвига и сумматор по модулю два, блок управления, генератор импульсов, элемент И, п генераторов псевдослучайных кодов по числу выходов контролируемого логического блока, каждый из которых содержит регистр сдвига, сумматор по модулю два, два элемента И и элемент ИЛИ, причем информационные входы генераторов псевдослучайных кодов соединены с выходами контролируемого логического блока и с выходами регистров сдвига предыдущих генераторов псевдослучайных кодов, а информационный вход общего генератора псевдо- случайных кодов соединен с выходом регистра сдвига in -го генератора псевдослучайных кодов 2J.

Известное устройство позволяет получить сигнатуры по каждому из выходов параллельно во времени, а также при определении годности выполнят одну операцию сравнения одной сигнатуры контролируемого логического блока с заданной в технической докуг ментации.

Недостатком известного устройства является низкая глубина контроля вследствие неиспользования для локализации неисправности сигнатур по каждог-гу из выходов контролируемого логического блока. Эти сигнатуры получаются в результате реализации тестовой программы и теряются при фомировании обобщенной сигнатуры.

Цель изобретения - увеличение глубины контроля с точностью до внешнего вывода контролируемого логического блока.

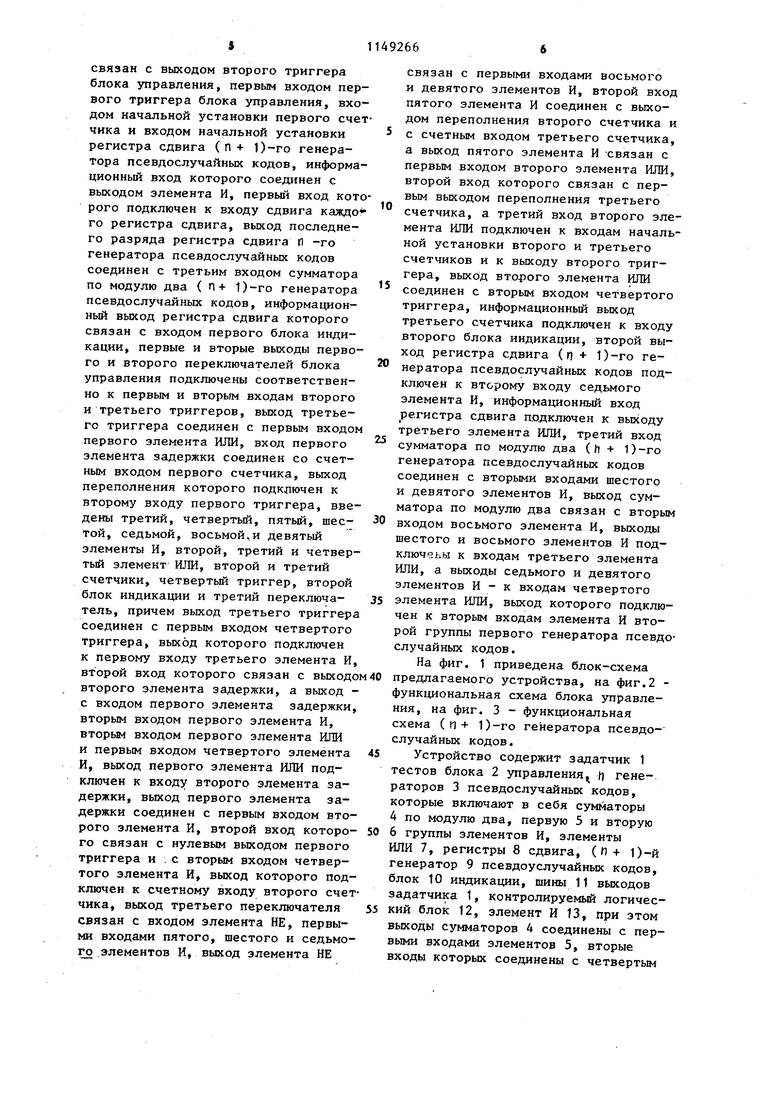

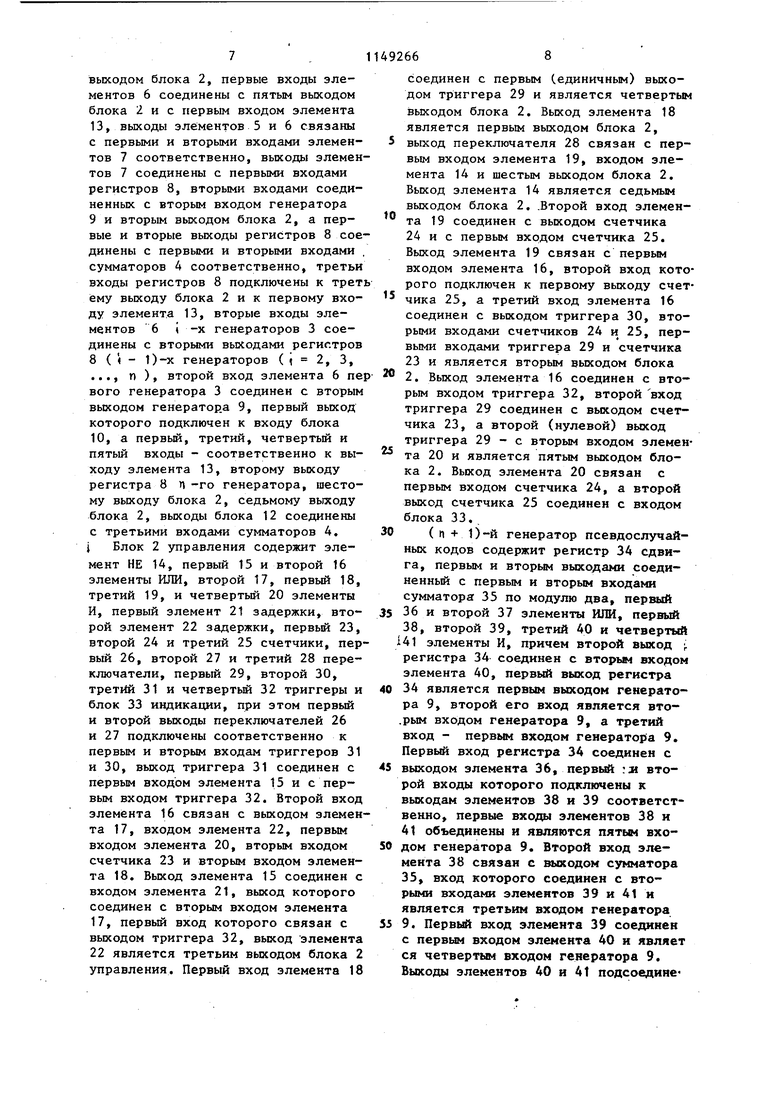

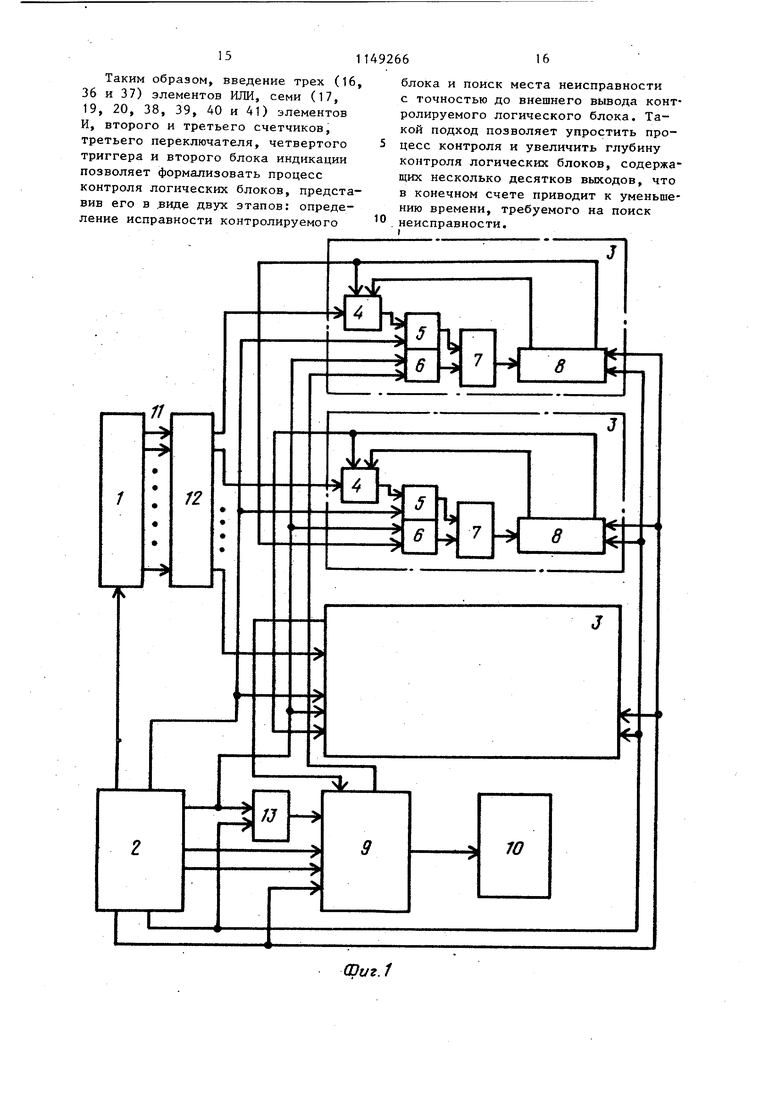

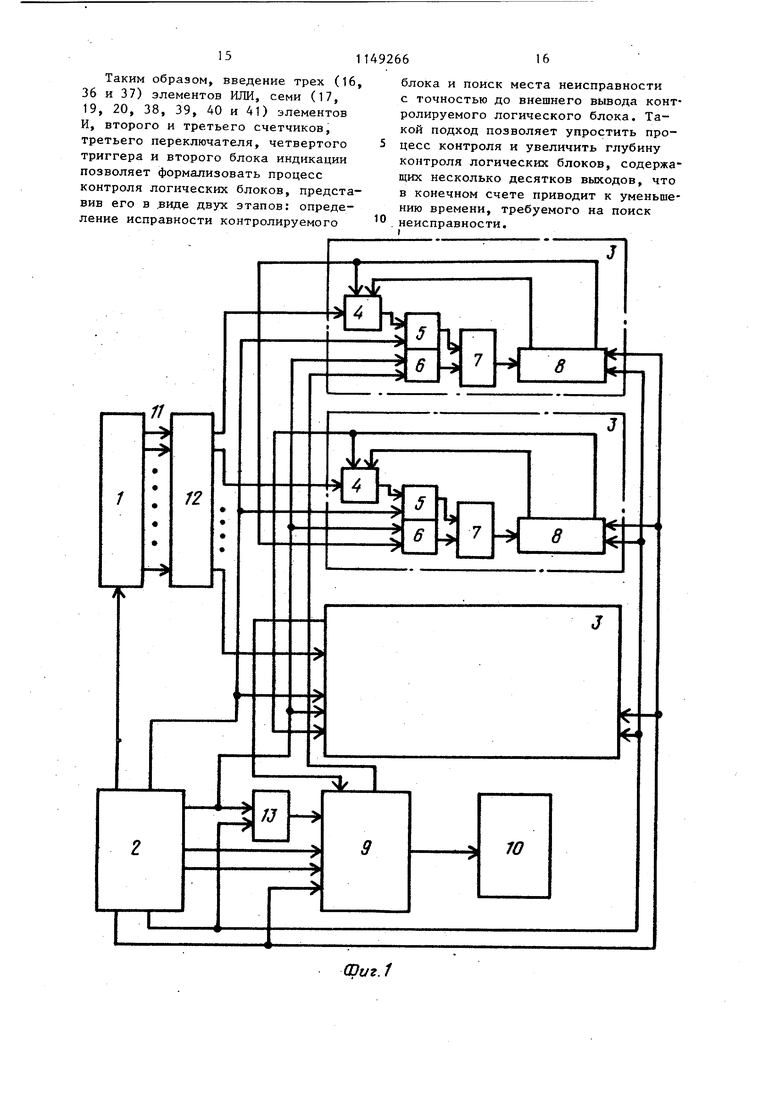

Поставленная цель достигается те что в устройство для контроля логических блоков, содержащее задатчик тестов, блок управления, включающий в себя первый, второй и третий триггеры, элемент НЕ, первый элемент ИЛИ, первый и второй элементы заздержки, первый элемент И, первый счетчик и первый и второй переключател И генераторов псевдослучайных кодов (п - число выходов контролируемого логического блока),каждьй из которых включает в себя сумматор по модулю два первую и вторую группы элементов И, элемент ИЛИ и регистр сдвига, (ц+ 1)-й генератор псевдослучайных кодов, содержащий сумматор по модулю два и регистр сдвига, а также блок индикации и второй элемент И, причем выходы первого и последнего регистров сдвига всех генераторов псевдослучайных кодов соединены с первыми и вторыми входами сумматоро по модулю два, выход сумматора по модулю два в каждом генераторе псевдослучайных кодов соединен с первыми входами элементов И первой группы, информационный вход регистра сдвига в каждом генераторе псевдослучайных кодов связан с ; выходом элемента ИЛИ, первые и вторые входы которого соединены с выходами элементов И первой и второй групп соответственно, вторые входы элементов И первой группы подключены к едничному выходу первого триггера и к первому входу первого элемента И блока управления, первые входы второй группы элементов И соединены с нулевым выходом первого триггера блока управления, выход первого элемента И блока управления подключен к входу задатчика тестов, выход которого соединены с входами контролируемого логического блока, соединенного выходами соответственно с третьим входом каждого сумматора по модулю два, вторые входы элементов И второй группы -X генераторов псевдослучайных кодов соединены соответственно с вторым выходом каждого регистра сдвига ( i - 1)-х генераторов псевдослучайных кодов, второй вход каждого регистра сдвига связан с выходом второго триггера блока управления, первым входом первого триггера блока управления, входом начальной установки первого счет чика и входом начальной установки регистра сдвига (п+ 1)-го генератора псевдослучайных кодов, информационный вход которого соединен с выходом элемента И, первый вход кото рого подключен к входу сдвига каждо го регистра сдвига, выход последнего разряда регистра сдвига П -го генератора псевдослучайных кодов соединен с третьим входом сумматора по модулю два (1+ 1)-го генератора псевдослучайных кодов, информационный выход регистра сдвига которого связан с входом первого блока индикации, первые и вторые выходы первого и второго переключателей блока управления подключены соответственно к первым и вторым входам второго и третьего триггеров, выход третьего триггера соединен с первым входом первого элемента ИЛИ, вход первого элемента задержки соединен со счетным входом первого счетчика, выход переполнения которого подключен к второму входу первого триггера, введены третий, четвертый, пятый, шеетой, седьмой, восьмой,и девятый элементы И, второй, третий и четвертый элемент ИЛИ, второй и третий счетчики, четвертьй триггер, второй блок индикации и третий переключатель, причем выход третьего триггера соединен с первым входом четвертого триггера, выход которого подключен к первому входу третьего элемента И, второй вход которого связан с выходо второго элемента задержки, а выход с входом первого элемента задержки вторым входом первого элемента И, вторьм входом первого элемента ИЛИ и первым входом четвертого элемента И, выход первого элемента ИЛИ подключен к входу второго элемента задержки, выход первого элемента задержки соединен с первым входом второго элемента И, второй вход которого связан с нулевым выходом первого триггера и . с вторьм входом четвертого элемента И, выход которого подключен к счетному входу второго счет чика, выход третьего переключателя связан с входом элемента НЕ, первыми входами пятого, шестого и седьмо го элементов И, выход элемента НЕ связан с первыми входами восьмого и девятого элементов И, второй вход пятого элемента И соединен с выходом переполнения второго счетчика и с счетным входом третьего счетчика, а выход пятого элемента И связан с первым входом второго элемента ИЛИ, второй вход которого связан с первым выходом переполнения третьего счетчика, а третий вход второго элемента ИЛИ подключен к входам начальной установки второго и третьего счетчиков и к выходу второго триггера, выход второго элемента ИЛИ соединен с вторым входом четвертого триггера, информационный выход третьего счетчика подключен к входу второго блока индикации, второй выход регистра сдвига (П + 1)-го генератора псевдослучайных кодов подключен к второму входу седьмого элемента И, информационный вход регистра сдвига подключен к выходу третьего элемента ИЛИ, третий вход сумматора по модулю два (Л + 1)-го генератора псевдослучайных кодов соединен с вторыми входами шестого и девятого элементов И, выход сумматора по модулю два связан с вторым входом восьмого элемента И, выходы шестого и восьмого элементов И подключены к входам третьего элемента ИЛИ, а выходы седьмого и девятого элементов И - к входам четвертого элемента ИЛИ, выход которого подключен к вторым входам элемента И второй группы первого генератора псевдослучайных кодов. На фиг. 1 приведена блок-схема предлагаемого устройства, на фиг.2 функциональная схема блока управления, на фиг. 3 - функциональная схема (ц+ 1)-го генератора псевдослучайных кодов. Устройство содержит задатчик 1 тестов блока 2 управления ц генераторов 3 псевдослучайных кодов, которые включают в себя сумматоры 4 по модулю два, первую 5 и вторую 6 группы элементов И, элементы ИЛИ 7, регистры 8 сдвига, (1 + 1)-й генератор 9 псевдоуслучайных кодов, блок 10 индикации, шины 11 выходов задатчика 1, контролируемый логический блок 12, элемент И 13, при этом выходы сумматоров 4 соединены с первыми входами элементов 5, вторые входы которых соединены с четвертым 7 . выходом блока 2, первые входы элементов 6 соединены с пятым выходом блока 2 и с первым входом элемента 13, выходы элементов 5 и 6 связаны с первыми и вторыми входами элементов 7 соответственно, выходы элемен тов 7 соединены с первыми входами регистров 8, вторыми входами соединенных с вторым входом генератора 9 и вторым выходом блока 2, а первые и вторые выходы регистров 8 сое динены с первыми и вторыми входами сумматоров 4 соответственно, третьи входы регистров 8 подключены к трет ему выходу блока 2 и к первому входу элемента 13, вторые входы элементов 6 i -X генераторов 3 соединены с вторыми выходами регистров 8 ( i - 1)-X генераторов (t 2, 3, ..., п ), второй вход элемента 6 пе вого генератора 3 соединен с вторым выходом генератор.а 9, первый выход которого подключен к входу блока 10, а первьй, третий, четвертый и пятый входы - соответственно к выходу элемента 13, второму выходу регистра 8 П -го генератора, шестому выходу блока 2, седьмому выходу блока 2, выходы блока 12 соединены с третьими входами сумматоров 4. i Блок 2 управления содержит элемент НЕ 14, первый 15 и второй 16 элементы ИЛИ, второй 17, первый 18, третий 19, и четвертый 20 элементы И, первый элемент 21 задержки, второй элемент 22 задержки, первый 23, второй 24 и третий 25 счетчики, пер вый 26, второй 27 и третий 28 переключатели, первый 29, второй 30, третей 31 и четвертый 32 триггеры и блок 33 индикации, при этом первый и второй выходы переключателей 26 и 27 подключены соответственно к первым и вторым входам триггеров 31 и 30, выход триггера 31 соединен с первым входом элемента 15 и с первым входом триггера 32. Второй вход элемента 16 связан с выходом элемен та 17, входом элемента 22, первым входом элемента 20, вторым входом счетчика 23 и вторым входом элемента 18. Выход элемента 15 соединен с входом элемента 21, выход которого соединен с вторым входом элемента 17, первый вход которого связан с выходом триггера 32, выход элемента 22 является третьим выходом блока 2 управления. Первый вход элемента 18 668 соединен с первым (единичным) выходом триггера 29 и является четвертым выходом блока 2. Выход элемента 18 является первым выходом блока 2, выход переключателя 28 связан с первым входом элемента 19, входом элемента 14 и шестым выходом блока 2. Выход элемента 14 является седьмым выходом блока 2. .Второй вход элемента 19 соединен с выходом счетчика 24 и с первым входом счетчика 25. Выход элемента 19 связан с первым входом элемента 16, второй вход которого подключен к первому выходу счетчика 25, а третий вход элемента 16 соединен с выходом триггера 30, вторыми входами счетчиков 24 и 25, первыми входами триггера 29 и счетчика 23 и является вторым выходом блока 2. Выход элемента 16 соединен с вторым входом триггера 32, второй вход триггера 29 соединен с выходом счетчика 23, а второй (нулевой) выход триггера 29 - с вторым входом элемента 20 и является пятым выходом блока 2. Выход элемента 20 связан с первым входом счетчика 24, а второй выход счетчика 25 соединен с входом блока 33. (П + 1)-и генератор псевдослучайных кодов содержит регистр 34 сдвига, первым и вторым выходами соединенный с первым и вторым входами сумматора: 35 по модулю два, первый 36 и второй 37 элементы ИЛИ, первый 38, второй 39, третий 40 и четвертый 41 элементы И, причем второй выход регистра 34 соединен с вторьм входом элемента 40, первый выход регистра 34 является первым выходом генератора 9, второй его вход является вторым входом генератора 9, а третий вход - первьм входом генератора 9. Первый вход регистра 34 соединен с выходом элемента 36, первый :м второй входы которого подключены к выходам элементов 38 и 39 соответственно, первые входы элементов 38 и 41 объединены и являются пятым входом генератора 9. Второй вход элемента 38 связан G выходом сумматора 35, вход которого соедииен с вторыми входами элементов 39 и 41 и является третьим входом генератора 9. Первый вход элемента 39 соединен с первым входом элемента 40 и являет ся четвертым входом генератора 9. Выходы элементов 40 и 41 подсоедине

ны к входам элемента 37, выход которого является вторым выходом генератора 9.

Работа устройства возможна в двух режимах: проверка работоспособности контролируемого блока в целом, локализация неисправности контролируемого блока с точностью до внешнего выхода.

В первом режиме устройство работа ет следующим образом.

Блок 2 управления по второму выходу вьщает сигнал Начальная установка, устанавливает регистры 8 и ( 11 + 1)-й генератор 9 псевдослучайньк кодов в исходное состояние, Задатчик 1 тестов по шинам 11 задает на блок 12 информадаю первого теста. С выходов блока 12 информация через сумматоры 4, вьшолняющие операцию сложения по модулю два, чйрез элементы 5, которые открыты стробом с блока 2, и элементы 7 поступают на входы регистров 8. В это время блок 2 закрывает элементы 6 и импульсами сдвига, поступающими на вторые входы регистров 8, записывает эту информаг цию параллельно в первые разряды регистров В, каждый из которых имеет п разрядов. Блок 2 блокирует по второму входу элемент 13,поэтому импульсы сдвига не поступают на (п+ 1)-й генератор 9 псевдослучайных кодов и не записывают в него информацию.

Затем задатчик 1 вьщает второй тест. Блок 2 по второму импульсу сдвига переписывает в регистры 8 с учетом влияния обратных связей через сумматоры 4 информацию с выходов контролируемого блока 12. В результате реализации всей программы блок 2 записьгаает в регистры 8 поканально в сжатом (в сигнатуры виде информацию с выходов блока 12 .По оконч НИИ программы блок 2 закрьшает элементы 5 и открывает элементы 6 и элементы 13, после чего блок 2 вьщает импульсный пакет с числом импульсов m П , по которым информация из регистров 8 предьщущих каналов через открытые элементы 6 и 7 поступает в регистры 8 последукяцих каналов, а с последнего канала - в (п + 1)-й генератор псевдослучайных кодов 9. Причем (п 1)-й генератор псевдослучайных кодов 9 организован таким образом, что по сигналам разрешения с

блока 2 управления в этом режиме на второй вход элемента 6 первого генератора псевдослучайных кодов 3 поступает информация с выхода регистра сдвига 8п-го генератора псевдослучайных кодов 3. В результате (И + 1)-й генератор псевдослучайных кодов 9 содержит информацию (сжатую) являющуюся выходной реакцией контролируемого блока 12 на входную тестовую программу.

Таким образом, блок индикации индицирует итоговую сжатую информацию, а сдвиговые регистры 8 генераторов 3 псевдослучайных кодов содержат сигнатуры, которые быпи получены в результате выполнения тестовой программы. Значение информации в оцифрованном виде, хранящийся в (ц + 1)-ом генераторе 9 псевдослучайных кодов, оператор сравнивает с эталонным значением, приведенным в технических условиях контролируемый блок, и делает заключение о его исправности. Количество тактов, необходимое для реализации всей программы, равно N + fnxn, где N - число тестов, вьщаваемых блоком 1.

Если сигнатуры, приведенные в технических условиях и высвечиваемые блоком 10 индикации, не совпадают, то контролируемое устройство 12 неисправно, В этом случае нужно перейти к второму режиму контроля.

В режиме локализации неисправности устройство работает следующим образом.

Блок 2 вьщает сигналы, соответствующие этому режиму. При этом элементы 5 закрыты, элементы 6 открыты, а ( Г1 + 1)-й генератор 9 .псевдослучайных кодов по сигналам, поступающим с шестого и седьмого выходов блока 2, настраивается таким образом, что входную информацию, поступающую с выхода и -го генератора 3 псевдослучайных кодов, он не сжимает в сигнатуры, как это было в предыдущем режиме, а пропускает через свой внутренний регистр и подает на второй вход элемента 6 первого генератора 3 псевдослучайных кодов. Блок 2 вьщает пачку из m -импульсов, по которым, информация из регистров 8 предыдущих каналов через открытые элементы 6 и 7 поступает в регистры 8 последующих каналов, с второго выхода регистра 8 последнего кана11ла информация поступает в (tt + 1)-й генератор псевдослучайных кодов, а с выхода (п + 1)-го генератора псевдослучайных кодов - в регистр первого канала. В результате в регистре 8 второго канала хранится информация с первого канала, в регистре 8 третьего канала - информация второго канала и т.д., в (ri+1j-w генераторе псевдослучайных кодов хранится информация последнего канала, а в регистре 8 первого канала - информация (h + 1)-го генератора псевдослучайных кодов. Таким образом, на блоке 10 индикации высвечивается код сигнатуры И-го канала. Оператор сравнивает этот код со значением эталонной сиг натуры этого канала, приведенной в технических условиях, и делает заключение об исправности И -го канала. Далее производятся аналогичные действия для всех каналов. После выдачи М + 1 пачек из m импульсов в регистрах Вив (h + 1)-м генераторе 9 псевдослучайных кодов хранится прежняя информация, полученная в результате выполнения тестовой программы. Блок 2 управления в режиме проверки работоспособности контролируе мого блока работает следующим образом. В этом режиме переключатель 28 должен быть нажат. При этом с выход переключателя 28 на элемент 19 и шестой выход блока 2 управления пос тупает сигнал запрета, а с выхода элемента 14 на пятый вход генератора 9 - сигнал разрешения. По нажатию переключателя 27 с выхода триггера 30 вьщается импуль который устанавливает в единичное состояние триггер 29, в нулевое состояние счетчики 23-25, а также через элемент ИЛИ 16 устанавливает Б нулевое состояние триггер 32. Си нал исходного состояния поступает в регистры 8 и генератор 9 псевдослучайных кодов. Сигнал с первого выхода триггера 29 поступает на элементы 5, а с второго выхода - н элементы 6 и элемент 13. Так как триггер 32 установлен в нулевое состояние, а триггер 29 в единично то элемент 18 .открыт, а элемент 17 закрыт. 66 По нажатию переключателя 26 триггер 31 выдает импульс, устанавливающий в единичное состояние триггер 32. Импульс с триггера 31 поступает уерез элемент ИЛИ 15, элемент 21 задержки на первый вход элемента 17, открытого триггером 32. С выхода элемента 17 сигнал поступает вновь на элемент 15 и т.д., создавая непрерывную последовательность импульсов, которые через открытый триггером элемент И 18 поступают на задатчик 1 тестов и осуществляют вывод очередных тестов. Через элемент 22 задержки эти же импульсы поступают в качестве сигналов сдвига на регистры 8 сдвига и элемент 13. Импульсы с выхода элемента 17 подсчитывает счетчик 23, емкость которого равна N. По окончании программы сигнал пере полнения счетчика 23 переводит триггер 29 в нулевое состояние. При этом на элементы 6, 13 и 20 подается сигнал разрешения, а на элементы 5 и 18сигнал запрета. Далее начинается процесс получения обобщенной сигнатуры. С выхода элемента И 17 импульсы поступают через открытый триггером 29 элемент И 20 на счетный вход счетчика 24, емкость которого равна т. Сигнал переполнения с выхода счетчика 24 поступает на счетный вход счетчика 25 и не проходит через закрытый переключателем 28 элемент И 19. Емкость счетчика 25 равна П . После переполнения счетчик 24 автоматически сбрасывается в нулевое состояние. К этому моменту на вход первого 3 и (П+ 1)-го 9 генераторов псевдослучайных кодов поступает содержимое всех разрядов регистра 8 сдвига 1 -го генератора 3 псевдослучайных кодов. Затем счетчик 24 опять начинает подсчет импульсов. Процесс подсчета импульсов счетчиками 24 и 25 продолжается до тех пор, пока на выходе переполнения счетчика 25 не появится сигнал, который через элемент ИЛИ 16 сбросит триггер 32 в нулевое состояние, обрывая непрерьганзпо последовательность импульсов на выходе элемента 17. Генератор 9 псевдослучайных кодов содержит к этому моменту обобщенную сигнатуру , а регистры 8 сдвига содержат прежнюю информацию полученную в результате вьтолнения тестовой программы.

В режиме локализации неисправности с точностью до внешнего вывода переключатель 28 должен быть отжат,

.в результате чего с выхода этого переключателя на элемент 19 и шестой

выход блока 2 управления поступает сигнал разрешения, а с выхода элемента 14 на пятый вход (И + 1)-го генератора 9 псевдослучайных кодов сигнал запрета. При нажатии переключателя 26 на выходе триггера 31 появляется импульс, устанавливающий триггер 32 в единичное состояние благодаря чему разрешается формирование последовательности импульсов на выходе элемента 1/.

Через открытый триггером 29 элемент И 20 эти импульсы поступают на счетный вход счетчика 24. Сигнал переполнения с выхода этого счетчика

Через открытый переключателем 28 элемент И 19 и элемент ИЛИ 16 сбрасывает триггер 32 в нулевое состояние, обрывая последовательность импульсов на выходе элемента 17. В результате выполнения описанных процедур в генератор 9 псевдослучайных кодов будет занесена информация с выхода И -го генератора 3 псевдослучайных кодов, а регистр 8 сдвига

первого генератора 3 псевдослучайных кодов, будет содержать информацию генератора 9. При этом блок 10 индикации будет высвечивать код сигнатуры Ц -го генератора 3 псевдослучайных кодов, а на втором блоке 33 индикации высветится соответствующий код, который указьюает номер канала, сигнатура которого находится в данный момент в регистре 34 сдвига генератора 9 псевдослучайных кодов.

При повторном нажатии переключате ля 26 описанная последовательность действий повторится вновь и на блоке 10 индикации высветится код (h - 1)-го генератора псевдослучайных кодов. Нажимая последовательно переключатель 26 Ц раз можно просмотреть на блоке 10 индикации коды сигнатур всех генераторов 3 псевдослучайных кодов. После нажатия переключателя 26 (h + 1)-й раз регистры 8 и 34 сдвига будут содержать прежнюю информацию, полученную в результате реализации тестовой программы.

Генератор 9 псевдослучайных кодов в режиме проверки работоспособности

контролируемого логического блока работает следующим образом.

При поступлении сброса с выхода блока 2 управления регистр 34 сдвига устанавливается в нулевое состояние. После выработки сигнала начальной установки блок 2 устанавливает на своих выходах соответствующие сигналы, обеспечивающие реализацию тестовой программы, в которой генератор 9 псевдослучайных кодов не принимает участия, так как на регистр 34 сдвига не поступают импульсы сдвига от элемента И 13, закрытого блоком 2. По окончании тестовой программы начинается этап получения обобщенной сигнатуры. К этому моменту на пятом выходе генератора 9 псевдослучайных кодов блоком 2 управления установлен сигнал разрешения, а на четвертом входе - сигнал запрета. При поступлении импульсов сдвига с выхода элемента И 13 на регистр 34 сдвига начинается процесс сжатия информации, поступающей с выхода г) -го генератора 3 псевдослучайных кодов. При этом информация поступает на третий вход сумматора 35, где складывается с информацией, поступающей с выходов

регистра 34. С выхода сумматора 35 преобразованная информация поступает Ч:гг,ез открытьй блоком 2 элемент И 38 и элемент ИЛИ 36 на первый вход регистра 34 сдвига.

5 С выхода h -го генератора 3 псевдослучайных кодов информация транспортируется через элемент И 41 и элемент ИЛИ 37 на второй вход элемента И 6 первого генератора 3 псевдослучайных кодов.

В режиме локализации неисправности с точностью до внешнего вывода контролируемого блока от блока 2 управления на пятый вход генератора 9

5 псевдослучайных кодов поступает сигнал запрета, а на четвертый вход сигнал разрешения. При поступлении импульсов сдвига от элемента 13 в регистр 34 сдвига через открытый блог

ком 2 управления элемент И 39 и элемент 36 на вход регистра 34 сдвига поступает информация с выхода h -го генератора 3 псевдослучайных кодов. Информа1щя с последнего разряда регистра 34 сдвига через элемент И 40 и элемент И 37 поступает на элемент 6 первого генератора 3 псевдослучайных кодов.

Таким образом, введение трех (16, 36 и 37) элементов ИЛИ, семи (17, 19, 20, 38, 39, 40 и 41) элементов И, второго и третьего счетчиков, третьего переключателя, четвертого триггера и второго блока индикации позволяет формализовать процесс контроля логических блоков, представив его в .виде двух этапов: определение исправности контролируемого

блока и поиск места неисправности с точностью до внешнего вывода контролируемого логического блока. Такой подход позволяет упростить процесс контроля и увеличить глубину контроля логических блоков, содержащих несколько десятков выходов, что в конечном счете приводит к уменьшению времени, требуемого на поиск неисправности.

Сриг. 1

26

r

15

Л

Ц

28

19

16

-4Q

24

20

27

JO

На 9

На 5

29

На 6,73

LKJ

На8.9

Фиг.2

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля логических блоков | 1979 |

|

SU875390A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-07—Публикация

1983-09-23—Подача