1

Изобретение относится к технике связи и может быть использовано для регенерации цифровых сигналов в кабельных линиях.

Целью изобретения является расширение вида регенерируемых сигналов .

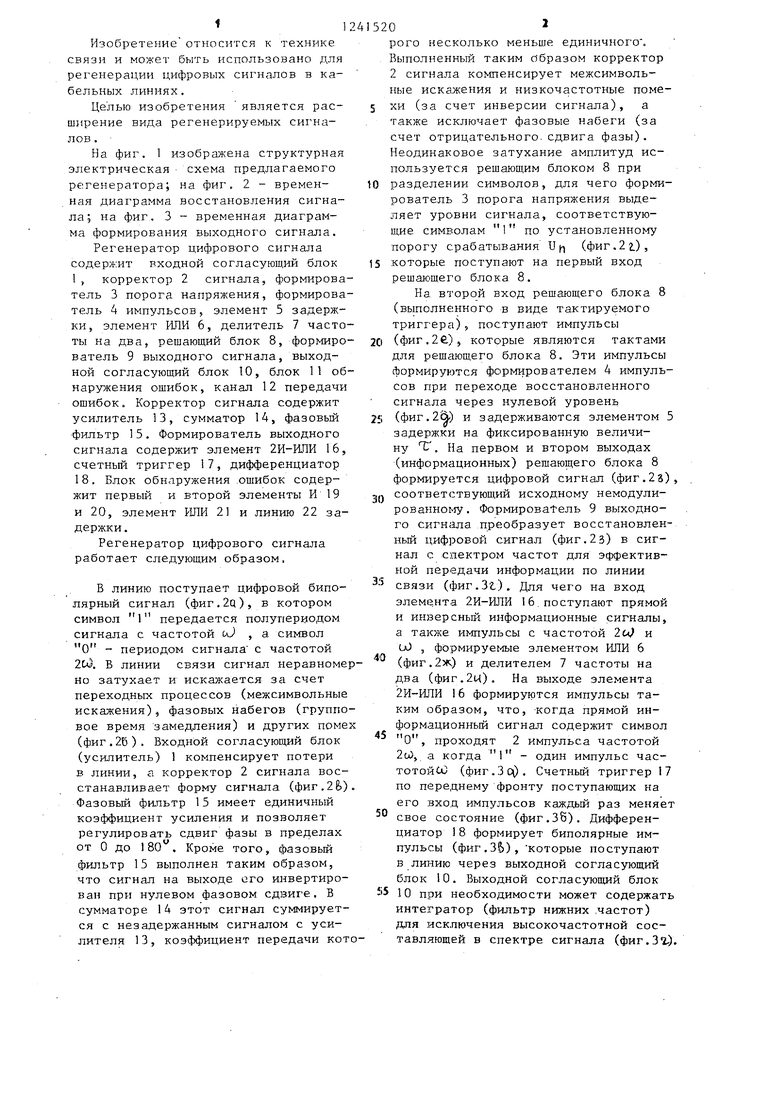

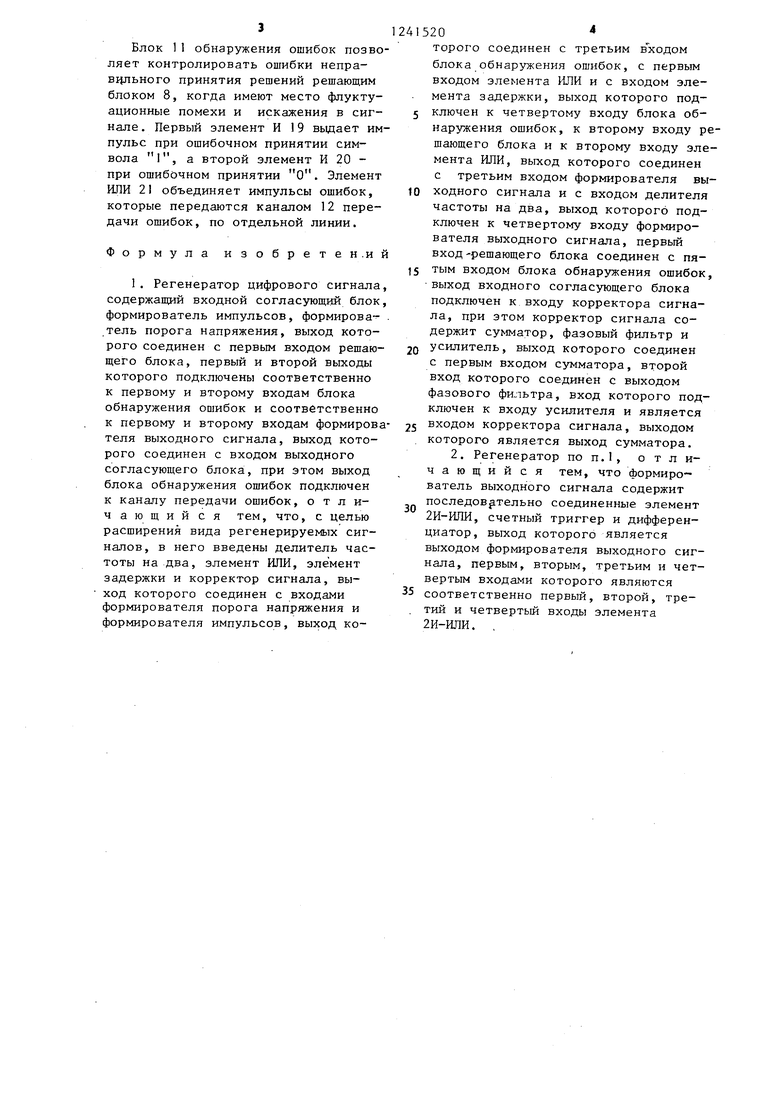

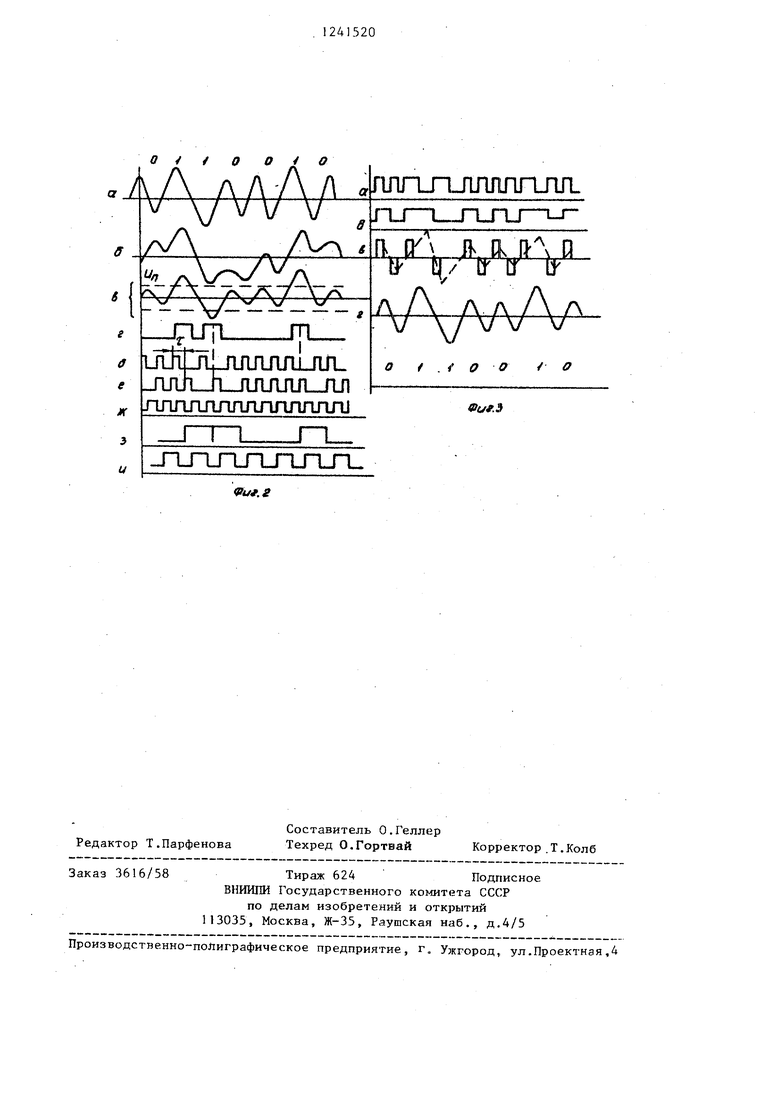

На фиг. 1 изображена структурная электрическая схема предлагаемого регенератора; на фиг, 2 - временная диаграмма восстановления сигнала; на фиг. 3 - временная диаграмма формирования выходного сигнала.

Регенератор цифрового сигнала содержит входной согласующий блок 1, корректор 2 сигнала, формирователь 3 порогэ- напряжения, формирователь 4 импульсов, элемент 5 задержки, элемент ИЛИ 6, делитель 7 частоты на два, решающий блок 8, формирователь 9 выходного сигнала, выходной согласующий блок 10, блок П обнаружения ошибок, канал 12 передачи ошибок. Корректор сигнала содержит усилитель 13, сумматор 14, фазовый фильтр 15. Формирователь выходного сигнала содержит элемент 2И-ИЛИ 16, счетный триггер 17, дифференциатор 18 , Блок обнаружения .ошибок содержит первый и второй элементы И 19 и 20, элемент ИЛИ 21 и линию 22 задержки.

Регенератор цифрового сигнала работает следующим образом,

В линию поступает цифровой биполярный сигнал (фиг.2с1), в котором символ 1 передается полупериодом сигнала с частотой , а символ О - периодом сигнала с частотой 2(м. В линии связи сигнал неравномерно затухает и искажается за счет переходных процессов (межсимвольные искажения), фазовых набегов (групповое время замедления) и других помех (фиг.26). Входной согласующий блок (усилитель) 1 компенсирует потери в линии, а корректор 2 сигнала восстанавливает форму сигнала (фиг, 2)) Фазовый фильтр 15 имеет единичный коэффициент усиления и позволяет регулировать сдвиг фазы в пределах от О до 80 . Кроме того, фазовый фильтр 15 выполнен таким образом, что сигнал на выходе его инвертирован при нулевом фазовом сдвиге, В сумматоре 14 этот сигнал суммируется с незадержанным сигналом с усилителя 13, коэффициент передачи кот5202

рого несколько меньше единичного . Выполненный таким о бразом корректор 2 сигнала компенсирует межсимвольные искажения и низкочастотные поме- хи (за счет инверсии сигнала), а также исключает фазовые набеги (за счет отрицательного, сдвига фазы). Неодинаковое затухание амплитуд используется решающим блоком 8 при разделении символов, для чего формирователь 3 порога напряжения выделяет уровни сигнала, соответствую- 1дие символам 1 по установленному порогу срабатывания U (фиг.20, 5 которые поступают на первый вход решающего блока 8.

На. второй вход решающего блока 8 (выполненного в виде тактируемого триггера), поступают импульсы 0 (фиг,26.) 5 которые являются тактами для решающего блока 8. Эти импульсы формируются формирователем 4 импульсов при переходе восстановленного сигнала через нулевой уровень f; (фиг.2Й ) и задерживаются элементом 5 задержки на фиксированную величину . На первом и втором выходах (информационных) решающего блока 8 формируется цифровой сигнал (фиг.2з), lj соответствующий исходному немодули- poBaHHOi-jy. ФормироваФель 9 выходного сигнала преобразует восстановленный цифровой сигнал (фиг.2з) в сигнал с спектром частот для эффективной передачи информации по линии - связи (фиг.З г.), Для чего на вход элемента 2И-ИЛИ 16.поступают прямой и инверсный информационные сигналы, а также импульсы с частотой 2W и Ы , формируег 1е элементом ИЛИ 6 (фиг.2ж,) и делителем 7 частоты на два (фиг.2ц). На выходе элемента 2И-ИЛИ 16 формируются импульсы таким образом, что, -когда прямой информационный сигнал содержит символ О, проходят 2 импульса частотой 2а), а когда 1 - один импульс час- тотойСО (фиг.ЗсО. Счетный триггер 17 по переднему фронту поступающих на его вход импульсов каждый раз меняет свое состояние (фиг.36). Дифференциатор 18 формирует биполярные импульсы (фиг.З)), которые поступают в линию через выходной согласующий блок 10. Выходной согласующий блок - 5 10 при необходимости может содержать интегратор (фильтр нижних .частот) ;и1я исключения высокочастотной составляющей в спектре сигнала (фиг.Зг).

3

Блок 11 обнаружения ошибок позволяет контролировать ошибки непра- вчльного принятия решений решающим блоком 8, когда имеют место флукту- ационные помехи и искажения в сигнале . Первый элемент И 19 выдает импульс при ошибочном принятии символа I, а второй элемент И 20 - при ошибочном принятии О. Элемент ИЛИ 21 объединяет импульсы ошибок, которые передаются каналом 12 передачи ошибок, по отдельной линии.

Формула изобрете н.и

1, Регенератор цифрового сигнала содержаШгИЙ входной согласующий блок формирователь импульсов, формирова- тель порога напряжения, выход которого соединен с первым входом решающего блока, первый и второй выходы которого подключены соответственно к первому и второму входам блока обнаружения ошибок и соответственно к первому и второму входам формировтеля выходного сигнала, выход которого соединен с входом выходного согласующего блока, при этом выход блока обнаружения ошибок подключен к каналу передачи ошибок, отличающийся тем, что, с целью расширения вида регенерируемых сигналов, в него введены делитель частоты на два, элемент ИЛИ, элемент задержки и корректор сигнала, выход которого соединен с входами формирователя порога напряжения и формирователя импульсов, выход ко41520

торого соединен с третьим в ходом блока обнаружения ошибок, с первым входом элемента ИЛИ и с входом элемента задержки, выход которого под- 5 ключей к четвертому входу блока обнаружения ошибок, к второму входу решающего блока и к второму входу элемента ИЛИ, выход которого соединен с третьим входом формирователя вы10 ходного сигнала и с входом делителя частоты на два, выход которого подключен к четвертому входу формирователя выходного сигнала, первый вход-решающего блока соединен с тым входом блока обнаружения ошибок, выход входного согласующего блока подключен к входу корректора сигнала, при этом корректор сигнала содержит сумматор, фазовый фильтр и

2Q усилитель, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом фазового фильтра, вход которого подключен к входу усилителя и является

25 входом корректора сигнала, выходом которого является выход сумматора.

2, Регенератор по п.I, отличающийся тем, что формирователь выходного сигнала содержит последовательно соединенные элемент 2И-ИЛИ, счетный триггер и дифференциатор, выход которого является выходом формирователя выходного сигнала, первым, вторым, третьим и четвертым входами которого являются

35 соответственно первый, второй, тре- . тий и четвертый входы элемента 2И-ИЛИ. ,

30

О / О 010

I

л

V

а

rШГLЛJШЛLГlГLЛJL

в

АО .

UJruTi

in

ллгшлляллллплш

п

J J-UTTLrLTLrL

fl, У. а Gk №Л Р

tr СГ LK

о f . f о о о

9uf.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Регенератор цифрового биполярного сигнала | 1985 |

|

SU1415456A1 |

| Приемник цифрового линейного сигнала | 1986 |

|

SU1462509A1 |

| Приемник цифрового биполярного сигнала | 1985 |

|

SU1305889A1 |

| Устройство для дуплексной цифровой связи | 1986 |

|

SU1408537A1 |

| Система для передачи цифровой информации по проводным каналам связи | 1985 |

|

SU1256233A1 |

| Система передачи дискретной информации | 1976 |

|

SU688082A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| Устройство для приема дискретных сигналов | 1986 |

|

SU1374444A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

Изобретение относится к технике связи. Расширяется вид регенерируемых сигналов. Устройство содержит входной согласующий блок 1, формирователь порога напряжения 3, формирователь импульсов 4, решающий блок 8, формирователь выходного сигнала 9, выходной согласующий блок 10, блок обнаружения ощибок 1I, канал передачи ошибок 12. Цель достигается введением делителя частоты на два 7, элемента ИЛИ 6, элемента задержки 5, корректора сигнала 2. По п.2 формулы формирователь выходного сигиала содержит элемент 2 И--ИЛИ 16, счетный триггер 17, дифференциатор 18. I з.п. ф-лы, 3 ил. (Л СП to

Редактор Т.Парфенова

Составитель О.Геллснр

Техред О.Гортвай Корректор.Т.Колб

Заказ 3616/58

Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г„ Ужгород,, ул.Проектная ,4

| Устройство оптимального регенератора | 1974 |

|

SU641841A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Оптимальный регенератор | 1974 |

|

SU583697A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-06-30—Публикация

1985-01-02—Подача