нение их уровней с пороговым, многократное последовательное преобразование, во время каждого из которых каждый импульс входной последовательности задерживают на разное число тактов. При этом в-К-м такте пре- образования (1-2)-й импульс дважды задерживают на один такт; (1.-1)-й импульс задерживают на один такт. 1--Й импульс не задерживают. Произво.«

Изобретение бтносится к электроизмерительной и импульсной технике и предназначено для подавления влияния помех в трактах преобразования младших разрядов цифровых измерительных устройств.

Цель изобретения уменьшение времени преобразования выходной последовательности импульсов и повышение помехоустойчивости.

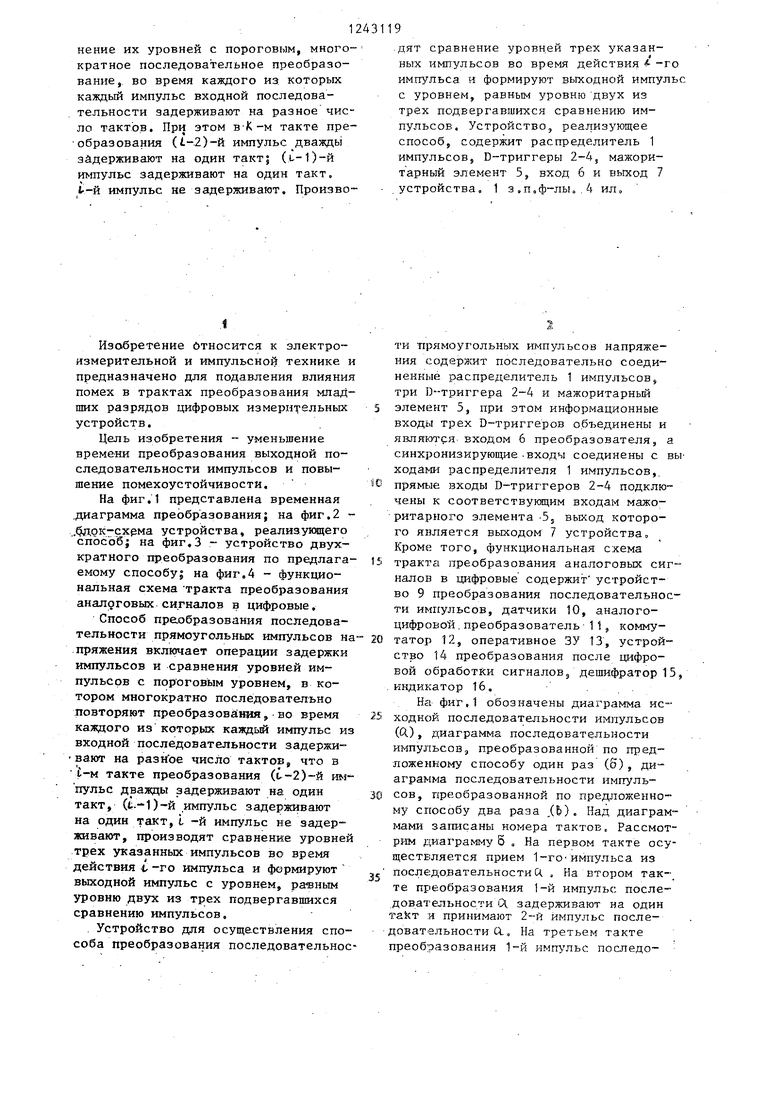

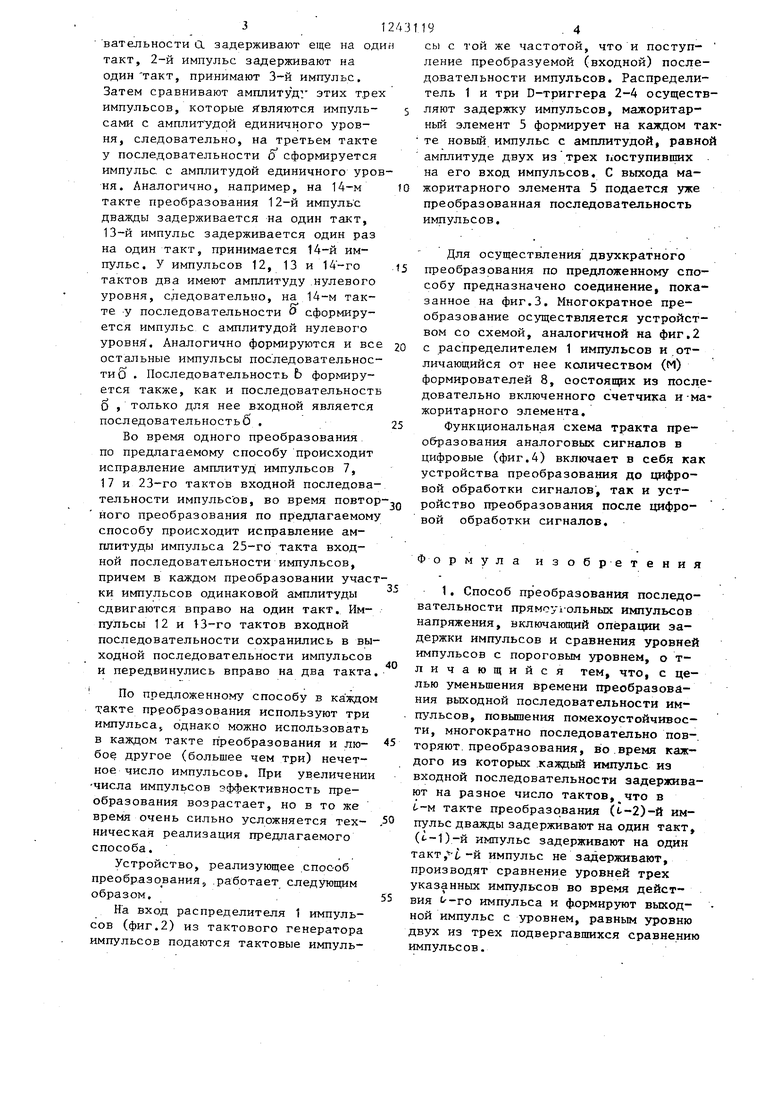

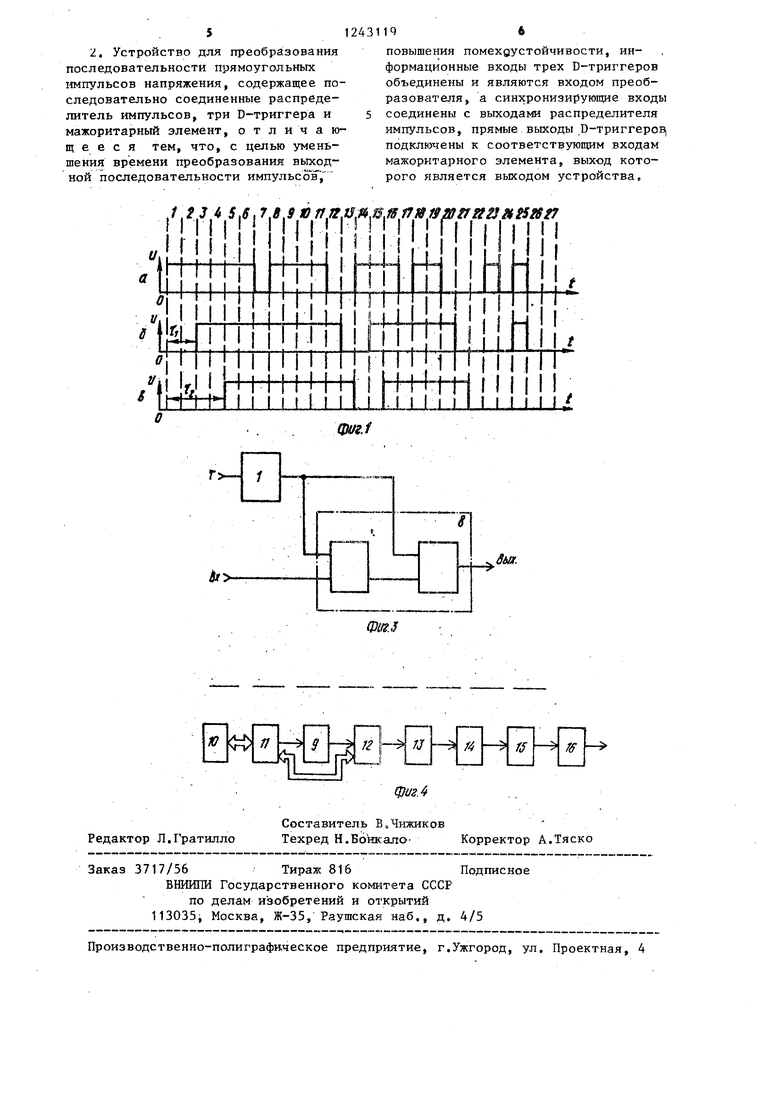

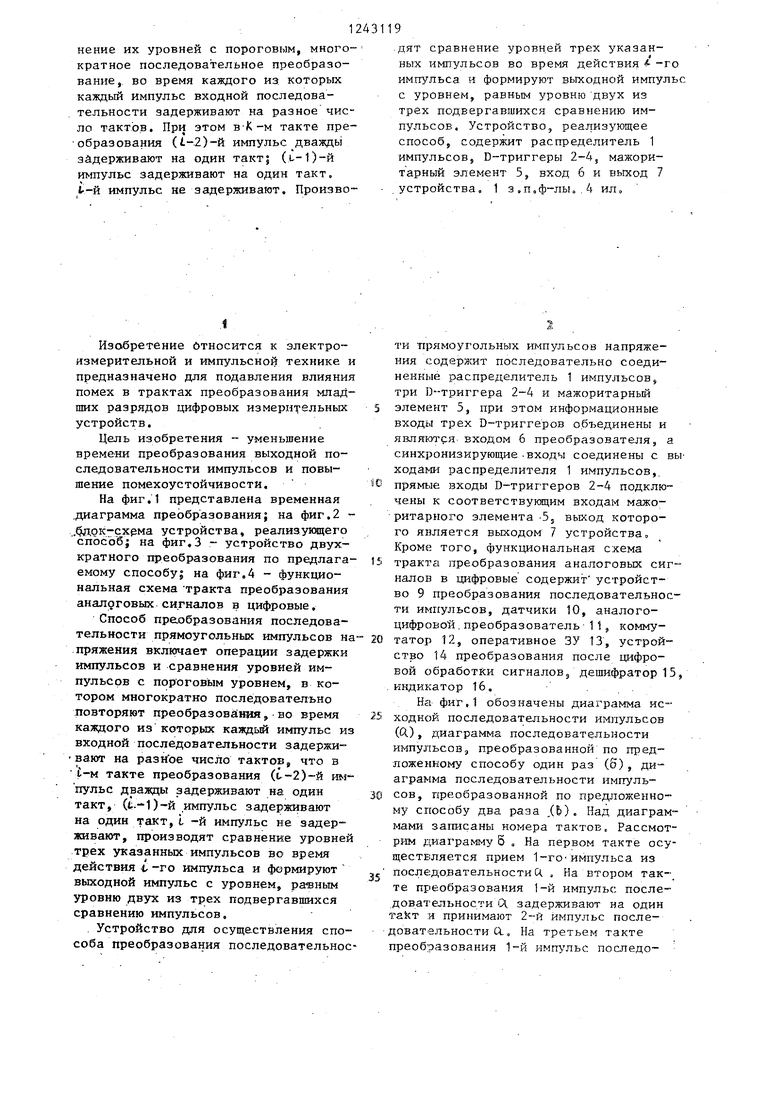

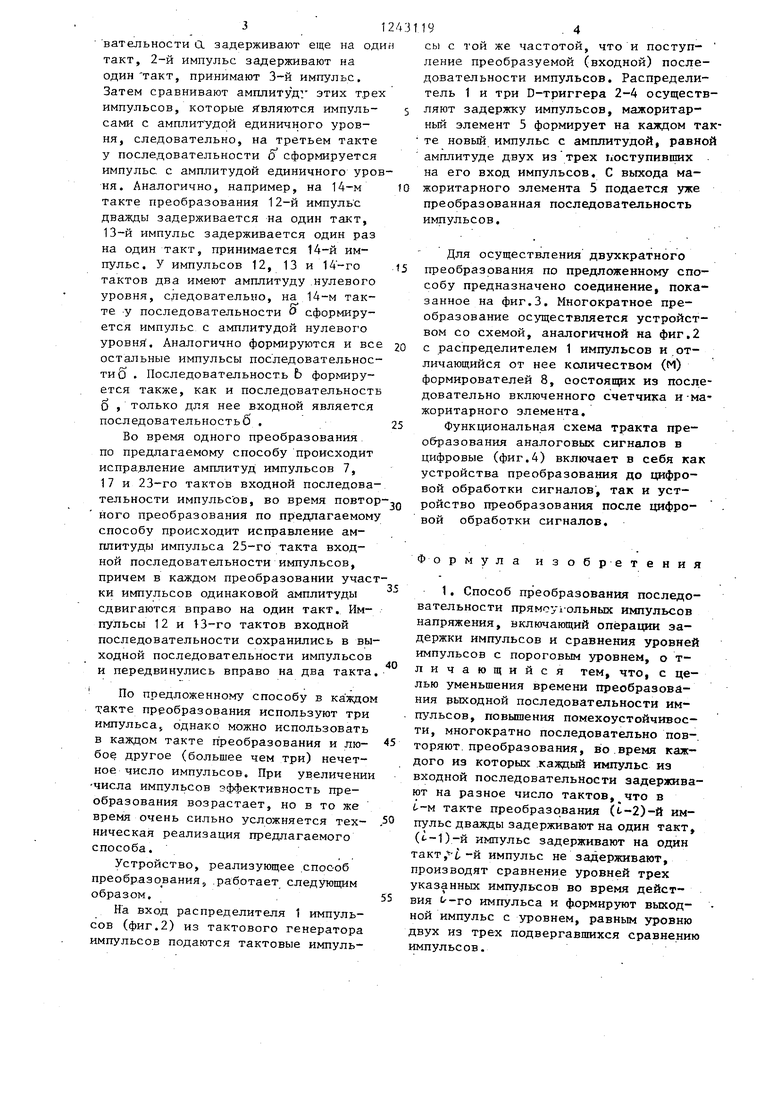

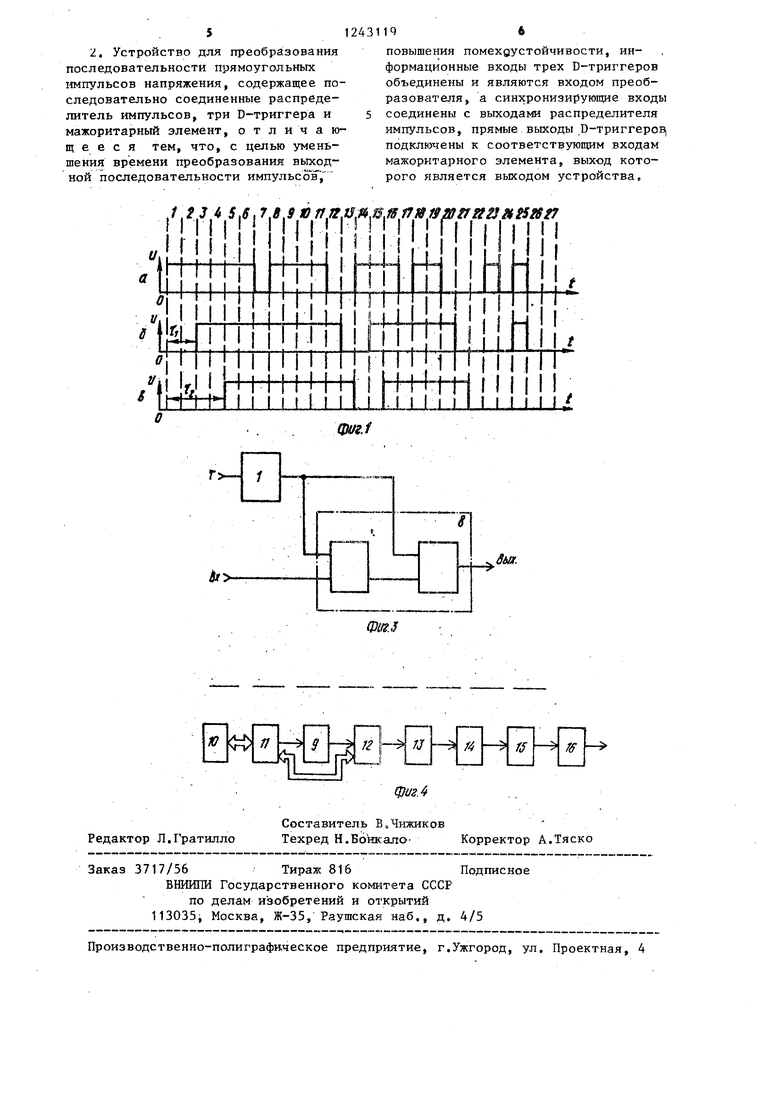

На фиг.1 представлена временная .диаграмма преобразования; на фиг.2 - ..фт,ок-схэма устройства, реализутацего способ; на фиг.З - устройство двухкратного преобразования по предлагаемому способу; на фиг.4 - функциональная схема тракта преобразования аналоговых сигналов в цифровые.

Способ преобразования последовательности прямоугольных импульсов напряжения включает операции задержки импульсов и сравнения уровней импульсов с пороговым уровнем, в котором многократко последовательно повторяют преобразования, во время каждого из которых каждый импульс из входной последовательности задержи- вают на разное число тактов, что в t-M такте преобразования (-2)-й пульс дважды задерживают на один такт, (с.-1)-й импульс задерживают на один такт, I -и импульс не задерживают, производят сравнение уровней трех указанных импульсов во время действия t-го импульса и формируют выходной импульс с уровнем, равным уровню двух из трех подвергавшихся сравнению импульсов.

. Устройство для осуществления способа преобразования последовательнос-дят сравнение уровней трех указанных импульсов во время действия -го импульса и формируют выходной импуль с уровнем, равным уровню двух из трех подвергавшихся сравнению импульсов;. Устройство, реализующее способ, содержит распределитель 1 импульсов, D-триггеры 2-4, мажоритарный элемент 5, вход 6 и выход 7 устройства, 1 з,п,ф-ль.,4 ил„

ти прямоугольных импульсов напряжения содержит последовательно соединенные распределитель 1 импульсов, три 1)триггера 2-4 и мажоритарный

элемент 5, при этом информационные входы трех D-триггеров объединены и являьэтрЯ входом 6 преобразователя, а синхронизирующие.входы соединены с вы- распределителя 1 импульсов,.

прямые входы D-триггеров 2-4 подключены к соответствукщим входам мажо- ритарного элемента -Sj выход которого является выходом 7 устройства, Кроме того, функциональная схема

тракта преобразования аналоговых сигналов в цифровые содержит устройство 9 преобразования последовательности импульсов, датчики 10, аналого- цифровой .преобразователь-11, коммутатор 12, оперативное ЗУ 13, устройство 14 преобразования после цифровой обработки сигналов, дешифратор 15, . индикатор 16. - . .

На фиг,1 обозначены диах рамма исходкой последовательности импульсов (ft.), диаграмма последовательности импульсоВэ преобразованной по предложенному способу один раз (S), диаграмма последовательности импульсов, преобразованной по предложенному способу два раза .(&) Над диаграммами за1шсаны номера тактов. Рассмотрим диаграмму 6 , На первом такте осуществляется прием 1-ГО импульса из

последо.вательн:остиС , На втором так-- те преобразования 1-й импульс последовательности Л задерживают на один TakT н принимают 2-й импульс последовательности Ci, На третьем такте преобразования 1-й импульс последо31

вательности CL задерживают еще на оди такт, 2-й импульс задерживают на один такт, принимают 3-й импульс. Затем сравнивают амплитуду этих трех импульсов, которые являются импуль- сами с амплитудой единичного уровня, следовательно, на третьем такте у последовательности ё сформируется импульс с амплитудой единичного уровня. Аналогично, например, на 14-м такте преобразования 12-й импуль с дважды задерживается на один такт, 13-й импульс задерживается один раз на один такт, принимается 14-й импульс, У импульсов 12, 13 и 14 -го тактов два имеют амплитуду нулевого уровня, следовательно, на 14-м такте -у последовательности О сформируется импульс с амплитудой нулевого уровня . Аналогично формируются и все остальные импульсы последовательности б . Последовательность Ь формируется также, как и последовательность б , только для нее входной является последовательность б ,

Во время одного преобразования по предлагаемому способу происходит испра.вление амплитуд импульсов 7, 17 и 23-го тактов входной последовательности импульсов, во время повтор ного преобразования по предлагаемому способу происходит исправление амплитуды импульса 25-го такта входной последовательности импульсов.

причем в каждом преобразовании участки импульсов одинаковой амплитуды сдвигаются вправо на один такт. Импульсы 12 и 13-го тактов входной последовательности сохранились в выходной последовательности импульсов и передвинулись вправо на два такта.

По предложенному способу в ка ждо такте преобразования используют три импульса5 однако можно использовать в каждом такте преобразования и лю- бое другое (большее чем три) нечетное число импульсов. При увеличени числа импульсов эффективность преобразования возрастает, но в то же время очень сильно усложняется тех- ническая реализация предлагаемого способа.

Устройство, реализующее .способ преобразования, .работает следующим образом,,

На вход распределителя 1 импульсов (фиг,2) из тактового генератора импульсов подаются тактовые импуль

5 Ш 15 20 5

-

5

0

19.4

сы с той же частотой, что и поступ- ление преобразуемой (входной) последовательности импульсов. Распределитель 1 и три D-триггера 2-4 осуществляют задержку импульсов, мажоритар ньй элемент 5 формирует на каждом такте новый импульс с амплитудой, равной амплитуде двух из трех поступивших на его вход импульсов, С выхода мажоритарного элемента 5 подается уже преобразованная последовательность импульсов.

Для осуществления двухкратного преобразования по предложенному способу предназначено соединение, показанное на фиг,3. Многократное преобразование осуществляется устройством со схемой, аналогичной на фиг,2 с распределителем 1 импульсов и отличающийся от нее количеством (М) формирователей 8, состоящих из последовательно включенного счетчика и-мажоритарного элемента.

Функциональная схема тракта преобразования аналоговых сигналов в цифровые (фиг,4) включает в себя как устройства преобразования до цифровой обработки сигналов, так и устройство преобразования после цифровой обработки сигналов.

Формула изобретения

1, Способ преобразования последовательности прямоугольных импульсов напряжения, включающий операции задержки импульсов и сравнения уровней импульсов с пороговым уровнем, о т- личающийся тем, что, с целью уменьшения времени преобразования выходной последовательности импульсов, повышения помехоустойчивости, многократно последовательно пов-. торяют. преобразования, во.время каждого из которых .каждый импульс из входной последовательности задерживают на разное число тактов, что в i-u такте преобразования (-2)-й импульс дважды задерживают на один такт, (--1)-й импульс задерживают на один такт,.-й импульс не задерживают, производят сравнение уровней трех указанных импульсов во время действия t -ro импульса и формируют вькод- ной импульс с уровнем, равным уровню двух из трех подвергавшихся сравнению импульсов.

5

2. Устройство для преобразования последовательности прямоугольных импульсов напряжения, содержащее последовательно соединенные распределитель импульсов, три D-триггера и мажоритарный элемент, отличающееся тем, что, с цепью уменьшения времени преобразования выходной последовательности импульссГв,

1,23 4 5,Г, 7 8.9 Ю 111tJSM,n,Wff№19EBlffg2S K№

iq6

повышения помехдустойчивости, информационные входы трех D-триггеров объединены и являются входом преоб- разовател1я, а синхронизирующие входы соединены с выходами распределителя импульсов, прямые выходы В-триггероВ| подклнзчены к соответствующим входам мажоритарного элемента, выход которого является выходом устройства

фог.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ преобразования последовательностей прямоугольных импульсов и устройство для его осуществления | 1990 |

|

SU1723660A1 |

| Способ преобразования последовательностей прямоугольных импульсов и устройство для его осуществления | 1988 |

|

SU1622931A1 |

| Элемент однородной вычислительной структуры | 1984 |

|

SU1211890A1 |

| Ультразвуковой дефектоскоп | 1989 |

|

SU1619169A1 |

| Резервированное счетное устройство | 1986 |

|

SU1350830A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО СИГНАЛА В ПЯТИУРОВНЕВЫЙ СИГНАЛ | 2010 |

|

RU2428787C1 |

| Устройство для преобразования последовательности импульсов | 1988 |

|

SU1624673A1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| Ультразвуковой дефектоскоп | 1988 |

|

SU1627974A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1478330A1 |

Изобретение предназначено для подавления помех в трактах преобразования младших разрядов цифровых измерительных устройств. Цель изобретения - повышение помехоустойчивости и уменьшение времени преобразования выходной последовательности импульсов. Способ включает следующие операции: задержку импульсов, сравtC СО 1г бьиг. 7 ;о

Редактор Л.Гратилло

(игЛ

Составитель В.Чижиков

Техред Н.Ббш.ало- Корректор А.Тяско

Заказ 3717/56Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам и зобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

| Новицкий П.В | |||

| Основы информационной теории измерительных устройств | |||

| Л.: Энергия, 1968, с | |||

| Прибор для записи звуковых волн | 1920 |

|

SU219A1 |

| Гришина Ю.П | |||

| и др | |||

| Микропроцессоры в радиотехнических системах | |||

| М.: Радио, 1982, с.120-125. | |||

Авторы

Даты

1986-07-07—Публикация

1983-11-09—Подача