последовательности k-го разряда не производят;

6)сравнивают (i - 2)-й, (i - 1)-й, i-й импульсы входной последовательности k-ro разряда;

7)формируют i-й импульс выходной последовательности k-ro разряда;

8)корректируют (заменяют) один из уровней импульсов (i - 2)-го, (i - 1)-го или i-ro тактов входной последовательности (k - 1)-го разряда по четвертой или пятой операции способа.

Операции задержки (i - 2)-го, (i - 1)-го и приема i-ro импульсов осуществляются для всех М входных последовательностей синхронно во времени и заканчиваются до сравнения уровней импульсов (i - 2)-го, (i - 1)-го, i-ro тактов входной последовательности самого старшего М-ro разряда.

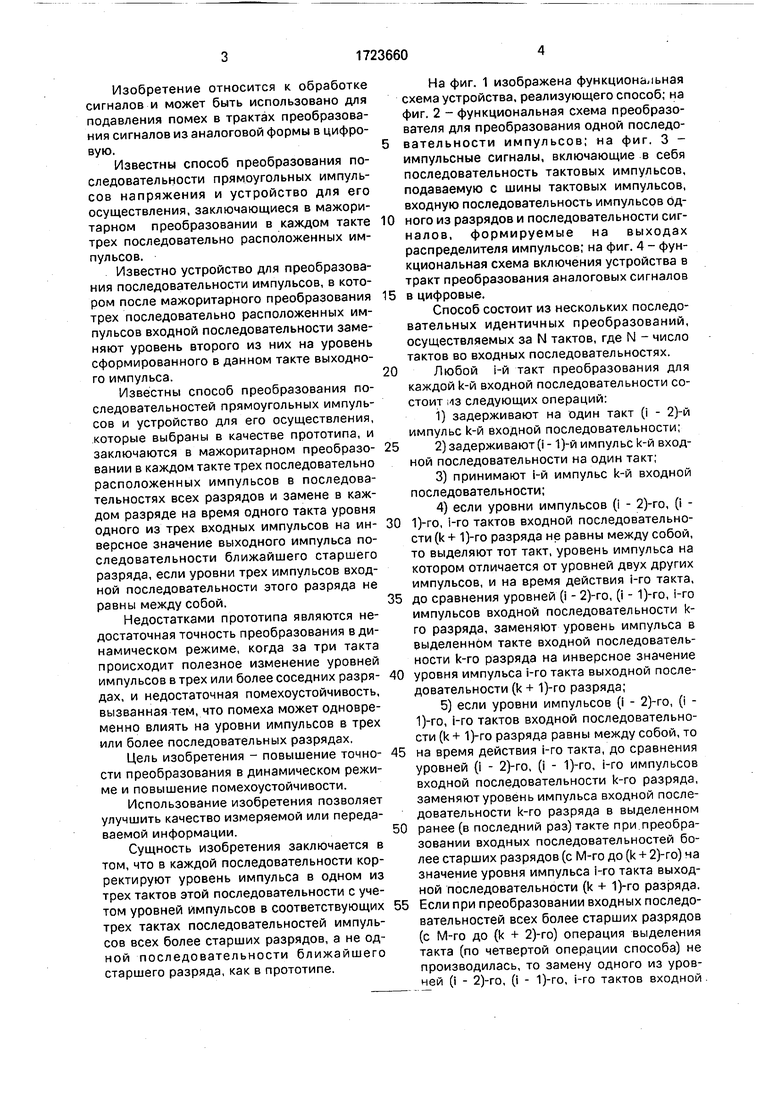

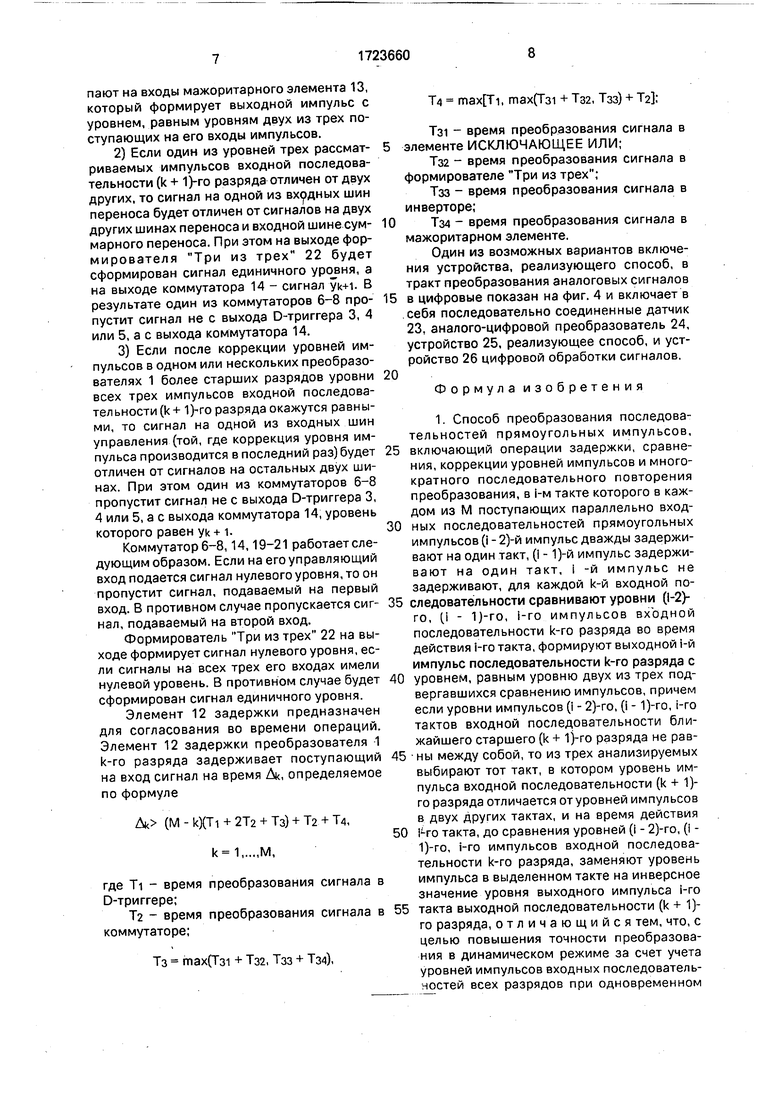

Устройство для осуществления способа приведено на фиг. 1 и состоит из М идентичных преобразователей 1, каждый из которых используется для преобразования лишь одной последовательности импульсов и располагается в одном разряде.

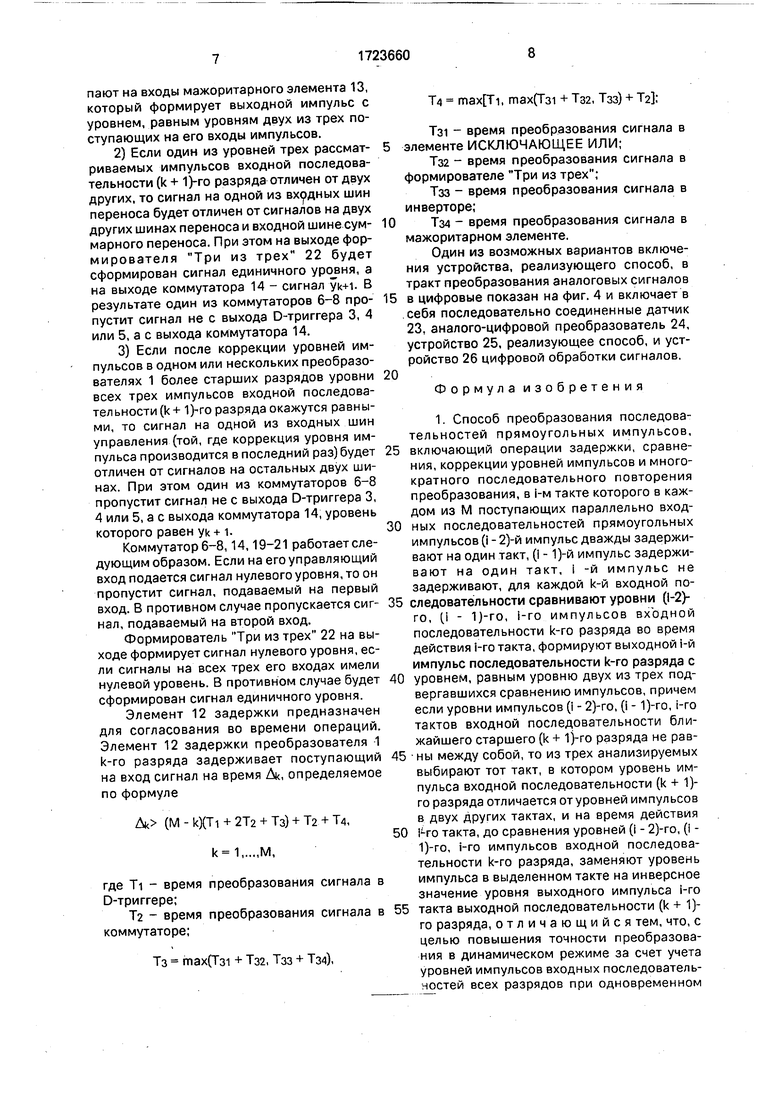

В преобразователе 1 k-ro разряда, приведенном на фиг. 2, распределитель 2 импульсов своими первыми тремя выходами соединен с соответствующими синхронизирующими входами (С-входы) трех D-тригге- ров 3-5, информационные входы (D-входы) которых объединены и являются входом преобразователя 1, соединенным с. информационной шиной Xk. Вход распределителя 2 импульсов соединен с шиной Т тактовых импульсов. Прямые выходы D-триггеров 3-5 соединены с первыми входами коммутаторов 6-8 соответствен но, выходы которыхсоединены с D-входзми D-триггеров 9-11. С-входы D-триггеров 9-11 объединены и соединены через элемент 12 задержки с четвертым выходом распределителя 2 импульсов. Прямые выходы D-триггеров 9- 11 соединены с соответствующими выходными шинами переноса ai, bk, Ck. Выход мажоритарного элемента 13 соединен с выходной шиной yk. Вторые входы коммутаторов 6-8 объединены и соединены с выходом коммутатора 14, второй вход которого соединен с выходом инвертора 15, а первый вход - с входной шиной суммарного переноса yk-H, которая соединена с выходной шиной преобразователя 1 ближнего старшего (k + 1)-го разряда. Входная шина суммарного переноса yk также соединена с входом инвертора 15 и с первыми1 входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 16-18, вторые входы которых соединены с соответствующими тремя входными шинами переноса ak+1, bk+1, Ck+1. Входные шины переноса

ak+1, bk+1, Ck+1 соединены с соответствующими выходными шинами переноса преобразователя 1 (k + 1)-го разряда. Выходы элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ 16-18 соединены с вторыми входами соответствующих коммутаторов 19-21 , с соответствующими входами формирователя Три из трех 22 и с соответствующими выходными шинами управления die, Ik, fk, которые

0 соединены с соответствующими входными шинами управления преобразователя 1 ближайшего младшего (k - 1)-го разряда. Выход формирователя Три из трех 22 соединен с управляющими входами коммутаторов 14,

5 19-21. Первые входы коммутаторов 19-21 соединены с соответствующими входными шинами управления dk+1, lk+1, fk-и. которые соединены с соответствующими выходными шинами управления преобразователя 1 (k +

0 1)-го разряда. Выходы коммутаторов 19-21 соединены с управляющими входами коммутаторов 6-8 соответственно. Выходная шина yk соединена с входной шиной суммарного переноса преобразователя 1 (k- 1)-го разряда.

5 Выходные шины переноса ак, bk, Ck соединены с соответствующими входными шинами переноса преобразователя 1 (k- 1)-го разряда. На три входные шины управления dv+1, 1м+1, fM+1, три входные шины переноса ам+i, Ьм+1,

0 см+1 и входную шину суммарного переноса ум-н преобразователя 1 самого старшего М-го разряда подаются сигналы нулевого уровня. Работает преобразователь 1. включенный в тракт любого k-ro разряда, следующим

5 образом.

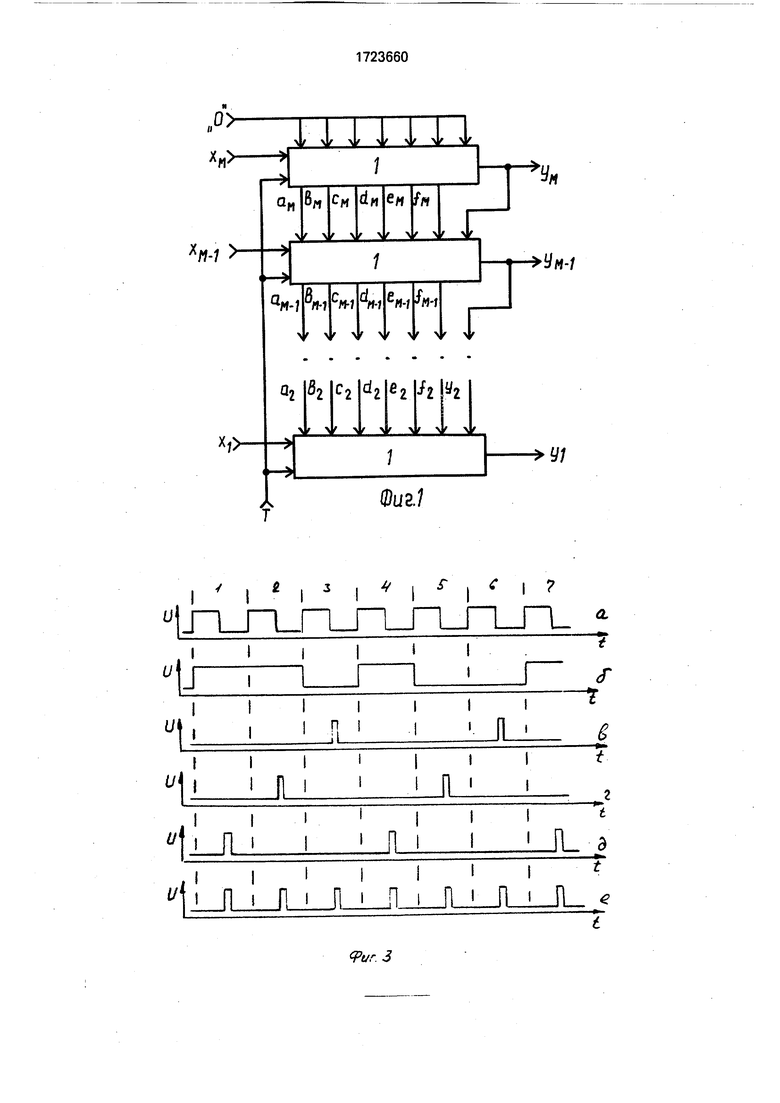

На вход распределителя 2 импульсов с шины Т тактовых импульсов подаются тактовые импульсы (фиг. За) с той же частотой, что и импульсы k-ro разряда с информационной

0 шины входной последовательности (фиг. 36). На первом-четвертом выходах распределителя 2 импульсов формируются последовательности импульсов, приведенные соответственно на фиг. Зв, г, д и е. D-триггеры

5 3-5 осуществляют задержку поступающих на их D-входы импульсов на два такта. Сигналы с выходов D-триггеров 3-5 поступают на первые входы коммутаторов 6-8. Далее преобразователь 1 может работать в трех режимах.

01) Если коррекция уровней импульсов в

преобразователях 1 более старших разрядов не проводилась ни разу, то с входных шин управления подаются сигналы нулевого уровня, а сигналы на входных шинах переноса и

5 входной шине суммарного переноса равны между собой. Сигналы с этих шин открывают первые входы коммутаторов 6-8, в результате чего они пропускают сигналы с выходов D- триггеров 3-5 на D-входы D-триггеров 9-11. С выходов D-триггеров 9-11 сигналы поступают на входы мажоритарного элемента 13, который формирует выходной импульс с уровнем, равным уровням двух из трех поступающих на его входы импульсов.

2)Если один из уровней трех рассматриваемых импульсов входной последовательности (k + разряда отличен от двух других, то сигнал на одной из входных шин переноса будет отличен от сигналов на двух других шинах переноса и входной шине суммарного переноса. При этом на выходе формирователя Три из трех 22 будет сформирован сигнал единичного уровня, а на выходе коммутатора 14 - сигнал yVn. В результате один из коммутаторов 6-8 пропустит сигнал не с выхода D-триггера З, 4 или 5, а с выхода коммутатора 14.

3)Если после коррекции уровней импульсов в одном или нескольких преобразователях 1 более старших разрядов уровни всех трех импульсов входной последовательности (k+ 1)-го разряда окажутся равными, то сигнал на одной из входных шин управления (той, где коррекция уровня импульса производится в последний раз) будет отличен от сигналов на остальных двух шинах. При этом один из коммутаторов 6-8 пропустит сигнал не с выхода D-триггера З, 4 или 5, а с выхода коммутатора 14, уровень которого равен yk + 1.

Коммутатор 6-8,14,19-21 работает следующим образом. Если на его управляющий вход подается сигнал нулевого уровня, то он пропустит сигнал, подаваемый на первый вход. В противном случае пропускается сигнал, подаваемый на второй вход.

Формирователь Три из трех 22 на выходе формирует сигнал нулевого уровня, если сигналы на всех трех его входах имели нулевой уровень. В противном случае будет сформирован сигнал единичного уровня.

Элемент 12 задержки предназначен для согласования во времени операций. Элемент 12 задержки преобразователя 1 k-ro разряда задерживает поступающий на вход сигнал на время Ak, определяемое по формуле

Ak (М - k)(Ti + 2Т2 + Тз) + Т2 + Т4, ,

где Ti - время преобразования сигнала в D-триггере;

Т2 - время преобразования сигнала в коммутаторе;

Тз тах(Тз1 + Тза, Тзз + Тзз),

Т4 тахПТт, тах(Тз1 + Тз2, Тзз) +

Тэт - время преобразования сигнала в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ;

Тз2 - время преобразования сигнала в формирователе Три из

Тзз - время преобразования сигнала в инверторе;

Тз4 - время преобразования сигнала в мажоритарном элементе.

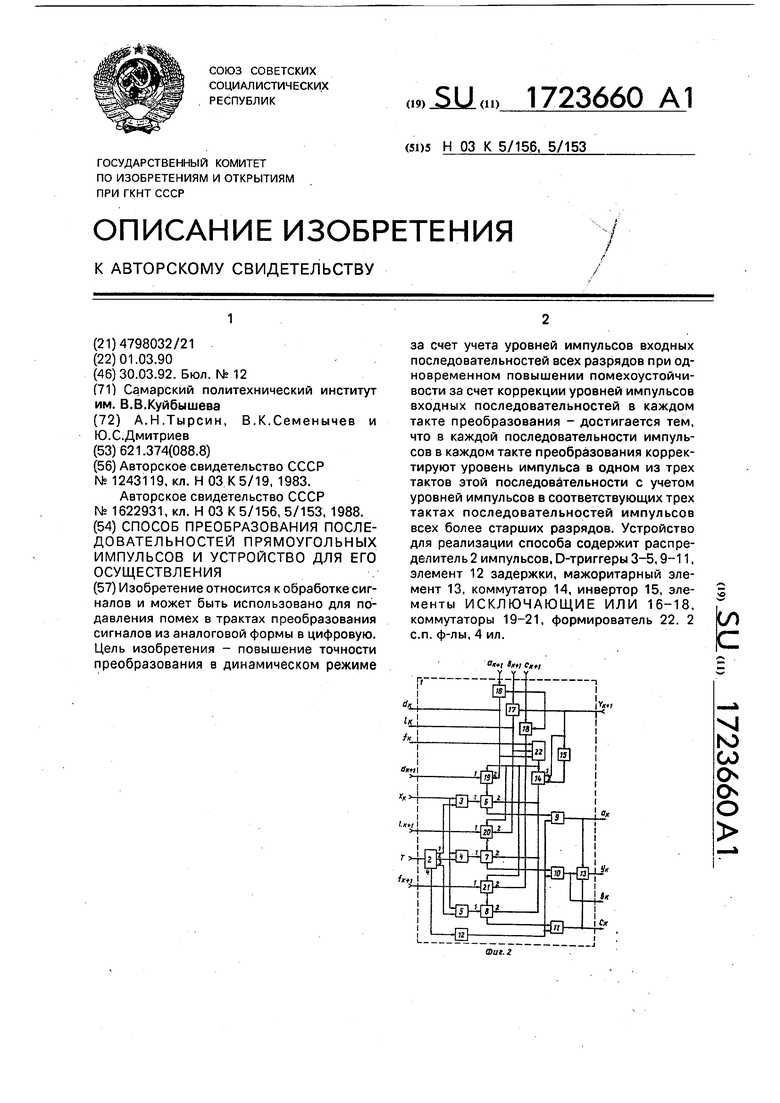

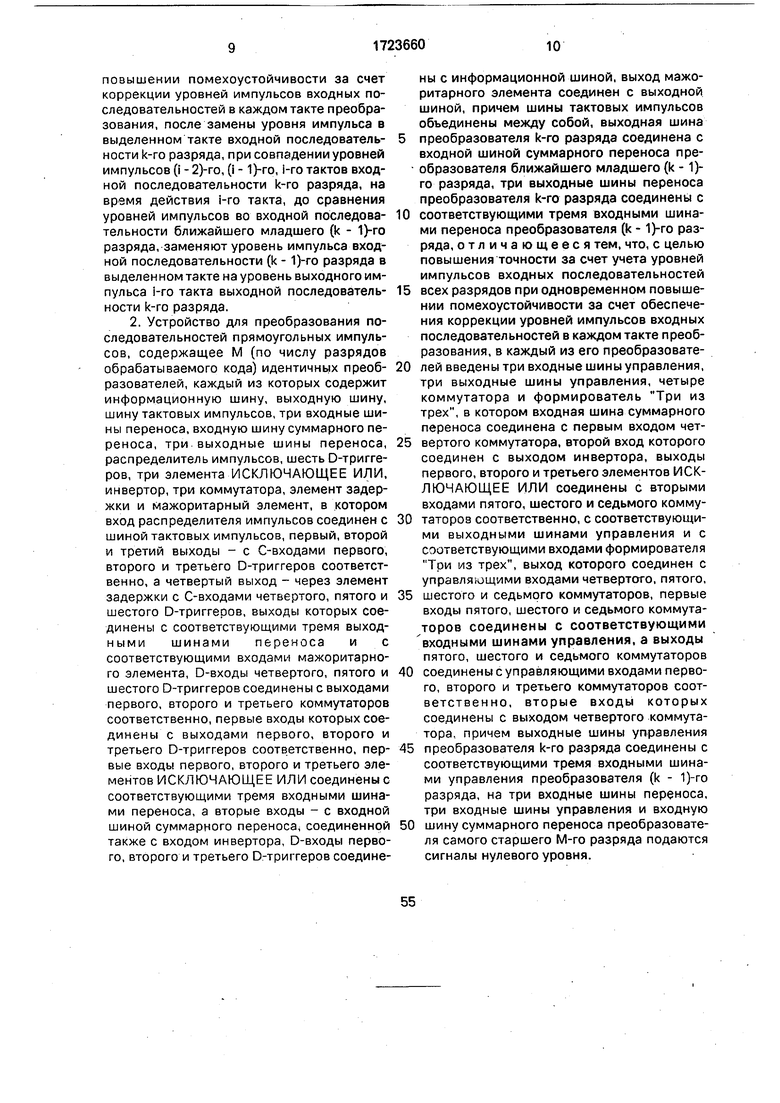

Один из возможных вариантов включения устройства, реализующего способ, в тракт преобразования аналоговых сигналов в цифровые показан на фиг. 4 и включает в себя последовательно соединенные датчик 23, аналого-цифровой преобразователь 24, устройство 25, реализующее способ, и устройство 26 цифровой обработки сигналов.

Ф о р м у л а и з о б р е т е н и я

1. Способ преобразования последовательностей прямоугольных импульсов,

включающий операции задержки, сравнения, коррекции уровней импульсов и многократного последовательного повторения преобразования, в i-м такте которого в каждом из М поступающих параллельно входных последовательностей прямоугольных импульсов (i - 2)-й импульс дважды задерживают на один такт, (i - 1)-й импульс задерживают на один такт, i -и импульс не задерживают, для каждой k-й входной последоватёльности сравнивают уровни (1-2)- го, ( - 1)-го, i-ro импульсов входной последовательности k-ro разряда во время действия i-ro такта, формируют выходной i-й импульс последовательности k-ro разряда с

уровнем, равным уровню двух из трех подвергавшихся сравнению импульсов, причем если уровни импульсов (i - 2)-го, (i - 1)-ro, i-ro тактов входной последовательности ближайшего старшего (k + 1)-го разряда не рав ны между собой, то из трех анализируемых выбирают тот такт, в котором уровень импульса входной последовательности (k + 1)- го разряда отличается от уровней импульсов в двух других тактах, и на время действия

такта, до сравнения уровней (i - 2)-го, (i - 1)-го, i-ro импульсов входной последовательности k-ro разряда, заменяют уровень импульса в выделенном такте на инверсное значение уровня выходного импульса i-ro

такта выходной последовательности (k + 1)- го разряда, отличающийся тем, что, с целью повышения точности преобразования в динамическом режиме за счет учета уровней импульсов входных последовательностей всех разрядов при одновременном

повышении помехоустойчивости за счет коррекции уровней импульсов входных последовательностей в каждом такте преобразования, после замены уровня импульса в выделенном такте входной последовательности k-ro разряда, при совпадении уровней импульсов (i - 2)-го, (i - 1)-го, 1-го тактов входной последовательности k-ro разряда, на время действия i-ro такта, до сравнения уровней импульсов во входной последовательности ближайшего младшего (k - 1)-го разряда, заменяют уровень импульса входной последовательности (k - 1)-го разряда в выделенном такте на уровень выходного импульса i-ro такта выходной последовательности k-ro разряда.

2. Устройство для преобразования последовательностей прямоугольных импульсов, содержащее М (по числу разрядов обрабатываемого кода) идентичных преобразователей, каждый из которых содержит информационную шину, выходную шину, шину тактовых импульсов, три входные шины переноса, входную шину суммарного переноса, три выходные шины переноса, распределитель импульсов, шесть D-тригге- ров, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, инвертор, три коммутатора, элемент задержки и мажоритарный элемент, в котором вход распределителя импульсов соединен с шиной тактовых импульсов, первый, второй и третий выходы - с С-входами первого, второго и третьего D-триггеров соответственно, а четвертый выход - через элемент задержки с С-входами четвертого, пятого и шестого D-триггеров, выходы которых соединены с соответствующими тремя выходными шинами переноса и с соответствующими входами мажоритарного элемента, D-входы четвертого, пятого и шестого D-триггеров соединены с выходами первого, второго и третьего коммутаторов соответственно, первые входы которых соединены с выходами первого, второго и третьего D-триггеров соответственно, первые входы первого, второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с соответствующими тремя входными шинами переноса, а вторые входы - с входной шиной суммарного переноса соединенной также с входом инвертора, D-входы первого, второго и третьего D-триггеров соединены с информационной шиной, выход мажоритарного элемента соединен с выходной шиной, причем шины тактовых импульсов объединены между собой, выходная шина

преобразователя k-ro разряда соединена с

входной шиной суммарного переноса преобразователя ближайшего младшего (k -1)го разряда, три выходные шины переноса

преобразователя k-ro разряда соединены с

соответствующими тремя входными шинами переноса преобразователя (k - 1)-го разряда, отличающееся тем, что, с целью повышения точности за счет учета уровней импульсов входных последовательностей

всех разрядов при одновременном повышении помехоустойчивости за счет обеспечения коррекции уровней импульсов входных последовательностей в каждом такте преобразования, в каждый из его преобразователей введены три входные шины управления, три выходные шины управления, четыре коммутатора и формирователь Три из трех, в котором входная шина суммарного переноса соединена с первым входом четвертого коммутатора, второй вход которого соединен с выходом инвертора, выходы первого, второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с вторыми входами пятого, шестого и седьмого коммутаторов соответственно, с соответствующими выходными шинами управления и с соответствующими входами формирователя Три из трех, выход которого соединен с управляющими входами четвертого, пятого,

шестого и седьмого коммутаторов, первые входы пятого, шестого и седьмого коммутаторов соединены с соответствующими входными шинами управления, а выходы пятого, шестого и седьмого коммутаторов

соединены с управляющими входами первого, второго и третьего коммутаторов соответственно, вторые входы которых соединены с выходом четвертого коммутатора, причем выходные шины управления

преобразователя k-ro разряда соединены с соответствующими тремя входными шинами управления преобразователя (k - 1)-го разряда, на три входные шины переноса, три входные шины управления и входную

шину суммарного переноса преобразователя самого старшего М-го разряда подаются сигналы нулевого уровня.

S.

I 7 I I

InJTLn

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ преобразования последовательностей прямоугольных импульсов и устройство для его осуществления | 1988 |

|

SU1622931A1 |

| Способ преобразования последовательности прямоугольных импульсов напряжения и устройство для его осуществления | 1983 |

|

SU1243119A1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Устройство преобразования последовательности прямоугольных импульсов напряжения | 1989 |

|

SU1721809A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1571761A1 |

| Преобразователь угол-код | 1983 |

|

SU1179528A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

и

у

iiii

u

I I

П JL

I I

I/

1

JUL

i i

tfjlJ1 i П i П i П i П

jLJL

i i

Jl

JL э

i i

i П

t

JL «

Vr J

фиг. 4

Авторы

Даты

1992-03-30—Публикация

1990-03-01—Подача