1

Изобретение относится к вычислительной технике и предназначено для синхронного деления частоты входных импульсов на 2,5 и 5.

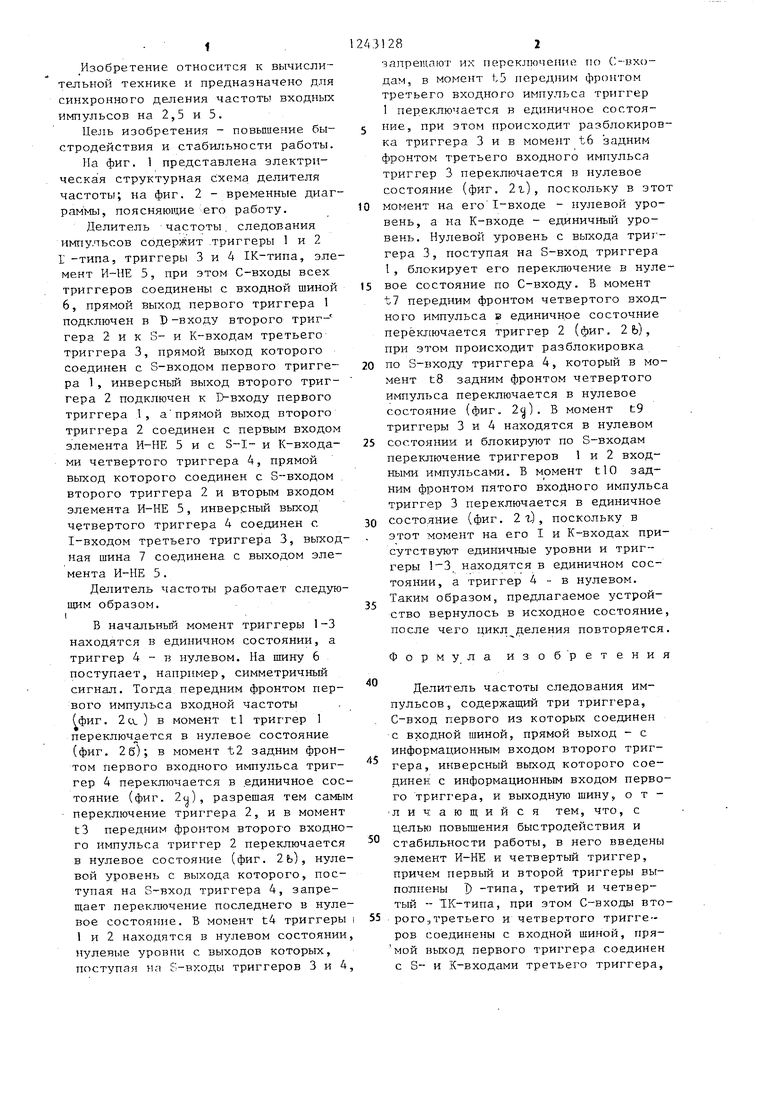

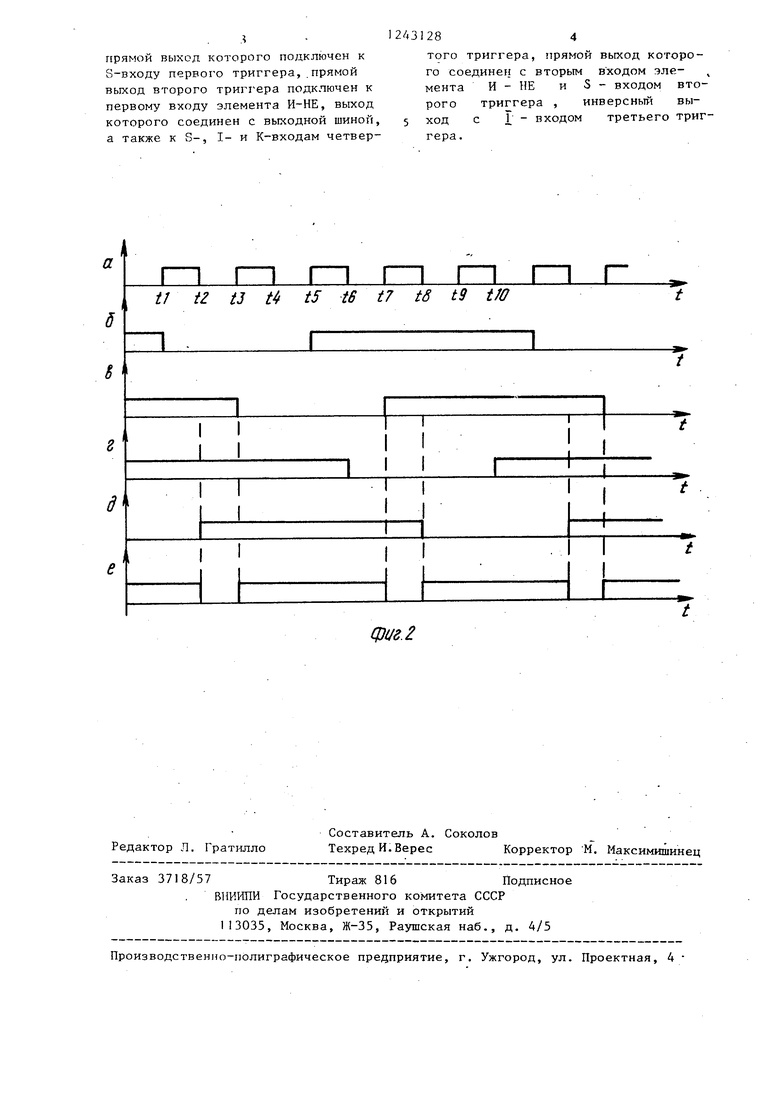

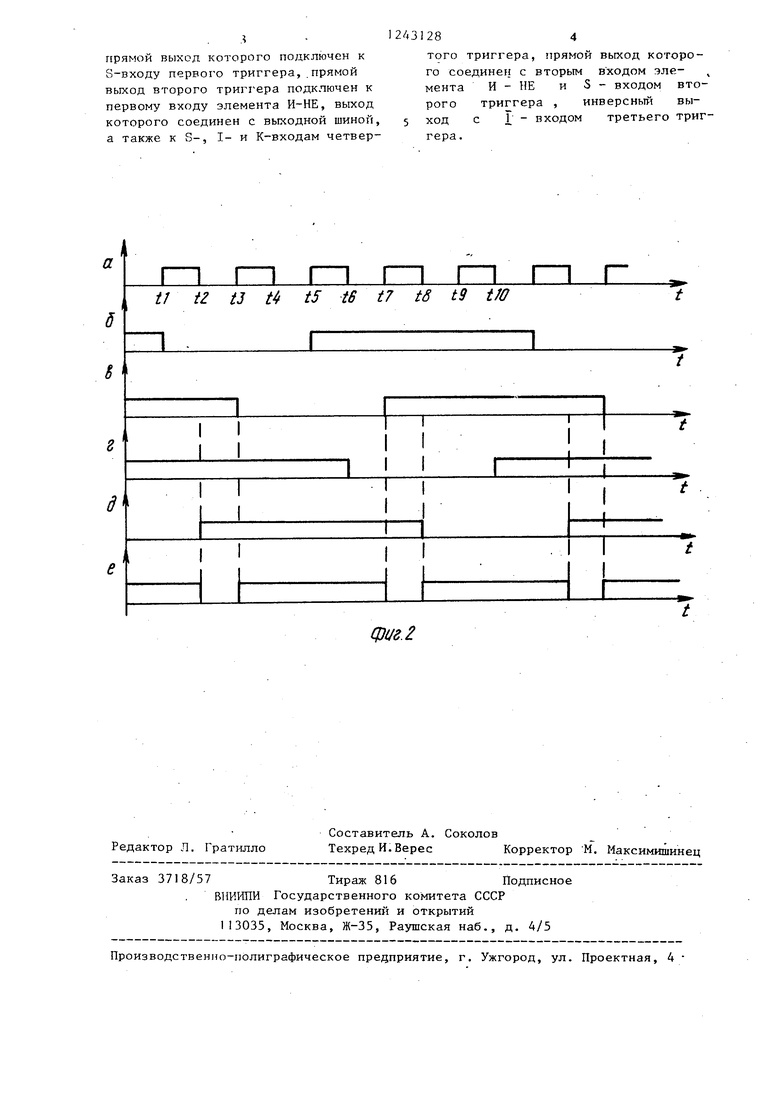

Цель изобретения - повышение быстродействия и стабильности работы. На фиг. 1 представлена электрическая структурная делителя частоты; на фиг. 2 - временные диаграммы, поясняющие его работу.

Делитель частоты. следования импульсов содерзкит .триггеры 1 и 2 Г -типа, триггеры 3 и 4 1К-типа, элемент И-НЕ 5, при этом С-входы всех Триггеров соединены с входной шиной 6, прямой выход первого триггера 1 подключен в I) -входу второго триг- гера 2 и к S- и К-входам третг:.его триггера 3, прямой выход которого соединен с S-входом первого триггера 1, инверсньй выход второго триггера 2 подключен к ГЬвходу первого триггера .1, а прямой выход второго триггера 2 соединен с первым входом элемента И-НЕ 5 и с S-I- и К-входа- ми четвертого триггера 4, прямой выход которого соединен с 5--входом второго триггера 2 и вторым входом элемента И-НЕ 5, инверсный выход четвертого триггера 4 соединен с 1-входом третьего триггера 3, выходная шина 7 соединена с выходом элемента И-НЕ 5 .

Делитель частоты работает следующим образом. I

В начальный момент триггеры 1-3

находятся в единичном состоянии, а триггер 4 - в нулевом. На шину 6 поступает, например, симметричный сигнал. Тогда передним фронтом первого импульса входной частоты (фиг. 2с.) в момент tl триггер 1 переключается в нулевое состояние (фиг. 2б); в момент t2 задним фронтом первого входного импульса триггер 4 переключается в единичное состояние (фиг. 2и), разрешая тем самы переключение триггера 2, и в момент t3 передним фронтом второго входного импульса триггер 2 переключается в нулевое состояние (фиг. 2Ь), нулевой уровень с выхода которого, поступая на S-вход триггера 4, запрещает переключение последнего в нулевое состояние. В момент t4 триггеры 1 и 2 находятся в нулевом состоянии нулевые уровни с выходов которых, поступая на S-входы триггеров 3 и 4

1282

запрещают их переключение по (,-вхо- дам, в момент t5 перед}1им фронтом третьего входного импульса триггер 1 переключается в единичное состояние, при этом происходит разблокировка триггера 3 и в момент t6 задним фронтом третьего входного импульса триггер 3 переключается в нулевое состояние (фиг. 2i , поскольку в этот

момент на его 1-входе - нулевой уровень, а на К-входе - единичный уровень. Нулевой уровень с выхода трит - гера 3, поступая на S-вход триггера I , блокирует его переключение в нулевое состояние по С-входу. В момент t7 передним фронтом четвертого входного импульса в единичное состочние переключается триггер 2 (фиг. 2 Ь), при этом происходит разблокировка

по триггера 4, который в момент t8 задним фронтом четвертого импульса переключается в нулевое состояние (фиг. 2). В момент t9 триггеры 3 и 4 находятся в нулевом

состоянии и блокируют по S-входам переключение триггеров 1 и 2 входными импульсами. В момент tlO задним фронтом пятого входного импульса триггер 3 переключается в единичное

состояние (фиг. 2 г) , поскольку в

этот момент на его I и К-входах присутствуют единичные уровни и триггеры 1-3 находятся в единичном состоянии, а триггер 4 - в нулевом. Таким образом, предлагаемое устройство вернулось в исходное состояние, после чего цикл деления повторяется.

Формула изоб ретения

Делитель частоты следования импульсов, содержаш;ий три триггера, С-вход первого из которых соединен с входной шиной, прямой выход - с информационным входом второго триггера, инверсный выход которого соединен с информационным входом первого триггера, и выходную шину, отличающийся тем, что, с дельн) повышения быстродействия и стабильности работы, в него введены элемент И-НЕ и четвертый триггер, причем первый и второй триггеры выполнены D -типа, третий и четвертый -- 1К-типа, при этом С-входы вто- рого,,третьего и четвертого триггеров соединены с входной шиной, пря- мой выход первого триггера соединен с S- и К-входами третьего триггера.

прямой выход которого подключен к S-входу первого триггера, .прямой выход второго триггера подключен к первому входу элемента И-НЕ, выход которого соединен с выходной шиной, а также к S-, 1-й К-входам четверРедактор Л. Гратилло

Составитель А. Соколов

Техред И. Верес Корректор М. Максимишинец

Заказ 3718/57Тираж 816Подписное

ВПИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

того триггера, прямой выход которого соединен с вторым входом эле- , мента И-НЕ и S - входом второго триггера , инверсный выход с Г - входом третьего триггера.

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на двенадцать | 1985 |

|

SU1298902A1 |

| Программируемый делитель частоты | 1985 |

|

SU1298899A1 |

| Делитель частоты следования импульсов | 1985 |

|

SU1243131A1 |

| Синхронный делитель частоты на десять | 1985 |

|

SU1298901A1 |

| Синхронный делитель частоты по модулю 2 @ -1 | 1985 |

|

SU1298903A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Синхронный делитель частоты | 1988 |

|

SU1555854A2 |

| Синхронный делитель частоты | 1985 |

|

SU1290516A1 |

| Синхронный делитель частоты | 1986 |

|

SU1504800A1 |

| Счетчик по модулю 5 | 1987 |

|

SU1480119A1 |

Изобретение относится к вычислительной технике и предназначено для синхронного деления частоты входных импульсов на 2,5 и 5. Цель изобретения - повьшение быстродействия и стабильности работы устройства. Делитель содержит триггеры 1 и 2 Г -типа, триггер 3 1К-типа, входные и выходные шины. Достижению поставленной цели способствует вве- . дение в делитель триггера 4 1К-типа, элемента И-НЕ 5 и образование новых связей между элементами устройства. 2 ил. U 00 to 00

| Кольцевой делитель частоты по модулю 2 @ -1 | 1982 |

|

SU1133665A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пересчетное устройство по модулю 1,5 | 1982 |

|

SU1019642A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты следования импульсов | 1981 |

|

SU980292A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-07-07—Публикация

1985-01-07—Подача