Изобретение относится к вычислительной технике и предназначено для синхронного деления частоты входных импульсов на 2,5 и 5.

Известен делитель частоты следования импульсов на 5, содержащий триггеры и элементы И-НЕ 1.

Однако указанное устройство характеризуется ограниченными функциональными возможностями, так как не обеспечивает деление входной импульсной последовательности на 2,5, и недостаточно высокой надежностью.

Наиболее близким по технической сущности к изобретению является дели.тель .частоты следования импульсов, содержащий три Дк-триггера, С-вход первого из которых соединен с вхрд нор шиной, 3-вход - с инверсным выхоЬом второго ЦК-триггера, выход которого соединен с С-входом третьего ЗК-триггера 2.

Недостатки известного делителя ограниченные функциональные возможности, так как он не обеспечивает синхронного деления входной импульс.ной последовательности на 2,5 и 5, и невысокая надежность.

Цель изобретения - расширение функциональных возможностей за счет получения коэффициентов деления, равных 2,5 и 5, при одновременном повышении надежности.

Поставленная цель достигается тем, что в делитель частоты следования импульсов, содержащий три ЭК-триггера, С-вход первого из которых соединен с входной шиной, J-вход - с инверсным выходом второго JK-триггера, а выход - с 3 ВХОДОМ второго ЭК-триггера, выход которого соединен с С-входом третьего ЛК-триггера, введен элемент равнозначности, первый вход которого соединен с С-входом первого 15 ЭК-триггера, второй вход - с прямым выходом третьего JK-триггера, а выход - с С-входом второго jK-триггера.

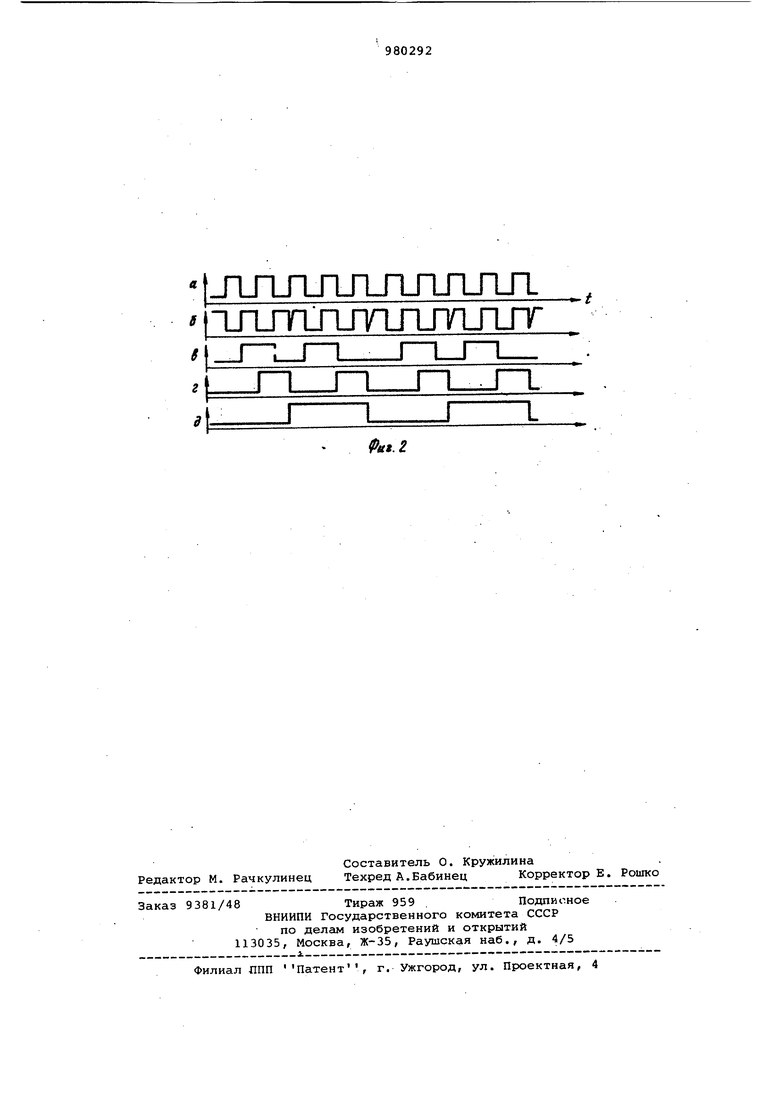

На фиг. 1 представлена структурная схема предлагаемого делителя на фиг. 2 - временные диаграммы, поясняющие его работу.

Делитель содержит JК-триггеры 1-3 и элемент 4 равнозначности.

Делитель частоты работает следующим образом.

В начальный момент производится установка ЭК-триггеров 1-3 в нулевое состояние (цепи установки на схеме не показаны). На входы элемента 4

поступают входные импульсы. Ug) и импульсы Ug с выхода ЭК-триггера 3 (фиг. 2 а,д).

Элемент 4 формирует импульсы U в соответствии с выражением

..Uj

Во время .нулевого потенциала на выхрде.,,.ДК-триггера 3 и на выходе элемента 4 формируются импульсы,соответ(СТвУющие инвертированному входному сигналу Uj,,{ {фиг. 2д) .

В соответствии с потенциалом на Э-входе ,jK-тpиггepa 2 (фиг. 2в) формируется импульс, .задним фронтом которого запускается ЭК-триггер 3. Во время единичного потенциала на входе Зк-триггера 3 (фиг, 2д) и на выходе .элемента 4 формируются импульсы (фиг. 26), соответствующие входным импульсам . После формирования второго импульса на выходе К-триггера 3 ЭК-триггеры 1-3 устанавливаются в исходное состояние.

На пять входных импульсов UQ- делитель выдает два выходных (фиг. 2г) и один импульс на выходе Зк-триггера 3, причем эти импульсы появляются строго через 2,5 и 5 входных импульсов.

Таким образом, введение; элемента 4 равнозначности в схему делителя позволяет получить синхронное деление на 2,5 и 5 относительно начального момента деления и значительно повысить надежность предлагаемого делителя по сравнению с известным, выполненным на большом количестве элементов И-НЕ с различным числом входов, в которых невозможно применение

стандартных ЭК-триггеров- из серий микросхем ТТЛ.

Кроме того, получение меандра (Q 2) на выходе ЗК-триггера 3 позволяет производить последовательное соединение нескольких предлагаемых делителей и получать коэффициенты деления 2,5; 5; 12,5; 25 и т.д., что невозможно сделать в известных делителях на 2,5.

Формула изобретения

Делитель частоты следования импульсов, содержащий три ЭК-триггера, С-вход первого из которых соединен с входной шиной, 7-вход - с инверсным выходом второго JK-триггера, а выход - с П-входом второго JK-триггера, выход которого соединен с С-вхдом третьего ЭК-триггера, отличающийся тем, что, с целью расширения функциональных возможностей за счет получения коэффициентов деления, равных 2,5 и 5, при одновременном повышении надежности, в него введен элемент равнозначности, первы вход которого соединен с С-входом первого ПС-триггера, второй вход с прямым .выходом третьего JFK-триггера, а выход - с С-входом второго ГК-триггера.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 570205, кл. Н 03 К 23/02, 1976.

2.Гушников B.C. Интегральная электроника в измерительных приборах Л., Энергия , 1974, с. 85.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с целочисленным коэффициентом деления | 1983 |

|

SU1095414A1 |

| Устройство для дискретной регулировки фазы | 1982 |

|

SU1027639A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Делитель частоты (его варианты) | 1984 |

|

SU1187261A1 |

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Селектор импульсов по периоду следования | 1983 |

|

SU1121775A1 |

| Синтезатор частот | 1976 |

|

SU799101A1 |

| Резервированный делитель частоты следования импульсов | 1981 |

|

SU961155A1 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1989 |

|

SU1677870A1 |

| Резервированный делитель частоты импульсов | 1977 |

|

SU698130A2 |

{JTJlJlJlJTJl-rLrLrLn. llJlJTiriJinjTJTLrLJT

Авторы

Даты

1982-12-07—Публикация

1981-06-17—Подача