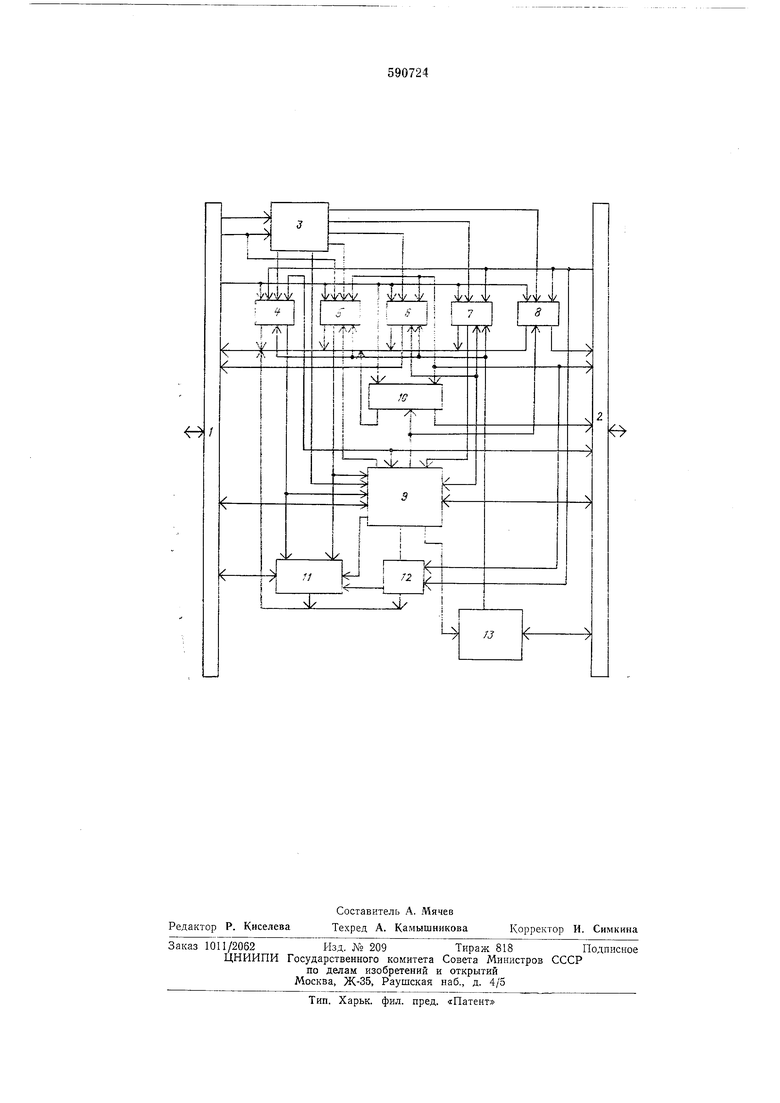

СО вторым входом первого блока связи, четвертый выход которого соединен с .первым входол деши фратора, второй .вход которого соединен с пятым .выходом блока связи и четвертым входом регистра команд, пятый вход которого соединен с третьим выходом второго блока связи, четверты;м входом регистра адреса памяти, вторыми входами регистра данных и блока обработки запросов, третий вход которого соединен с четвертым выходом второго блока связи, четверты.ми входами регистра старшего байта данных и третьим входом регистра признаков, четвертый вход которого соединен со вторым выходом второго блока связи, второй выход первого блока связи соедииеи с третьим входо.м регистра данных. Даиное устройство характеризуется эффективностью в режиме прямого доступа. Целью изобретения является .иовышение коэффициента использования оборудования. Поставленная цель достигается тем, что в устройство введен блок подготовки режима прямого доступа, выход iKOToporo соединен с пятыми входами регистров признаков, адреса паМЯти, счетчика слов и шестым входом регистра команд, ;блок подготовки режи.ма прямого доступа соединен двусторонними связями с блоком управления и вторым блоком связи. Блок-схема устройства приведена па чертеже. Устройство содержит блоки /, 2 связи, дешифратор 3, регистр 4 признаков, регистр 5 команд, регистр б адреса памяти, счетчик 7 слов, регистр 8 старшего байта данных, блок 5 управления, регистр 10 данных, блок 11 захвата, блок 12 о.бработки запросов, блок /5 подготовки режима прямого доступа. Устройство работает в следуюших основиых режимах: а)осуществляет обмен информацией в программном режиме под уиравлен.ием процессора;б)осуществляет обмен информацией между оперативной памятью ЭВМ и периферийной системой в режиме прямого доступа к памяти по инициативе процессора или устройства -периферийной системы; в)в режиме автоматической обработки запросов устройств периферийной системы автономно производит .иоиск источника запроса. При записи информации в периферийиую систему блоя 9 стробирует прием информации из блока 1 в регистр 10. .Затем запускается цикл периферийной системы, для чего блок 9 посылает в блок 2 комацду периферийной системы (номера -периферийной подсистемы, устройства и его регистра и код фуикции). При операции записи информация из регистров 10 к 8 передается в блок 2. /При записи полного слова данных в лериферийную систему предварительно проводится цикл загруз.ки регистра 8 старшими разряда.ми .данных. После выдачи команды бло.к 9 посылает в блок 2 сигнал синхронизации. После выполнепи5; операции адресуемая периферийная подсистема выдает ответный си.нхронизируюший сигнал, поступающий из блока 2 в блок 9. Приняв этот синхросигнал, блок 9 заканчивает операцию. При операции чтения блок 9 стробирует прием .данных периферийной системы из блока 2 в регистры 10 и 8, снимает команду и синхросигнал и выдает через блок / ответный синхросигнал в общую шину. При операции чтения информация из регистра W передается в блок /. Процессор, опознав наличие ответного синхросигнала, завершает операцию НО общей щине. Режим прямого доступа к памяти ;может проводиться устройством как .по инициативе процессора, так и ио ииициативе периферийного устройства. В перво.м случае для подготовки прямого доступа к памяти процессор загружает в регистр 4 - номер и код функции периферийной подсистемы, в регистр 5 - номер устройства и регистра, в регистр 6- начальный адрес области памяти ЭВМ, к которой проводится обращение, в счетчик 7 - дополнительный код количества слов, КОторое будет передано. Последним загружается регистр 4, причем в нем дополнительно устанавливаются следующие разряды управления, обеспечивак щие соответствующие режимы работы: разряды разрешения сканирования адресов иер.иферийиой системы, - если он в единице, после передачи слова даниых помер регистра устройства увеличивается на единицу, иосле опроса всех регистров номер устройства увеличивается иа едииицу; -разряд разрешения прерывания по окончанию режима, цри -установке этого разряда после передачи всего блока данных устройство выпол1няет п-рерывание программы ЭВМ; -разряд разрешение передачи бло-ков - при уста.новке этого разряда устройство занимает общую ппгну на шремя -передачи всего блока данных; -разряд начала режима - после его установки устройство переходит в .даиный режим работы. Последовательность операций при работе УСтройСтва в режиме прямого доступа 1следующая. Содержимое управле.ния прямым доступом, а также помар устройства и его регистра передаются из регистра 5 в блок 9. Номер и код функции передаются из регистра 4 в блок 9, где дешифруется код функции. При чтении дапных в памяти ЭВМ блок 9 запускает цикл периферийиой системы, для чего посылает в блок 2 соответствующую Команду. После .выполнения команды периферийное устройство выставляет яа линии магистрали данные в ответный синхросигнал. Блок 9, иринжв из блока 2 ответный Оинх-росилнал, ст.робирует за.несение .да-нных в регистр 10, снимает ко-манду и сиихр-ооигнал и запускает блок II, который проводит операцию захвата общей шины для ;выпол.нения прямога доступа к памяти. После того, как устройство стано1вится задатчиком общей шины, блок 9 открывает выходные вентили регистра 10 и его содержимое передается в блок /, затем блок 9 посылает через |блок 1 ъ общую щину код записи и синхросигнал. После выполнения операции память ЭВМ от1вечает ответным синхросигналом, который через блок / поступает в блок 9. Приняв этот сигнал, блок 9 заФерщает операцию на общей шиле и увеличивает содержимое регистра 6 и счетчика 7 на единицу. Если передача блоков запрещена, то общая шина освобождается и цикл повторяется снова, если разрешена, то общая шина не освобождается и цикл повторяется без фазы зах1вата. При операции записи аначала проводится операция захвата общей щвны, затем цикл чтения 1соде ржимого ячейки памяти, адрес которой хранится в регистре 6, для чего блок 9 открывает вентили регистра 6 и выста/вляет код чтения и си-нхросигнал. После выполнения операции ло общей щине блок 9 стробирует прием данных в регистр 10, а затем запускает периферийной системы. После выполнения команды периферийной системой блок 9 снимает информацию и уве-личивает на единицу содержимое регистра 6 и счетчика 7. После этого iBiCe операции повторяются снова. Если установлен разряд разрешения сканирования адресов, то после передачи каждого слО(Ва увеличивается на единицу содержимое регистра 6 и счетчика 7 и номер регистра периферийной cniCTeMH. Окончание режнма прямого доступа происходит по сигналу переполнения счетчика 7, после получения которого блок 9 завершает все операции и переводит устройство в исходное состояние. При проведении режима прямого доступа к памяти по инициативе периферийного устройства последовательность работы следующая. Периферийное устройство выставляет заnpOiC прямого доступа, который через блок 2 поступает в блок 13. Если устройство сво:бодно и не выполняет других операций, блок 13 запускает бло« 9, который совместно с ним проводит последовательно две операции чтения по магистрали периферийной системы. Для проведения первого цикла блок 13 выставляет признак чтения первого слова, а блок 9 - сигнал синх ронизации. После выполнения операции периферийное адрес устройство, пославшее запрос прямого доступа, выставляет ячейки памяти и дополнительный код числа слОВ и сопровождает эту информацию ответным с1ьнХросигкалом. Блок 9 сигнализирует бло.ку 13 о .выполнении первого цикла. Блок 13 стробирует прием информации в регистр 6 и счетчик 7. Затем выставляет признак чтения второго слова и запускает блок 9, который для.проведения второго цикла посылает через блок 2 сигнал синхронизации. После выполнения этой операции периферийное устройство выставляет номер периферийного устройства и его регистра и необходимые разряды управления прямым доступом к памяти, номер и код функции периферийной подсистемы и ответный синхросигнал. Блок 9 сигнализирует блоку 13 о выполнении второго цикла. Блок 13 стробирует прием информации из блока 2 в регистры 4 и 5 и снимает сигнал синхрониза.ции. Управление передается блоку 9 и дальнейший обмен данными между периферийной системой и памятью ЭВМ проводится так же, как в режиме прямого доступа к памяти по инициативе ЭВМ. в режиме автоматической обработки запросов в регистре 4 программно устанавливается разряд разрешения этого режима. При получении от периферийной системы запроса на прерывание устройство с помощью блока 9 посылает через блок 2 команду чтения слова запросов. После выполнения этой команды каждая периферийная подсистема выставит запросы. Блок 9, приняв ответные синхросигналы, свидетельствующие о выполнении команды, стробирует прием слова запросов в блок 12. Блок J2 по заданному закону производит выборку наиболее приоритетного запроса. Каждому запросу блок 12 ставит в соответствие вектор прерывания - начальный адрес подпрограммы обслуживания данного запроса. После определения запроса наиболее приоритетного и соответствующего ему вектора прерывания блок 12 запускает блок //, жоторый производит по общей щине операцию ирерывания. Век-тор прерывания передается из блока 12 в блок / и блок 11 завершает операцию на общей шине. Реализация в устройстве прямого доступа в память по инициативе периферийной системы позволяет повысить эффективность использования оборудования устройства и ЭВМ за счет сокращения примерно на порядок времени подготовки режима прямого доступа в память ЭВМ устройств периферийной системы. Это особенно важно для диалоговых систем, а также при связи посредством предложенного устройства периферийных ЭВМ с центральной. Формула изобретения Устройство управления периферийной системой, содержащее дешифратор, регистры признаков, команд, адреса памяти, старщего айта данных, данных, счетчик слов, блок правления, блок захвата, блок обработки апросов, первый блок связи, второй блок вязи, причем входы блока управления соединены с первыми входами первого блока вязи, регистра признаков дешифратора реистра команд, счетчика слов, с первым и торым выходами второго блока связи, выхоы дешифратора соединены с первыми вхоами регистров признаков, команд, адреса

памяти, старшего байта данных, счетчика слов, второй выход первого блока связп соединен со вторыми входами регистров признаков, команд, адреса памяти, старшего байта данных, счетчика слов, первые выходы регистров старшего байта данных и данных соединены соответственно с первым и вторым входами второго блока связи, первый выход регистра адреса памяти соединен с первым входом первого блока связи, вторые входы регистров признаков, команд, адреса памяти данных, старшего байта данных и счетчика слов соединены со вторым входом первого блока-связи, выходы блока управления соединены с первыми входами регистра данных, блока захвата и блока обработки запросов и с третьими входами регистров команд, старшего байта данных, адреса памяти, счетчика слов и блоков связи, со второго по пятый входы блока захвата соединены соответственно с первым выходом блока обработки запросов, первыми выходами регистров признаков и команд, и третьим выходом первого блока связи, четвертый вход которого соединен с первым выходом блока захвата, вторые выходы блоков захвата и обработки запросов соединены со вторым входом первого блока связи, четвертый выход которого соединен с первым входом дешифратора, второй вход которого соединен

с пятым выходом блока связи и четвертым входом регистра хо.манд, пятый вход которого соединен с третьим выходом второго блока связи, четвертым входом регистра адреса памяти, вторыми входами регистра данных и блока обработки запросов, третий вход которого соединен с четвертым выходом второго блока связи, четвертыми входами регистра старшего байта данных и третьим входом регистра признаков, четвертый вход которого соединен со вторым выходом второго блока связи, второй выход первого блока связи соединен с третьим входом регистра данных, отличаюш,ееся тем, что, с целью повышения коэффициента использования оборудования, в устройство введен блок подготовки режима прямого доступа, выход которого соединен с пятыми входами регистров признаков, адреса памяти, счетчика слов и шестым входом регистра команд, блок подготовки режима прямого доступа соединен двусторонними связями с блоком управления и вторым блоком связи.

Источники информации, принятые во внимание при экспертизе:

1.Патент США, № 3815099, кл. 340-172.5, 1974.

2.Патент Великобритании N° 1108800, кл. 64 А, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1975 |

|

SU561180A1 |

| Устройство для сопряжения электронной вычислительной машины с абонентами | 1976 |

|

SU642701A1 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения процессора с периферийным устройством | 1984 |

|

SU1246102A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

Авторы

Даты

1978-01-30—Публикация

1975-07-11—Подача