10

15

20

25

t

Изобретение относится к вычислительной технике -и может использовать-, ся в информационно-измерительных.системах, например в системах регистрации энергетических спектров частиц или других статистических распреде- . лений.

Цель изобретения,- расширение класса решаемых устройством задач за счет обеспечения одновременного накопления информации в инкрементном реясиме прямого доступа при произвольном задании областей адресации памяти ЭВМ.

Расширение функциональных возможностей приводит к повышению производительности и эффективности систем, используюш;их данное устройство соп- ряжения.

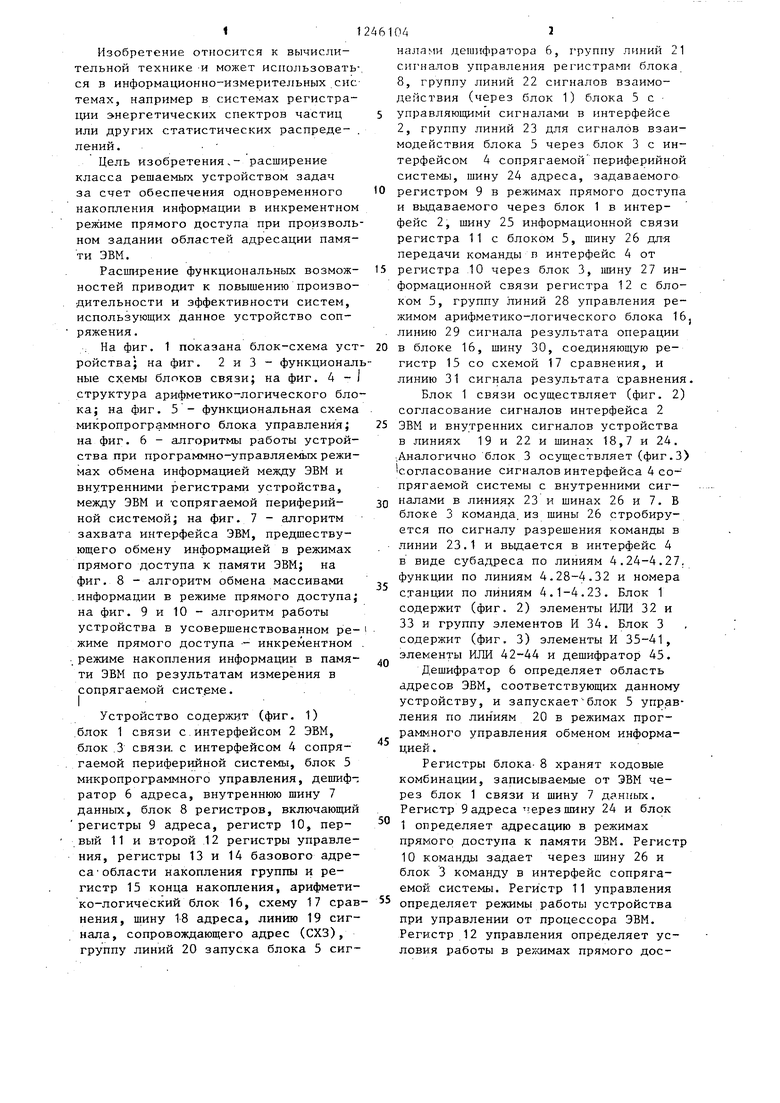

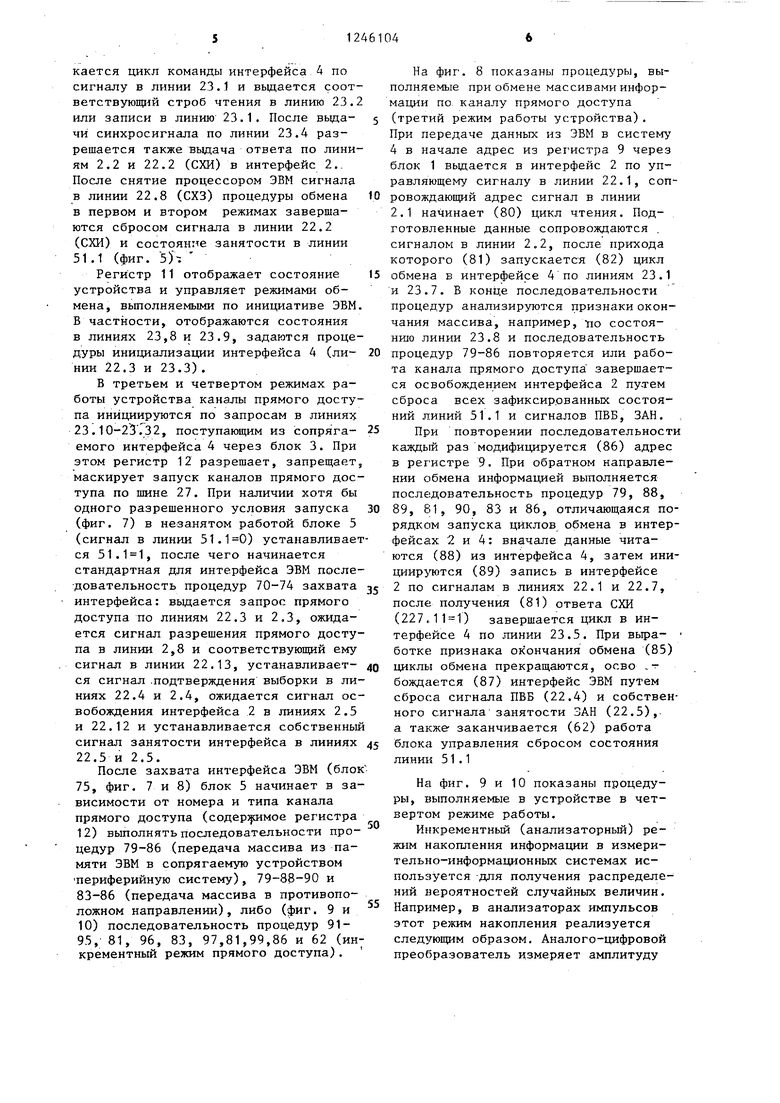

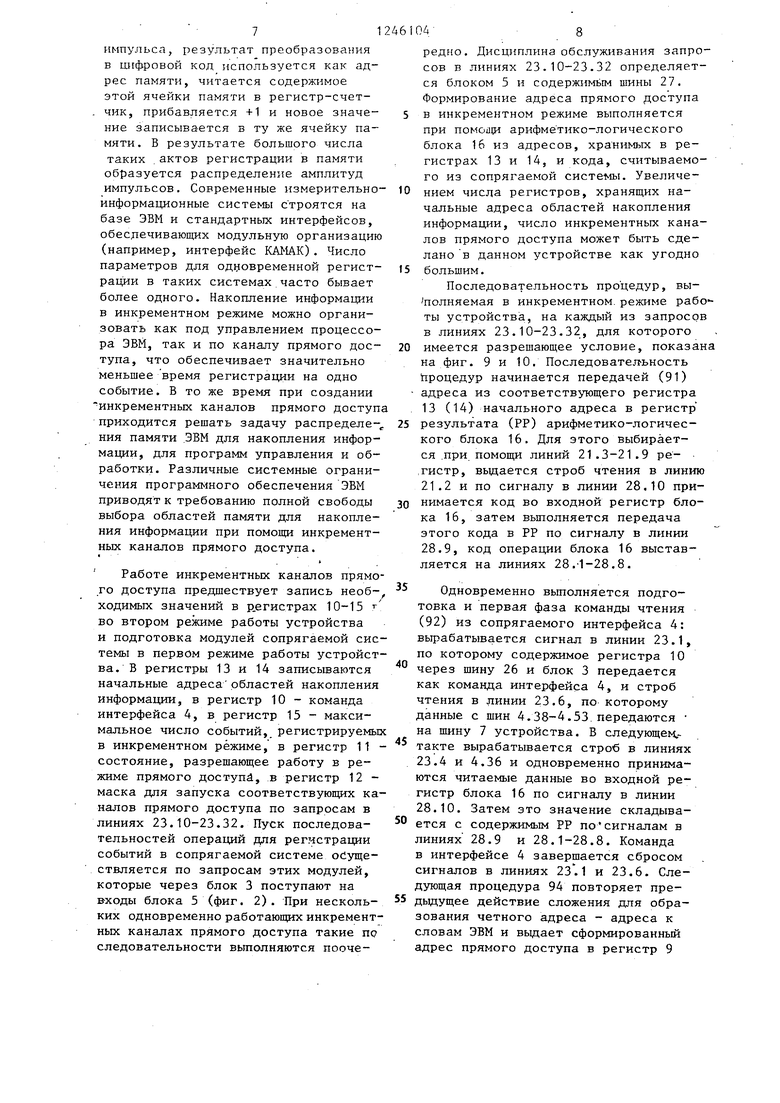

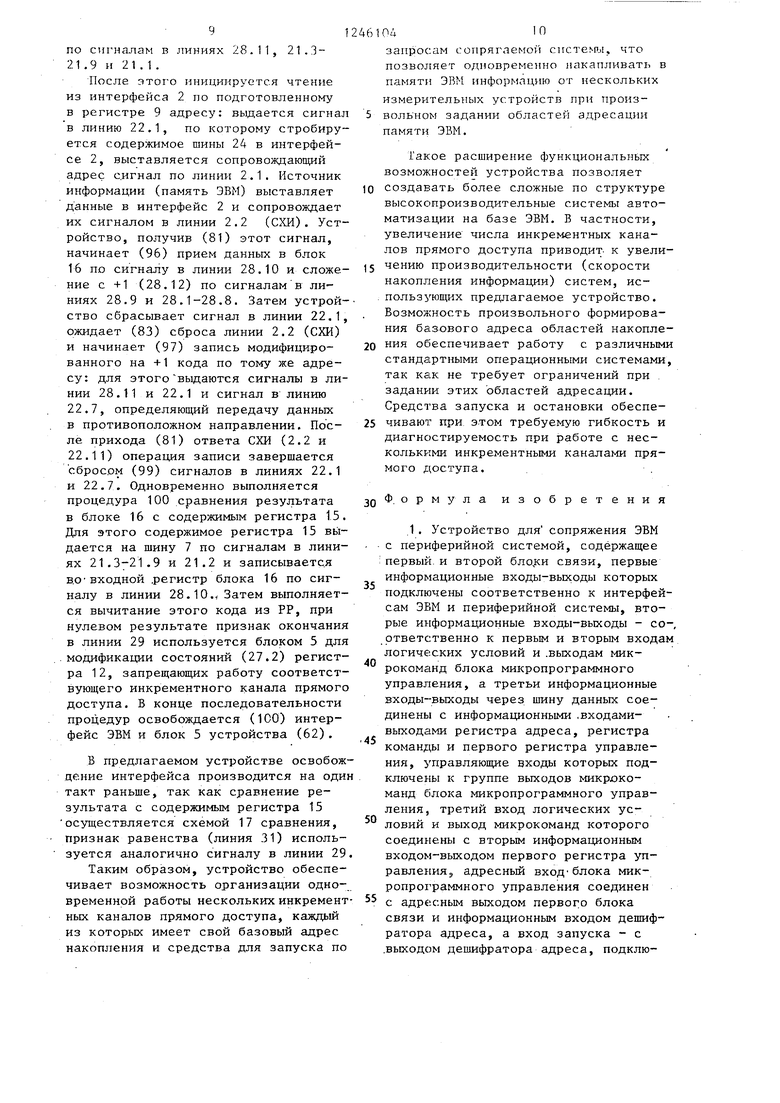

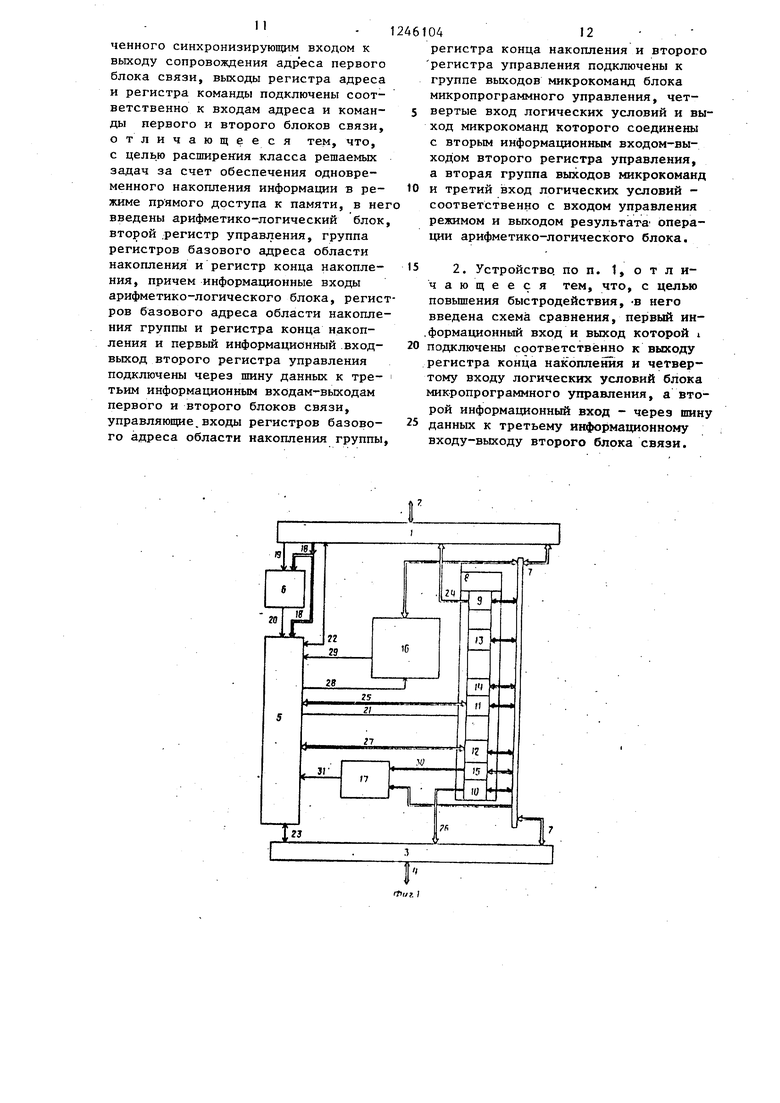

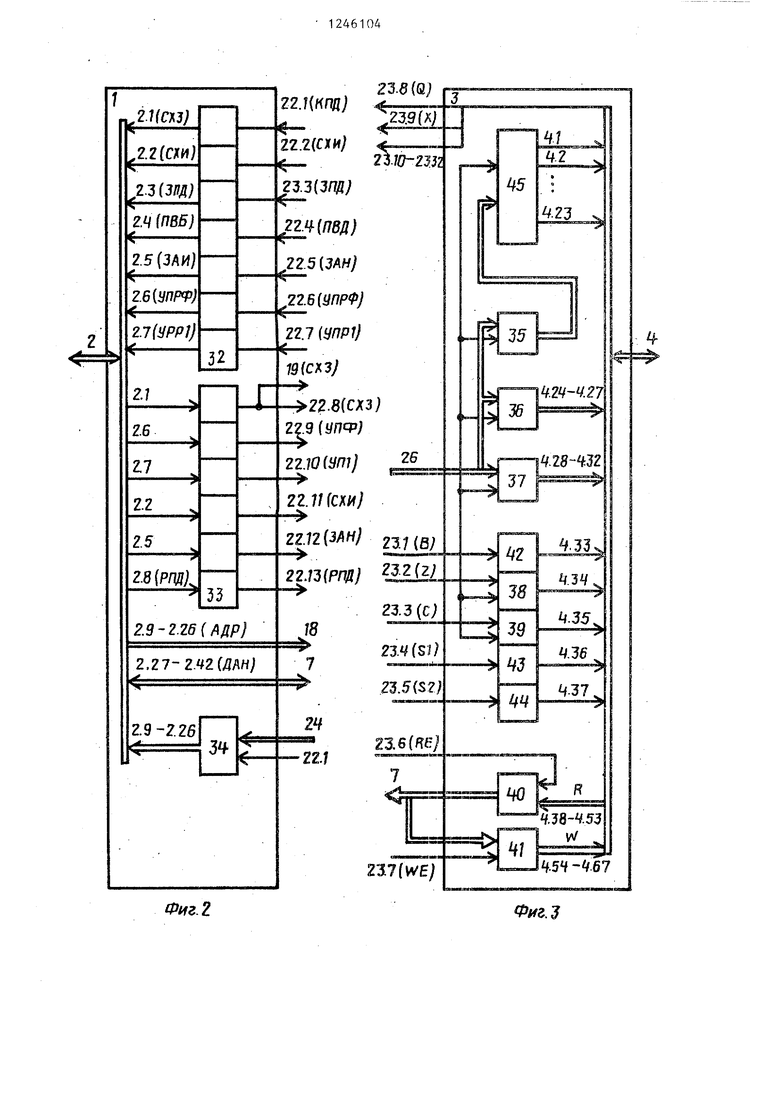

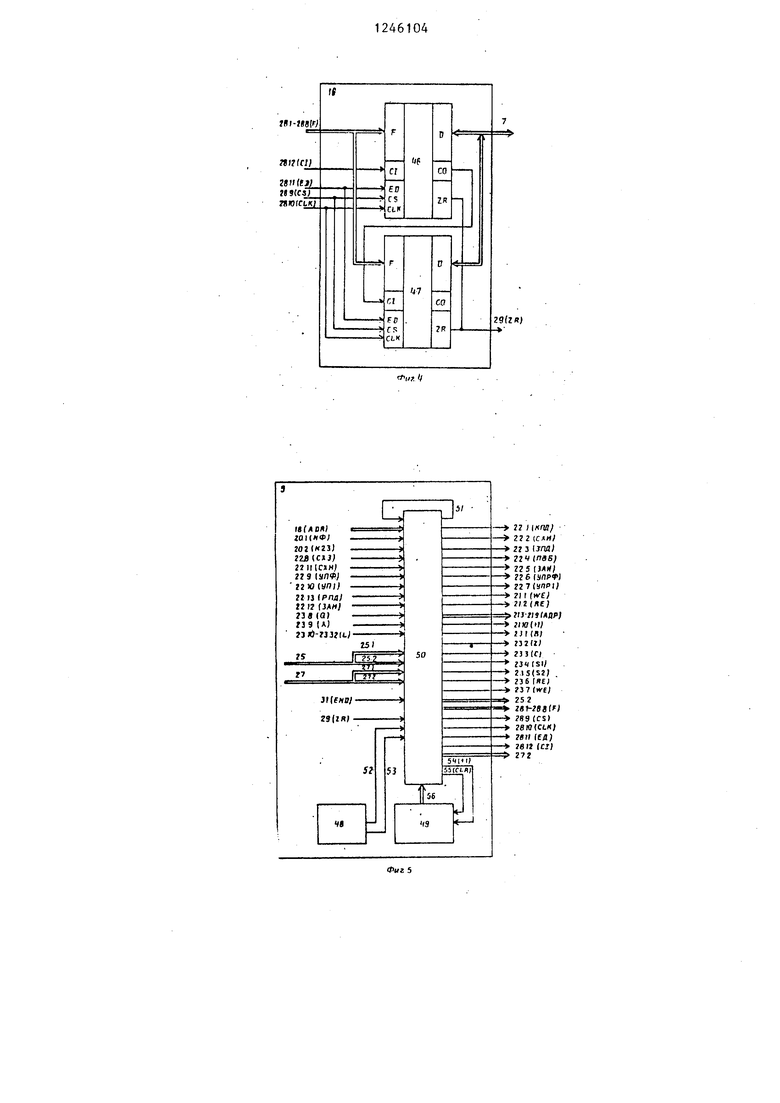

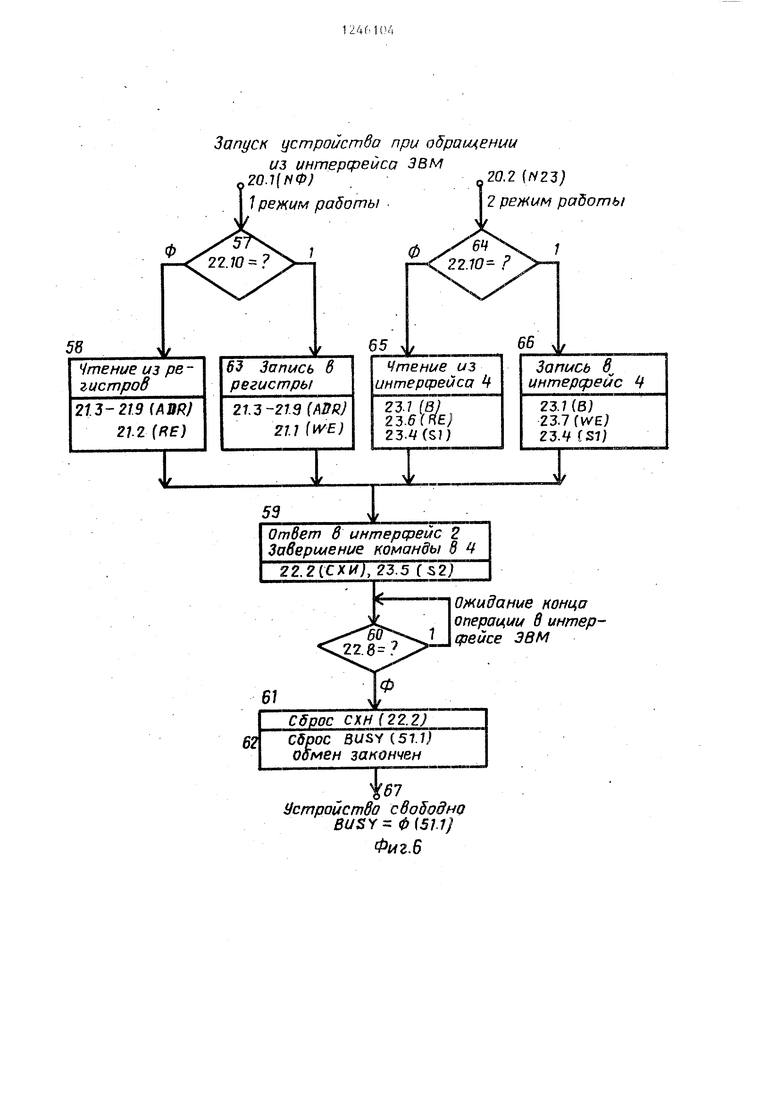

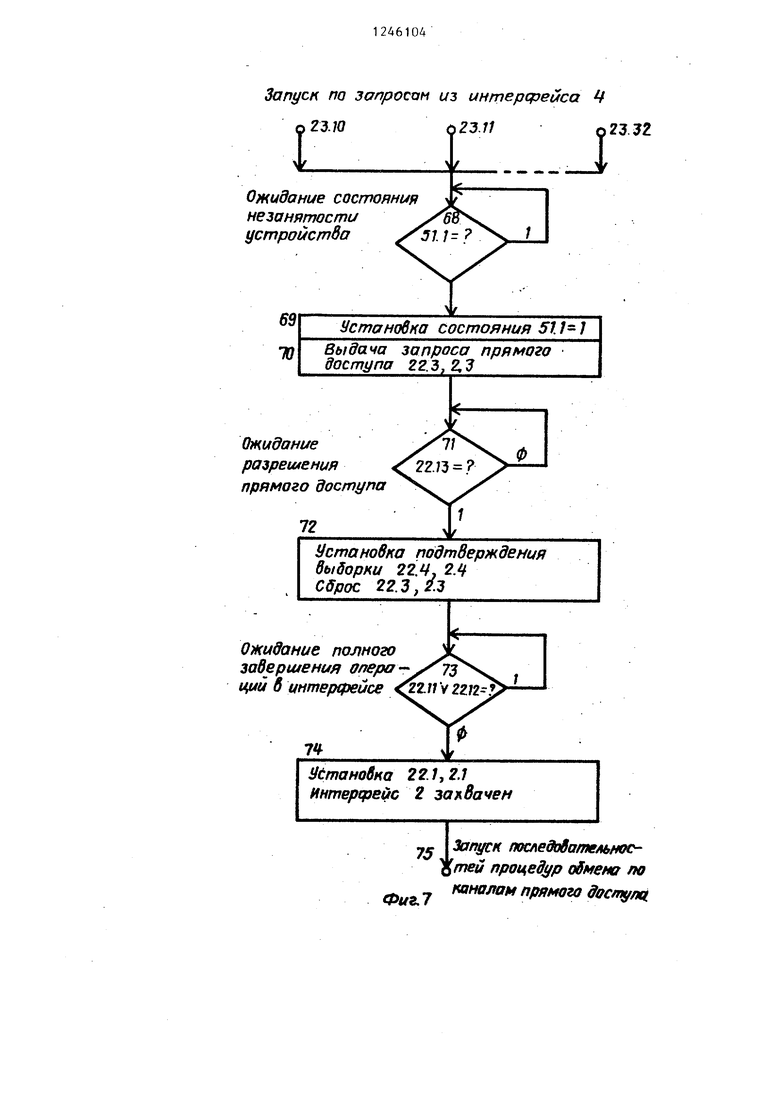

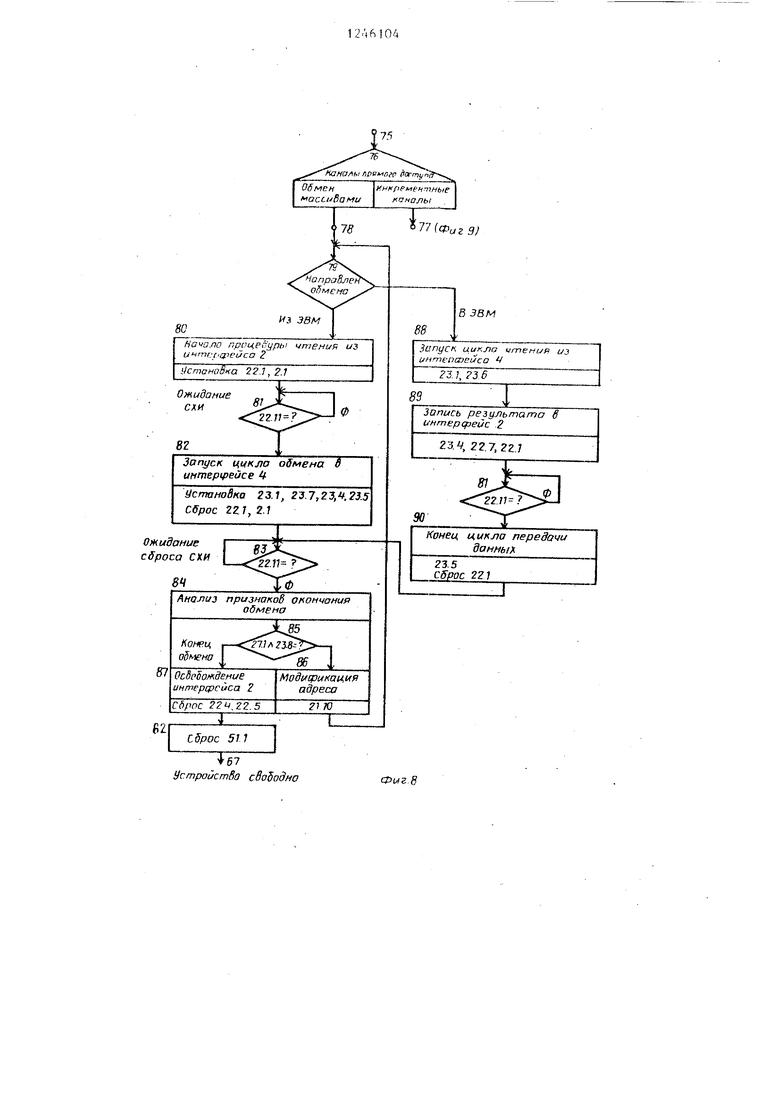

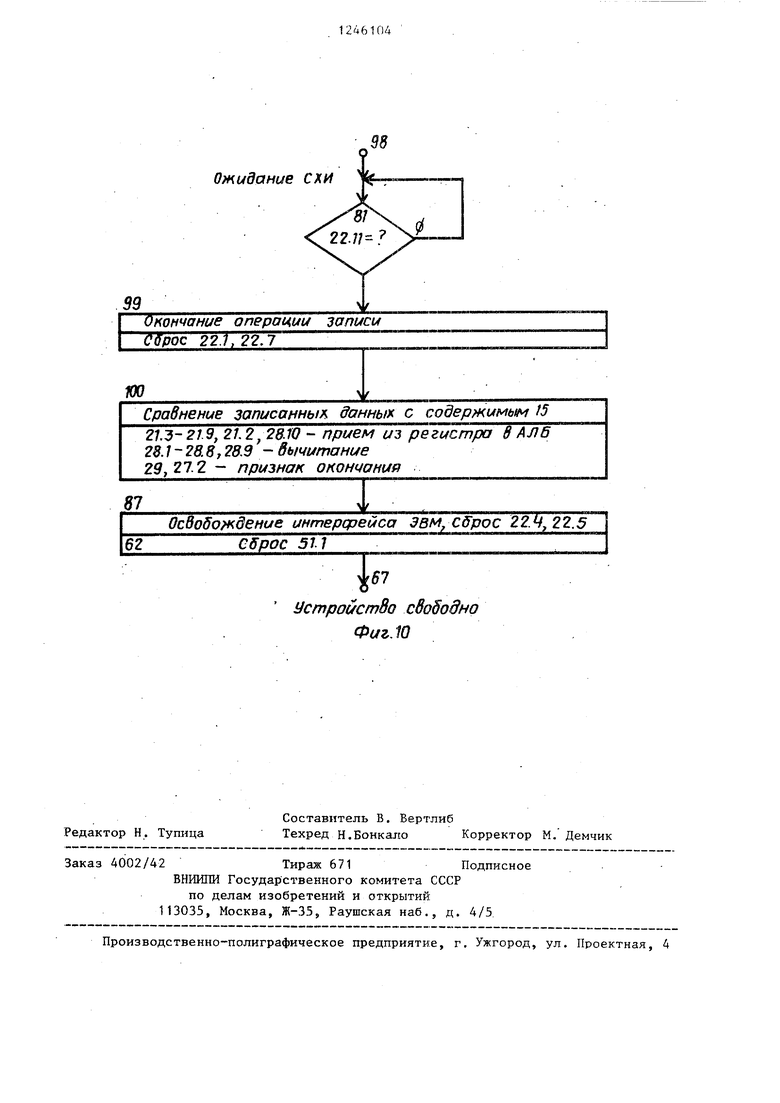

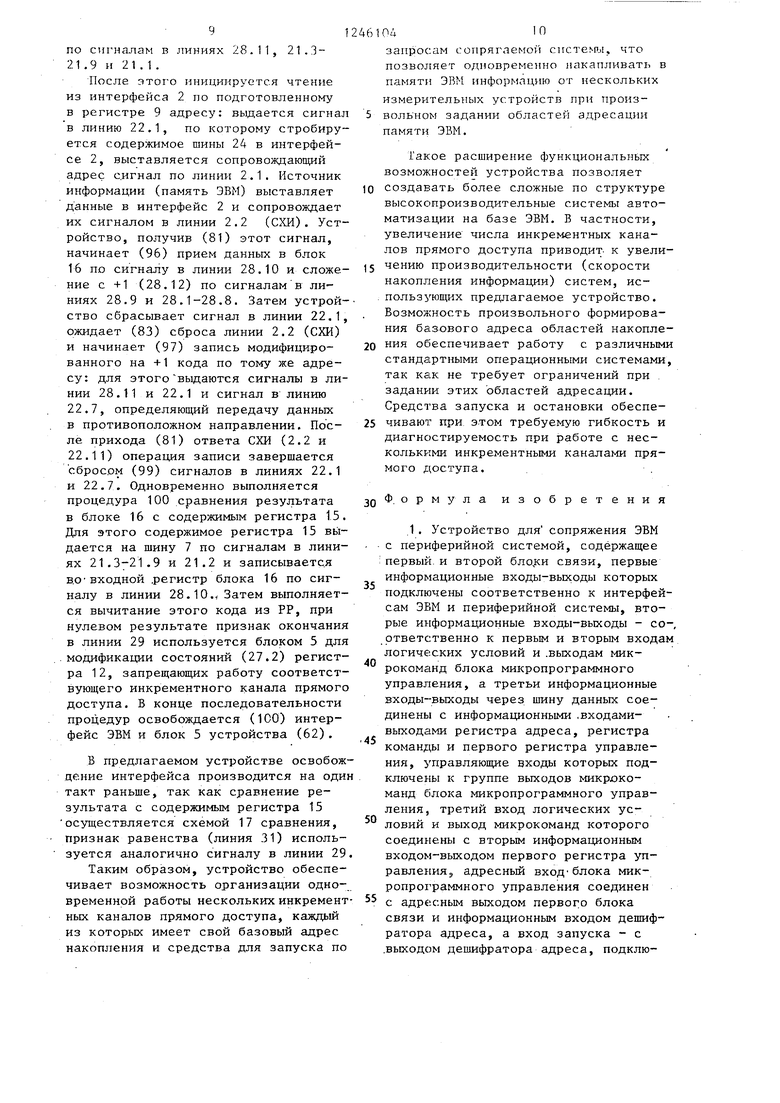

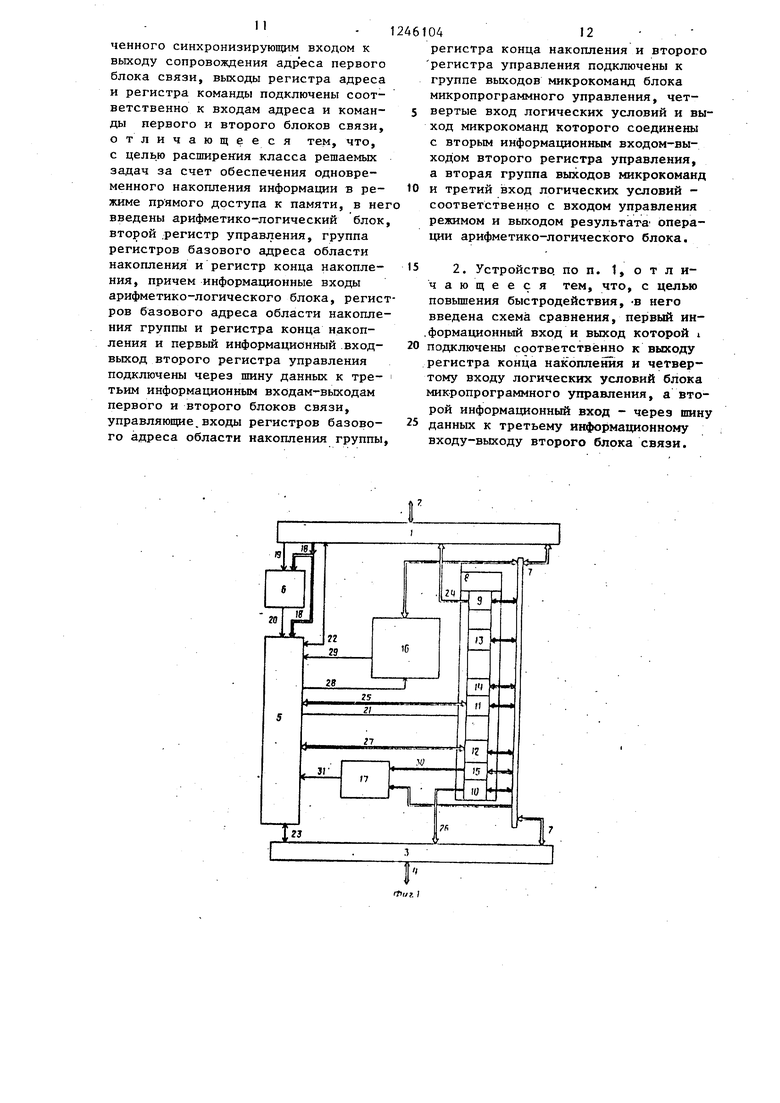

; На фиг. 1 показана блок-схема устройства; на фиг. 2 и 3 - функциональные схемы блоков связи; на фиг. 4 - 1 структура арифметико-логического блока; на фиг. 5 - функциональная схема микропрограммного блока управления; на фиг. 6 - алгоритмы работы устройства при программно-управляем1з1х режимах обмена информацией между ЭВМ и внутренними регистрами устройства, между ЭВМ и сопрягаемой периферийной системой; на фиг. 7 - алгоритм захвата интерфейса ЭВМ, предшествующего обмену информацией в режимах прямого доступа к памяти ЭВМ; на фиг. 8 - алгоритм обмена массивами информации в режиме прямого доступа; на фиг. 9 и 10 - алгоритм работы устройства в усовершенствованном ре- i жиме прямого доступа - инкрементном . режиме накопления информации в памяти ЭВМ по результатам измерения в сопрягаемой системе.

Устройство содержит (фиг. 1) .блок 1 связи с.интерфейсом 2 ЭВМ, блок 3 связи, с интерфейсом 4 сопрягаемой периферийной системы, блок 5 микропрограммного управления, дешиф-: ратор 6 адреса, внутреннюю шину 7 данных, блок 8 регистров, включающий регистры 9 адреса, регистр 10, первый 11 и второй 12 регистры управления, регистры 13 и 14 базового адреса области накопления группы и регистр 15 конца накопления, арифметико-логический блок 16, схему 17 срав- 55 нения, шину 18 адреса, линию 19 сигнала, сопровождающего адрес (СХЗ), группу линий 20 запуска блока 5 сиг12461

30

35

40

45

50

10

15

20

25

i

55

246104J

налами дешифратора 6, группу линий 21 сигналов управления регистрами блока 8, группу линий 22 сигналов взаимодействия (через блок 1) блока 5 с управляю1цими сигналами в интерфейсе 2, группу линий 23 для сигналов взаимодействия блока 5 через блок 3 с интерфейсом 4 сопрягаемой периферийной системы, шину 24 адреса, задаваемого регистром 9 в режимах прямого доступа и вьщаваемого через блок 1 в интерфейс 2, шину 25 информационной связи регистра 11 с блоком 5, шину 26 дл-я передачи команды в интерфейс 4 от регистра 10 через блок 3, шину 27 информационной связи регистра 12 с блоком 5, группу линий 28 управления режимом арифметико-логического блока 16, линию 29 сигнала результата операции в блоке 16, шину 30, соединяющую регистр 15 со схемой 17 сравнения, и линию 31 сигнала результата сравнения.

Блок 1 связи осуществляет (фиг. 2) согласование сигналов интерфейса 2 ЭВМ и внутренних сигналов устройства в линиях 19 и 22 и шинах 18,7 и 24. .Аналогично блок 3 осуществляет(фиг.З) согласование сигналов интерфейса 4 со- прягаемой системы с внутренними сигналами в линиях 23 и шинах 26 и 7. В блоке 3 команда, из шины 26 стробиру- ется по сигналу разрешения команды в линии 23.1 и выдается в интерфейс 4 в виде субадреса по линиям 4.24-4.27. функции по линиям 4.28-4.32 и номера с:ганции по линиям 4.1-4.23. Блок 1 содержит (фиг. 2) элементы ИЛИ 32 и 33 и группу элементов И 34. Блок 3 содержит (фиг. 3) элементы И 35-41, элементы ИЛИ 42-44 и дешифратор 45.

Дешифратор 6 определяет область адресов ЭВМ, соответствующих данному устройству, и запускает блок 5 управления по лин иям 20 в режимах прог- рамм;ного управления обменом информацией .

Регистры блока-8 хранят кодовые комбинации, записываемые от ЭВМ через блок 1 связи и шину 7 данных. Регистр 9 адреса .ерез шину 24 и блок 1 определяет адресацию в режимах прямого доступа к памяти ЭВМ. Регистр 10 команды задает через шину 26 и блок 3 команду в интерфейс сопрягаемой системы. Регистр 11 управления определяет режимы работы устройства при управлении от процессора ЭВМ. Регистр 12 управления определяет условия работы в режимах прямого дос30

35

40

45

50

3

тупа (разрешает, запрещает, запускает каналы прямого доступа, а также отображает состояния устройства),

Содержимое регистров 13 и 14 базовых адресов областей накопления ис- пользуется для формирования вместе с принимаемыми из интерфейса 4 кодовыми комбинациями адреса ячейки памяти ЭВМ. Кроме собственно регистров блок 8 содержит ключевые схемы для выдачи и приема данных в шину 7, Вторые шины регистров 9,10 и 15 представляют собой выходы разрядов регистров. В шинах 25. и 27 регистров управления часть линий выполняет соединение выходов разрядов регистров 11 и 12с входами блока 5 по линиям 25.1 и 27.1, часть линий (25. и 27.2) соединяет выходы блока 5 с входами регистров.для отображения и чтения со стороны ЭВМ состояний устройства. Регистр 9 адреса выполнен как счетчик, модификация адреса осуществляется по сигналу в линии 21.10 Арифметико-логический блок 16 выпол няет процедуры формирования адреса памяти ЭВМ, модификации прочитанных по этому адресу данных на +1 и сравнения результата модификации с содержимым регистра 15 для выработки в линию 29 признака окончания работы канала прямого доступа. Регистры 13 и 14 хранят начальные адреса областей памяти ЭВМ, в которые накапливается информация в инкрементных режи- мах прямого доступа.

На фиг. 4 показана структура арифметико-логического блока 16, образованного из секций 4Ь и 47 разрядностью меньшей, чем разрядность ЭВМ и устройства сопряжения. Выполняемая операция в блоке 16 определяется кодом в линиях 28.1-28.8, инициируется по сигналу в линии 28.9, прием данны выполняется по сигналу в линии 28.10 Вьщача результатов в шину 7 данных осуществляется, по сигналу в линии 28.11. Добавление единицы осуществляется сигналом в линии 28.12.

Блок 5 микропрограммного управления (фиг. 5) содержит генератор 48 тактовых импульсов, счетчик 49 такто и память 50 микроопераций с линиями Ы-53 входов, линиями 54 и 55 выходов и группой линий 56.входов. В паузах между циклами работы состояние в линии 51.1 разрешает некоторым из комбинаций сигналов на входах блока 5 инициировать последовательности

5 0 s 0 5 о

5

5

1044

микроопераций, переход от одной микрооперации к другой осуществляется при ПОМОЩ11 сигнала в линии 54 ( + 1 в счетчик 49) , в конце послеловате.пь- ности сбрасывается счетчик по сигналу в линии 555 в течение этого интервала времени в линии 51.1 вырабатывается сигнал занятости 6jioKa 5,блокирующий конкурируюп;ие запускающие условия на входе блока 5.

На фиг. 6-10 показаны процедуры 57-100 реализации алгоритмов.

Схема 17 сравнения вырабатывает признак окончания накопления информации в инкрементном режиме прямого доступа более быстрым способом, чем при noMonpi арифметико-логического блока,

Устройство работает следующим образом.

Блок 5 управления обеспечивает работу устройства в следующих основных режимах: обмен информацией между ЭВМ и сопрягаемой системой (под управлением процессора ЭВМ, обмен информацией между ЭВМ и регистрами устройства (под управлением процессора ЭВМ)5 обмен информацией между памятью и сопрягаемой системой без участия процессора ЭВМ, инкрементный режим накопления информации в памяти ЭВМ без участия процессора ЭВМ.

Предлагаемое техническое решение . направлено на достижение положительного эффекта в последнем из указанных режимов работы.

В первых двух режимах работы ЭВМ выставляет через блок 1 по шине 18 адрес устройства и по линиям 19 и 22.8-22.10 сопровождаю1цне адрес сигналы. При совпадении адреса с адресом данного устройства выходные сигналы в линиях 20 дешифратора 6 запускают блок 5. На фиг. 6 показаны процедуры, cooTBeTCTBiTOD e чтению регист ;ров (57-61), записи в регистры (57, 63 и 59-62), чтению из сопрягаемой системы (64,65 и 59-62) и записи из. ЭВМ в сопрягаемую систему (64,66 и 59-62). При обращении к регистрам в зависимости от сигнала в линии 2 2.10, тождественного сигналу в линии 2.7 в интерфейсе 2 ЭВМ, вырабатывается строб чтения в линии 21.2 или строб записи в линии 21.1. Адрес регистра на линиях 21.3 - 21.9 формируется из сигнала в линии 20.1 и части разрядов адреса ЭВМ в шине 18. При обращении к модулям сопрягаемой системы запускается цикл команды интерфейса 4 по сигналу в линии 23.1 и вьщается соответствующий строб чтения в линию 23.2 или записи в линию 23.1. После вьща- чи синхросигнала по линии 23.4 разрешается также выдача ответа по линиям 2.2 и 22.2 (СХИ) в интерфейс 2.. После снятие процессором ЭВМ сигнала в линии 22.8 (СХЗ) процедуры обмена в первом и втором режимах завершаются сбросом сигнала в линии 22.2 (СХИ) и состояние занятости в линии 51.1 (фиг. ЗЬ

Регистр 11 отображает состояние устройства и управляет режимами обмена, вьшолняемыми по инициативе ЭВМ. В частности, отображаются состояния в линиях 23,8 и 23.9, задаются процедуры инициализации интерфейса 4 (ли- НИИ 22.3 и 23.3).

В третьем и четвертом режимах работы устройства каналы прямого доступа инициируются по запросам в линиях 23 .10-25.32, поступающим из сопряга- емого интерфейса 4 через блок 3. При этом регистр 12 разрешает, запрещает, маскирует запуск каналов прямого доступа по шине 27. При наличии хотя бы одного разрешенного условия запуска (фиг. 7) в незанятом работой блоке 5 (сигнал в линии 51.) устанавливается 51., после чего начинается стандартная для интерфейса ЭВМ после- довательность процедур 70-74 захвата интерфейса: выдается запрос прямого доступа по линиям 22.3 и 2,3, ожидается сигнал разрешения прямого доступа в линии 2,8 и соответствующий ему сигнал в линии 22.13, устанавливает- ся сигнал .подтверждения выборки в линиях 22.4 и 2.4, ожидается сигнал освобождения интерфейса 2 в линиях 2.5 и 22.12 и устанавливается собственный сигнал занятости интерфейса в линиях 22.5 и 2.5.

После захвата интерфейса ЭВМ (блок 75, фиг. 7 и 8) блок 5 начинает в зависимости от номера и типа канала прямого доступа (содер мое регистра 12) выполнять последовательности процедур 79-86 (передача массива из памяти ЭВМ в сопрягаемую устройством периферийную систему), 79-88-90 и 83-86 (передача массива в противоположном направлении), либо (фиг. 9 и 10) последовательность процедур 91- 95, 81, 96, 83, 97,81,99,86 и 62 (ин- крементный режим прямого доступа).

На фиг. 8 показаны процедуры, выполняемые при обмене массивами информации по, каналу прямого доступа (третий режим работы устройства). При передаче данных из ЭВМ в систему 4 в начале адрес из регистра 9 через блок 1 выдается в интерфейс 2 по управляющему сигналу в линии 22.1, сопровождающий адрес сигнал в линии 2.1 начинает (80) цикл чтения. Подготовленные данные сопровождаются сигналом в линии 2.2, после прихода которого (81) запускается (82) цикл обмена в интерфейсе 4 по линиям 23.1 и 23.7. В конце последовательности процедур анализируются признаки окончания массива, например, по состоя- ншо линии 23.8 и последовательность процедур 79-86 повторяется или работа канала прямого доступа завершается освобождением интерфейса 2 путем сброса всех зафиксированных состояний линий 51.1 и сигналов ПВБ, ЗАН.

При повторении последовательност каждый раз модифицируется (86) адрес в регистре 9. При обратном направлении обмена информацией выполняется последовательность процедур 79, 88, 89, 81, 90, 83 и 86, отличающаяся порядком запуска циклов обмена в интерфейсах 2 и 4: вначале данные читаются (88) из интерфейса 4, затем ини циир тотся (89) запись в интерфейсе 2 по сигналам в линиях 22.1 и 22.7, после получения (81) ответа СХИ (227,) завершается цикл в интерфейсе 4 по линии 23.5. При выра- ботке признака окончания обмена (85) циклы обмена прекращаются, осво .- бождается (87) интерфейс ЭВМ путем сброса сигнала ПВБ (22.4) и собственного сигнала занятости ЗАН (22.5), а также заканчивается (62) работа блока управления сбросом состояния линии 51.1

На фиг. 9 и 10 показаны процедуры, выполняемые в устройстве в четвертом режиме работы.

Инкрементный (анализаторный) режим накопления информации в измерительно-информационных системах используется -для получения распределений вероятностей случайных величин. Например, в анализаторах импульсов этот резким накопления реализуется следующим образом. Аналого-цифровой преобразователь измеряет амплитуду

712

импульса, результат преобразования в Ш1ФРОВОЙ код используется как адрес памяти, читается содержимое этой ячейки памяти в регистр-счетчик, прибавляется +1 и новое значе- ние записывается в ту же ячейку памяти. В результате большого числа таких .актов регистрации в памяти образуется распределение амплитуд импульсов. Современные измерительно- информационные системы строятся на базе ЭВМ и стандартных интерфейсов, обесдечивающих модульную организацию (например, интерфейс КАМАК), Число параметров для одновременной регист- рации в таких системах часто бывает более одного. Накопление информации в инкрементном режиме можно организовать как под управлением процессора ЭВМ, так и по каналу прямого дос- тупа, что обеспечивает значительно меньшее время регистрации на одно событие. В то же время при создании инкрементных каналов прямого доступа приходится решать задачу распределе- НИН памяти ЭВМ для накопления информации, для программ управления и обработки. Различные системные ограничения программного обеспечения ЭВМ приводят к требованию полной свободы выбора областей памяти для накопления информации при помощи инкрементных каналов прямого доступа.

i

Работе инкрементных каналов прямого доступа предшествует запись необ-, ходимых значений в р.егистрах 10-15 во втором режиме работы устройства и подготовка модулей сопрягаемой системы в первом режиме работы устройства. Б регистры 13 и 14 записываются начальные адреса областей накопления информации, в регистр 10 - команда интерфейса 4, в регистр 15 - максимальное число событий,, регистрируемых в инкрементном режиме, в регистр 11 - состояние, разрешающее работу в режиме прямого доступ, в регистр 12 - маска для запуска соответствующих каналов прямого доступа по запросам в линиях 23.10-23.32. Пуск последова- тельностей операций для рег7-1страции событий в сопрягаемой системе осуществляется по запросам этих модулей, которые через блок 3 поступают на входы блока 5 (фиг. 2). При несколь- ких одновременно работающих инкрементных каналах прямого доступа такие пс следовательности выполняются пооче

0 s 0 5 о

5

0

5

048

редно. Дисциплина обслуживания запросов в линиях 23.10-23.32 определяется блоком 5 и содержимьгм шины 27. Формирование адреса прямого доступа в инкрементном режиме выполняется при помо11:(и арифме тико-логического блока 16 из адресов, хранимых в регистрах 13 и 14, и кода, считываемого из сопрягаемой системы. Увеличением числа регистров, хранящих начальные адреса областей накопления информации, число инкрементных каналов прямого доступа может быть сделано в данном устройстве как угодно большим.

Последовательность процедур, вы- полняемая в инкрементном. режиме работы устройства, на каждый из запросов в линиях 23.10-23.32, для которого . имеется разрешающее условие, показана на фиг. 9 и 10. Последовател ьность процедур начинается передачей (91) адреса из соответствующего регистра 13 (14) начального адреса в регистр результата (РР) арифметико-логического блока 16. Для этого выбирается .при помощи линий 21.3-21.9 регистр, выдается строб чтения в линию 21.2 и по сигналу в линии 28.10 принимается код во входной регистр блока 16, затем выполняется передача этого кода в РР по сигка.пу в линии 28.9, код операции блока 16 выставляется на линиях 28.-1-28.8.

Одновременно выполняется подготовка и первая фаза команды чтения (92) из сопрягаемого интерфейса 4: вырабатывается сигнал в линии 23.1, по которому содержимое регистра 10 через шину 26 и блок 3 передается как команда интерфейса 4, и строб чтения в линии 23.6, по которому данные с шин 4.38-4.53. передаются на шину 7 устройства. В следующем,- такте вырабатывается строб в линиях 23.4 и 4.36 и одновременно принимаются читаемые данные во входной регистр блока 16 по сигналу в линии 28.10. Затем это значение складывается с содержимым РР по сигналам в линиях 28.9 и 28.1-28.8. Команда в интерфейсе 4 завершается сбросом сигналов в линиях 23.1 и 23.6. Следующая процедура 94 повторяет пре- дьщущее действие сложения для образования четного адреса - адреса к словам ЭВМ и вьщает сформированный адрес прямого доступа в регистр 9

91

по сигналам в линиях 28.11, 21.3- 21.9 и 21.1.

После ятого инициируется чтение из интерфейса 2 по подготовленному в регистре 9 адресу: выдается сигнал в линию 22.1, по которому стробиру- ется содержимое шины 24 в интерфейсе 2, выставляется сопровождающий адрес сигнал по линии 2,1, Источник информации (память ЭВМ) выставляет данные в интерфейс 2 и сопровождает их сигналом в линии 2,2 (СХИ). Устройство, получив (81) этот сигнал, начинает (96) прием данных в блок 16 по сигналу в линии 28,10 и сложе- ние с +1 (28,12) по сигналам в линиях 28,9 и 28,1-28.8, Затем устройство сбрасывает сигнал в линии 22,1, ожидает (83) сброса линии 2,2 (СХИ) и начинает (97) запись модифициро- ванного на +1 кода по тому же адресу: для этого вьщаются сигналы в линии 28,11 и 22,1 и сигнал в линию 7.2,1, определяющий передачу данных в противоположном направлении, Пос- ле прихода (81) ответа СХИ (2,2 и 22,11) операция записи завершается сбросом (99) сигналов в линиях 22,1 и 22,7, Одновременно выполняется процедура 100 сравнения результата в блоке 16 с содержимым регистра 15. Для этого содержимое регистра 15 выдается на шину 7 по сигналам в линиях 21.3-21,9 и 21,2 и записывается в.О входной .регистр блока 16 по сиг- налу в линии 28,10,, Затем выполняется вычитание этого кода из РР, при нулевом результате признак окончания в линии 29 используется блоком 5 для .модификации состояний (27.2) регист- ра 12, запрещающих работу соответствующего инкрементного канала прямого доступа, В конце последовательности процедур освобождается (100) интерфейс ЭВМ и блок 5 устройства (62),

В предлагаемом устройстве освобождение интерфейса производится на оди такт раньше, так как сравнение результата с содержимым регистра 15 осуществляется схемой 17 сравнения, признак равенства (линия 31) используется аналогично сигналу в линии 29 Таким образом, устройство обеспечивает возможность организации одновременной работы нескольких инкремент ных каналов прямого доступа, каждый из которых имеет свой базовый адрес накопления и средства для запуска по

04IО

запросам сопрягаемой ciicTeNnji, что позволяет одновременно накапливать в памяти ЭВМ информацию от нескольких измерительных устройств при произвольном задании областей адресации памяти ЭВМ.

Такое расширение функциональных возможностей устройства позволяет создав1ать более сложные по структуре высокопроизводительные системы автоматизации на базе ЭВМ, Б частности, увеличение числа инкрементных каналов прямого доступа приводит, к увеличению производительности (скорости накопления информации) систем, использующих предлагаемое устройство. Возможность произвольного формирования базового адреса областей накопления обеспечивает работу с различным стандартными операционными системами так как не требует ограничений при . задании этих областей адресации. Средства запуска и остановки обеспечивают при этом требуемую гибкость и диагностируемость при работе с несколькими инкрементными каналами прямого доступа,

Ф. ормула изобретения

1, Устройство для сопряжения ЭВМ с периферийной системой, содержащее первый, и второй бло,ки связи, первые информационные входы-выходы которых подключены соответственно к интерфейсам ЭВМ и периферийной системы, вторые информационные входы-выходы - со ответственно к первым и вторым входа логических условий и .выходам микрокоманд блока микропрограммного управления, а третьи информационные входы-выходы через шину данных соединены с информационными .входами- выходами регистра адреса, регистра команды и первого регистра управления, управляющие входы которьк подключены к группе выходов микрокоманд блока микропрограммного управления, третий вход логических условий и выход микрокоманд которого соединены с вторым информационным входом-выходом первого регистра управления,, адресный вход блока микропрограммного управления соединен с адресным выходом первог;о блока связи и информационным входом дещиф- ратора адреса, а вход запуска - с .выходом дешифратора адреса, подклю

ченного синхронизирующим входом к выходу сопровождения адр еса первого блока связи, выходы регистра адреса и регистра команды подключены соответственно к входам адреса и команды первого и второго блоков связи.

отличающееся тем, что, с целью расширения класса решаемых задач за счет обеспечения одновременного накопления информации в режиме прямого доступа к памяти, в нег введены арифметико-логический блок, второй .регистр управления, группа регистров базового адреса области накопления и регистр конца накопления, причем информационные входы арифметико-логического блока, регистров базового адреса области накопления группы и регистра конца накопления и первый информационный .вход- выход второго регистра управления подключены через шину данных к третьим информационным входам-выходам первого и второго блоков связи, управляющие.входы регистров базового адреса области накопления группы.

610412

регистра конца накопления и второго регистра управления подключены к группе выходов микрокоманд блока микропрограммного управления, чет- 5 вертые вход логических условий и выход микрокоманд которого соединены с вторым информационным входом-выходом второго регистра управления, а вторая группа выходов микрокоманд 10 и третий вход логических условий - соответственно с входом управления режимом и выходом результата операции арифметико-логического блока.

5 2. Устройство, по п. 1, отличающееся тем, что, с целью повьшгения быстродействия, -в него введена схема сравнения, первый ин- .формационный вход и выход которой i

20 подключены соответственно к выходу регистра конца накопления и четвертому входу логических условий блока микропрограммного управления, а второй информационный вход - через шин

25 данных к третьему информационному входу-выходу второго блока связи.

Фщ I

Фиг.2

Фиг.

aiticti

tS ltttl tl 9(CS)

(6

гд(гя}

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1224805A1 |

| Устройство для сопряжения процессора с периферийным устройством | 1984 |

|

SU1246102A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1332326A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для обмена информацией между ЭВМ и внешней памятью | 1989 |

|

SU1714613A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для обмена информацией между магистралью параллельного интерфейса и последовательным каналом | 1986 |

|

SU1444788A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

Изобретение относится к области вычислительной техники и может использоваться в информационно-измерительных системах, например в сие- , темах регистрации энергетических спектров частиц или других статистических распределений. Целью изобретения является расширение класса решаемых устройством задач за счет обеспечения одновременного накопле-, , НИН информации в инкрементном режиме прямого доступа при произвольном задании областей адресации памяти ЭВМ. Такое расширение функциональных возможностей приводит к повьшзению производительности и эффективности систем, использующих данное устройство сопряжения. Поставленная цель достигается тем, что в устройство, содержащее два блока связи, дешифратор адреса, блок микропрограммного управления и блок регистров, включающий регистр адреса, первый регистр управления и регистр команды, введены арифметико-логический блок, а в блок регистров - группа регистров базового адреса области накопления, регистр конца накопления и второй регистр управления. Кроме того, в устройство введена схема сравнения. 1 з.п. ф-лы, 10 ил. (О (Л ю .4 О)

ГвГАОА

taidfi

202lM23j .

ггй(сч}

«IUCJH;2i9 ynf) iiviiyniinnipnai

ttt f3AHl (0)

Г39(А)

IS

7

1

50

2Г ллш; ггг (сди/ гг 3 (inal - ггч(пяБ) - гг5 txit} г 6 (inpT)

- Г27((ЛР1;

- г1 г (IVE;

- 11ЦЯС)

it -tiiinaPl г1ю((;

111 1Я1

гзг(г; гзз(г)

Z34IS4

Z.JS(S2) .

гзб ЯП

гз7(

252

zt isstfl

199 (CS)

гвю(сбк; гв ГЕД)

jen ICI)

гтг

Запуск устройства при обращ

из интерсреиса ЭВМ 20.ЦНФ)

1 режим работы

Z рсгботы

Ф

61

Ожидание конца операции в интер- срейсе ЭВМ

Сброс СХН (22.2}

62

Сброс 5t/SY (57J,I

Обмен закончен

57

Устройство свободно BUSY 0(51.1

Фиг. 5

Запуск по запросан из unniepqyeuca

Ожидание состоянир

незанятости

устройства

69 Ю

Установка состояния 51J-1

Выдача запроса прямого доступа 223,2,

Отидание разрешения прямого доступа

12

Установка подтверждения выборки 22.4, 2.Ц Сброс 22.3,2.3

Ожидание полного завершения апера-г 73 б интерсрейсе 2.n yzzj2

7ff

Убтановна 22.1,2.1 Интеререис 2 -закВачен

7J последоВательносQmeu npou,edt/p оИмеио по

ф J прямого доступу

HaHOfihi / рембго (iormynff-,

ТКФагЭ)

В ЭВМ

Начало прсщрд урь чтения из ичтсГ уейса 2

ИстаноВна 2 7, 2Л

Запуск иикло чтения из интспсоЕиса Ч

з,;, 15

8Z

т

Запись результата в интерсреис 2

Запуск ццкла обмена о интерфейсе U

Установка 23.1, 2.7,27,,23.5 Сброс 2Z1, 2.1

8J

90

Ожидание сброса СХИ

84

Конец цикла передачи данныи

В1

С5рос 5П

W7

Устройства свободно

Фиг.8

Инкрементный редким оуобмена

1

Передача адреса из регистра 3(If/ о накопительный регистр РР блока Ю AJJ6) 21 Z- 219,212,28Ю передала 8 А-П5 2S 9, 281- 28.8 фиксация РР

Запуск чтения 8 интерфейс/

23}, 23.6

Сло хсние РР с результатом чтения- 23 , 28Ю - передача б АЛ6 28.1-28.8,28.9-сло иение с РР 235, Cfpoc 23Л,

94

I

Повторное , запись адреса S регистр 9

АЛБс РР 28.11.21:5-213,21.1 - запись в рв истрЗ

95i

сь

36

ПриЕМ даннь и сложение с

28 Ю - прием в АЛ б

28Л2,289,28.1-288- Сложение с 1 i28,12) Сброс 22.1

921

О кидание задершениа

571

Запись результата в интвр }еис 2

гаП. 22.1, 22.6 0, 22.7 /

635 f Фиг Ю) Фиг.9

,э«

0)t udaHue СХИ 1

99

Устройство свободно Фиг.Ю

Редактор Н. Тупица

Составитель В. Вертлиб

Техред Н.Бонкало Корректор М. Демчик

Заказ 4002/42Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-ЗЗ, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

67

| Устройство для сопряжения периферийной системы с электронной вычислительной машиной | 1975 |

|

SU554534A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления периферийной системой | 1975 |

|

SU590724A1 |

Авторы

Даты

1986-07-23—Публикация

1984-05-24—Подача