СО 00

Изобретение относится к вычислительной технике и технике связи и предназначено для организации межресурсных связей в многопроцессорных вычислительных системах.

Цель изобретения - повышение быстродействия коммутационного устройства в режиме настройки на требуемые соединения.

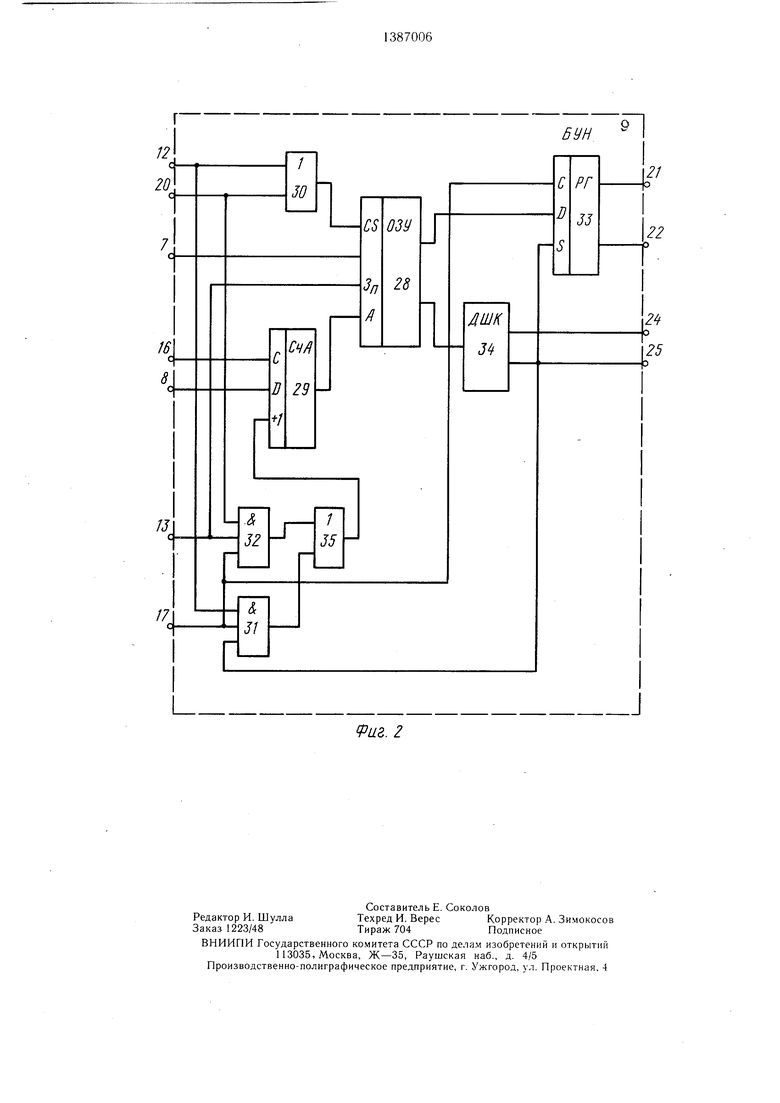

На фиг. I приведена функциональная схема коммутационного устройства; на фиг. 2 - функциональная схема блока управления настройкой.

Коммутационное устройство содержит информационные входы Ь - 1и устройства, модуль 2|-2п коммутации, группы 3i-3т модулей коммутации, образующие матричный коммутатор 3, информационные выходы 4i-4„ устройства, адресные входы 5 и 6 устройства, адресные входы 7 и 8 блоков 9i - 9m управления настройкой, управляющие входы 10 и 11 устройства, управляющие входы 12 и 13 блоков 9i-9m, синхронизирующие входы 14 и 15 устройства, синхронизирующие входы 16 и 17 блоков 9|- 9ш, адресный вход 18 устройства, дещифра- тор 19, входы 20 разрещения блоков 9: 9т,выходы 2 и 22 блоков 9i-9m, дешифраторы 231-23m, выходы 24 и 25 блоков 9i - 9ш, элемент И 26, выход 27 признака готовности устройства, узел 28 памяти, счетчик 29, элемент ИЛИ 30, элементы И 31 и 32, регистр 33, дещифратор 34, элемент ИЛИ 35.

Устройство работает следующим образом.

В режиме «Загрузка во все блоки 9 осуществляется последовательная запись всех программ настройки групп 3A(,...,m). В режиме «Настройка производится считывание программ из всех блоков 9 во все группы 3« одновременно. В режиме «Обмен производится передача информации с входов 1 на выходы 4 устройства после окончания настройки его на конкретную nporpajvi- му соединений.

Работа устройства в режиме «Загрузка начинается с прихода управляющего сигнала на вход 11 устройства, который через входы 13 блоков управления настройкой подается на входы записи считывания узлов 28, подготавливая их к приему информации. С адресного входа 6 устройства через входы 8 блоков 9 на информационные входы счетчиков 29 подается номер загружаемой программы, устанавливающий начальный адрес приема информации в узлы 28. С приходом на вход 14 устройства и далее через входы 16 блоков 9 на синхронизирующие входы счетчиков 29 импульса сопровождения информации номер программы записывается в счетчики 29 и подается на адресные входы узлов 28. Через вход 18 устройства на вход дешифратора 19 подается адрес загружаемого блока 9, возбуждается соответствующий выход дешифратора 19 и через вход 20 выбранного блока 9, элемент 30 на вход «Выбор кристалла узла 28 поступает сигнал.

0

0

5

0

5

0

5

0

5

разрещающий прием в последнем информации. Одновременно с этим на вход 5 устройства и далее через вход 7 выбранного блока 9 на информационный вход узла 28 подается команда настройки соответствующего матричного коммутатора и осуществляется прием этой команды в узел 28. После этого на вход 15 устройства подается тактовый импульс, который через вход 17 выбранного блока 9, элементы 32 и 35 поступает на счетный вход счетчика 29, который наращивает свое содержимое на единцу и тем самым подготавливает следующую ячейку узла 28 к приему следующей команды настройки, выставляя на его адресный вход новый адрес. После этого на вход 18 устройства подается адрес блока 9, в который записывается следующая команда настройки, и так до тех пор, пока в соответствующий блок управления настройкой не запишется последняя команда программы настройки матричных коммутаторов. Далее во все счетчики 29 записывается номер новой программы настройки и производится загрузка этой программы. Устройство заканчивает свою работу в режиме «Загрузка, когда с входа 11 снимается управляющий сигнал. Работа устройства в режиме «Настройка начинается с приходом на вход 10 устройства управляющего сигнала, который через входы 12 блоков 9 и элементы 30 поступает на первые управляющие входы узлов 28, разрешая чтение из них информации, одновременно через адресный вход 6 устройства, входы 8 блоков 9 на информационные входы счетчиков 29 адреда подается номер вызываемой программы, устанавливающий адрес начальных ячеек программы в узлах 28. С приходом на вход 14 устройства и далее через входы 16 блоков 9 на синхронизирующие входы счетчиков 29 импульса сопрп.ождения информации, номер программы записывается в счетчики 29 и с их выходов подается на адресные входы узлов 28. С выходов последних на входы дещифра- торов 34 подается код операции и если считанная в конкретном блоке 9 команда не является командой «Финиш, то с второго выхода дешифратора 34 снимается разрещающий сигнал, поступающий на вход установки регистра 33 и второй вход элемента 31. С подачей на вход 15 устройства и далее на входы 17 блоков 9 тактового импульса регистры 33 принимают информацию с первых выходов узлов 28 и через элементы 31 и 35 на счетный вход счетчиков 29 подается импульс, наращивающий их содержимое на единицу. Тем самым узел 28 подготавливается к чтению нОвой команды. Если же считанная в конкретном блоке 9 команда является командой «Финиш, то на втором выходе дешифратора 34 появляется сигнал, запирающий элемент 31 и запрещающий прием информации в регистр 33. При этом тактовые импульсы.

приходящие на вход 17 блока 9, не проходят на счетчик 29 и чтение содержимого последующих ячеек узла 28 не происходит. Команды настройки бывают трех типов: «Стирание, «Запись и «Финищ. Выполнение этих команд начинается с дещифра- ции кода команды в дешифраторе 34. Если код команды соответствует команде «Стирание, то с выхода 24 блока 9 на управляющий вход соответствующего дещифратора 23 и на вторые управляющие входы всех модулей 2i-2„ соответствующей группы 3 подается управляющий сигнал, возбуждающий все выходы дещифратора 23 и далее все управляющие входы модулей 2i-2„. При этом производится стирание связей по адресам выходов модулей 2i-2„ групп 3 поступающим с выхода 21 блока управления настройкой. Если код команды соответствует команде «Запись, то с выхода 24 блока управления настройкой выдается управляющий сигнал, запирающий вторые управляющие входы модулей 2i-2„ и разрещающий де- щифрацию старщих разрядов адреса входа соответствующего матричного коммутатора 3, поступающих с выхода 22 блока 9 в дешифратор 23. При этом возбуждается один из выходов дещифратора 23 и далее первый управляющий вход соответствующего модуля матричного коммутатора, в котором осуществляется установление связей по адресу, поступающему с выхода 21 блока 9.

Работа устройства в режиме «Настройка заканчивается появлением на выходе 27 устройства сигнала о том, что команда «Финищ выполнена всеми блоками 9. Тем самым устройство переходит в режим «Обмен.

Формула изобретения

1. Коммутационное устройство, содержащее матричный коммутатор, m информационных входов и п информационных выходов которого являются информационными входами и выходами устройства, соответственно дещифратор, выходы которого подключены к управляющим входам первой группы матричного коммутатора, отличающееся тем, что, с целью повышения быстродействия в режиме настройки на требуемые соединения, в него введены (т-1) дешифраторов, дополнительный дещифратор, m блоков управления настройкой и элемент И, первые адресные входы всех блоков управления настройкой объединены и являются первым адресным входом устройства, вторые адрес- ные входы всех блоков управления настройкой объединены и являются вторым адресным входом устройства, первые управляющие входы всех блоков управления настройкой объединены и являются первым управляющим входом устройства, вторые управ0

ляющие входы всех блоков управления настройкой объединены и являются вторым управляющим входом устройства, первые синхронизирующие входы всех блоков уиравлеиия настройкой объединены и являются первым синхронизирующим входом устройства, вторые синхронизирующие входы всех блоков управления настройкой объединены и являются вторым синхронизирующим входом

0 устройства, вход дополнительного дешифратора является входом выбора блока управления настройкой устройства, а m выходов дополнительного дешифратора соединены с входами разрешения соответствующих блоков управления настройкой, первый и

5 второй выходы k-ro блока управления настройкой (, ..., m) соединены с k-м адресным входом матричного коммутатора и с информационным входом k-ro дешифратора, выходы Н-го дешифратора (,...,т) подключены к управляющим входам Н-й группы матричного коммутатора, третий выход k-ro блока управления настройкой подключен к управляющему входу k-ro дешифратора и к k-му управляюшему входу матричного коммутатора, четвертые выходы

5 всех блоков управления настройкой подключены к входам элемента И, выход которого является выходом признака готовности устройства, Н-й информационный вход матричного коммутатора является Н-м информационным входом устройства.

0

2. Устройство по п. I, отличающееся тем, что блок управления настройкой содержит узел памяти, счетчик, регистр, дешифратор, первый и второй элементы И, первый и второй элементы ИЛИ, причем

5 информационный вход узла памяти является первым адресным входом блока, информа ционный и синхронизирующий входы счетчика являются вторым адресным и первым синхронизирующим входами блока соответд ственно, выход счетчика подключен к адресному входу узла памяти, первый вход первого элемента ИЛИ и первый вход второго элемента И соединены с первым управляющим входом блока, вход записи-считывания узла памяти объединен с вторым входом пер5 вого элемента И и является вторым управляющим входом блока, первый вход первого элемента И объединен с вторым входом первого элемента ИЛИ и является входом разрещения блока, выход первого элемента ИЛИ подключен к входу «Выбор кристал0 ла узла памяти, первый выход которого подключен к информационному входу регистра, первый и второй выходы которого являются первым и вторым выходами блока соответственно, второй выход блока памяти подключен к входу дешифратора, первый выход которого является третьим выходом блока, а второй выход дешифратора подключен к входу установки регистра, третьему входу второго элемента И и явля5

ется четвертым выходом блока, синхронизирующий вход регистра соединен с третьим входом первого элемента И, вторым входом второго элемента И и является вторым синхронизирующим входом блока, первый и

второй входы второго элемента ИЛИ подключены к выходам первого и второго элементов И соответственно, выход второго элемента ИЛИ подключен к счетному входу счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| Коммутационное устройство | 1989 |

|

SU1645963A1 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Устройство для управления матрич-НыМ КОММуТАТОРОМ | 1979 |

|

SU832719A1 |

| Устройство для формирования входных воздействий в системе программного контроля | 1983 |

|

SU1138803A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| Устройство для отображения информации | 1988 |

|

SU1501135A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

Изобретение относится к области вычислительной техники и техники связи, ин-Цель изобретения - повышение быстродействия в режиме настройки. Поставленная цель достигается тем, что в устройство коммутации, содержащее матричный коммутатор, введены m блоков управления настройкой, причем ввод настроечной информации в матричные коммутаторы осуществляется параллельно из соответствующих блоков. 1 з.п. ф-лы, 2 ил.

Фиг.1

PULZ. 2

| Коммутационное устройство для вычислительной системы | 1978 |

|

SU746492A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-07—Публикация

1986-05-26—Подача