(54) КОММУТАЦИОННОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ Изобретение относится к цифровой вычислительной технике. Ономожет быть использовано в составе вычислительных систем для связи вычислительных машин с общими внешними устройствами и для связи между вычислительны-ми машинами системы. . . Известны коммутирующие устройства для вычислительной системы, содёр.жащие связанные .с вьгаисл и тельными машинами коммутатор каналов,регистр настройки, дискрипторные регистры связи, регистр ключей связи, схему сборки, дешифратор равнозначности и вентили ll. В этом устройстве кроме каналов связи-Вычислительных мешшн с коммутатором каналов имеются дополнительные линии связи с регистром настройки, дискрипторным регистром связи, схемой сборки и регистром ключей связи. Известное устройство содержит боль шое количество элементов, что приводит к снижению надежности устройства Известно,коммутирующее устройство для вычислительной системы, содержащее коммутационную матрицу, соединенную с центрсшьными процессорами, про цессорами ввода-вывода и модулями памяти 2j. В данной вычислительной системе функции коммутации выполняются центральнкми процессорами, процессорами ввода-вывода и модулями памяти. 11анные устройства содержат большоечисло элементов, что снижает общую надежность системы. Целью изобретения является повышение надежности работы коммутирующего устройства. Указанная цель изобретения достигается тем, что в коммутационное устройство для вычислительной системы, содержащее матричный коммутатор и блок управления, причем первая и вторая группа выходов матричного коммутатора Являются соответственно, первой и второй группой выходов устройства, первгя группа входов матричного коммутатора соедийена с первой группой входов блока управления и является первой группой входов устройства, вторая группа входов матричного коммутатора является второй группой входов устройства введен дешифратор и матр1ица управления коммутацией, причем первая, вторая и третья группы выходов матрицы управления коммутацией является соответственно третьей группой входов матричного коммутатора,

третьей, группой выхолгов устройства и второй Г1 уппой входов блока управления, первая и вторая группы выходов дешифратора соединены соответЬтвенно, с первой группой входов матрицы управления коммутацией с третьей группой входов управления, первая и вторая группа выходов которого соединена соответственно со второй группой вхопов матрицы управления коммутацией с первой группой входов дешифратора, первая группа входов устройства соединена со второй группой входов дешифратора. И еще матрица управления коммутацией содержит тактовый генератор, первую и вторую группы элементов ИЛИ, первую группу кольцевых регистров сдвига по числу вычислительных машин, входящих в систему, третью и четвертую группу -элементов ИЛИ, вторую группу кольцевых регистров сдвига по числу внешних устройств входящих в систему, первую и вторую групги элементов И, причем выходы первой и третьей группы элементов ИЛИ являются второй группой выходов матрицы управления коммутацией, каждый вйход элемента ИЛИ второй группы элементов ИЛИ соединен с блокировочным входом соответствующего кольцевого регистра сдвига первой группы, каждый выход элемента ИЛИ четвертой группы элементов ИЛИ соединен с блокировочным уходом соответствующе о кольцевогр регистра сдвига второй группы, информационные выхода каждого кольцевого рег-йстрасдёйга первой группы соединены с первыми входами соответствующих элементов И первой группы элементов И, информационные выходы каждого кольцевого регистра сдвига второй группы соединены с первыми входами соответствующего,элемента и второй группы элементов И, вторые входы элементов И первой и второй группы являются первой группой входов Матрицы управления коммутацией,выхода элементов И первой и второй группы элементов И являются первой и третьей группой выходов матрицы управления коммутацией, выход калсдого элемента И первой группы элементов И соединены с соответствукхцим входом соответствугацего элемента ИЛИ первой и второй групп элементов ИЛИ, выход каждого элемента И второй группы соединен с соотвеТс тву1сщим вхбДЬМ сббтвётствующегр элемента ИЛИ, третьей и четвертой групп элементов ИЛИ, выход тактового генератора соединен со входом синхронизации всех кольцевых регистров сдвига первой и второй группы, управляющие входы каждого крльцевого регистра сдвига первой и второй групп являются вторбй группой входов матрицы управления кокпиутацией.

На фиг. 1 изображенаблок.-схема коммутационного устройства для вычиг746492

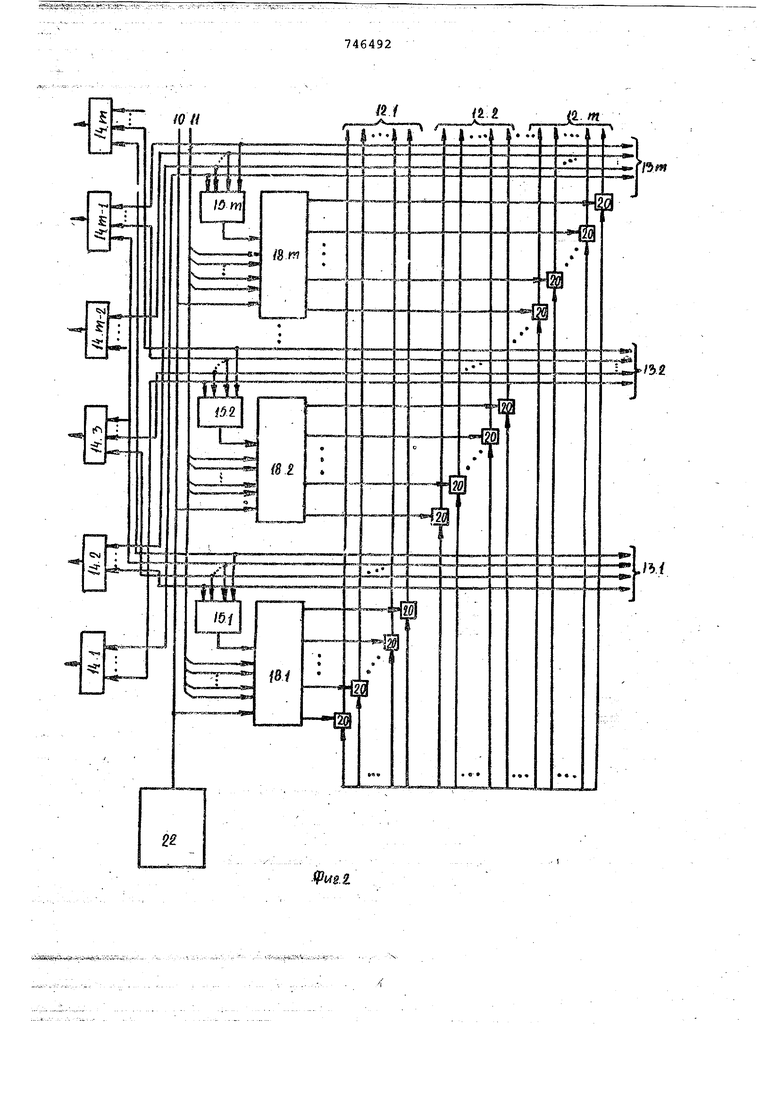

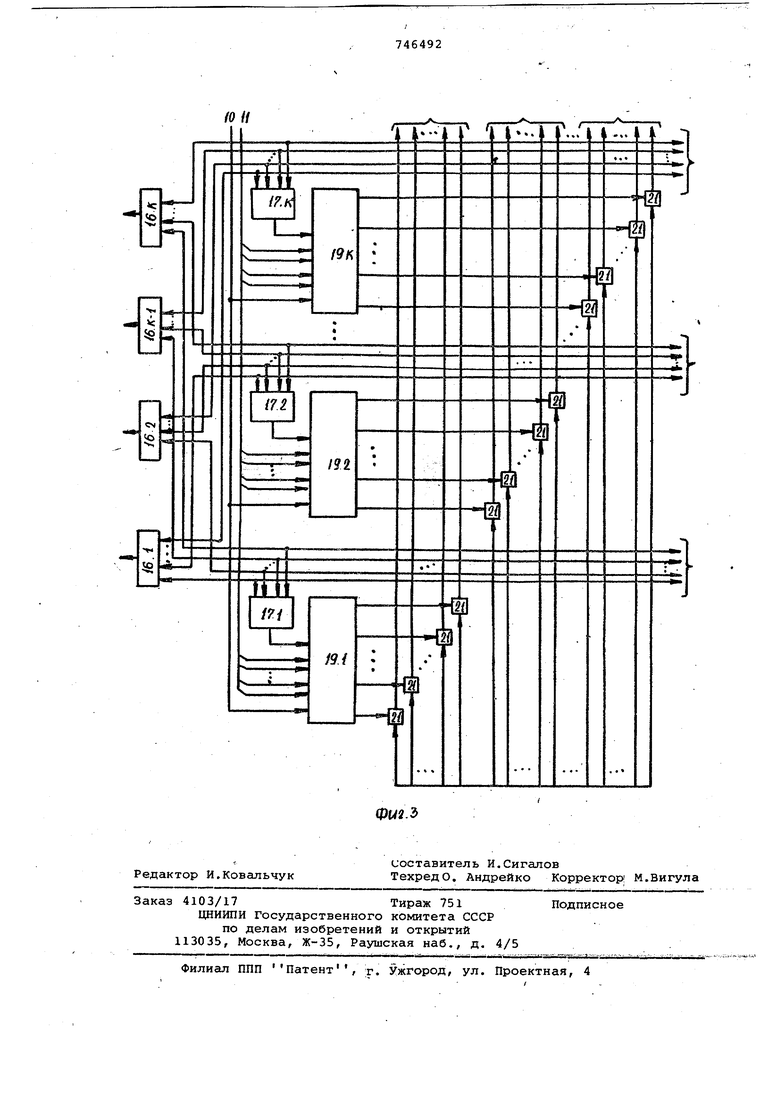

лительной систегльт; на фиг. 2 и 3 матрица для управления коммутацией.

Устройство содержит матричный комг.утатор 1, матрицу 2 управления комглутацией, блок 3 управления, дешифратор 4, первую хруппу выходов 5 матричного коммутатора, первую группу входов б матричного коммутатора, вторую группу выходов матричного коммутатора 7, вторую группу входов матричного коммутатора 8, первую группу вы,ходов матрицы 9 управления коммутацией, выход 10 тактового генератора, вторую группу выходов 11 матрицы управления коммутацией. Выходы управлягадих сигналов обращения i-ой машины (где , ..., т) соответственно 12-. 1, 12,2 2.т, выходы сигналов связи с блоком управления для регистрации обмена машиной (где i ,2 ..., m) срответств.енно 13.1, 13.2 13.m. Первая группа элементов 14.1 - 14.m ИЛИ, вторая группа элементов 15.1 - 15.m ИЛИ, третья группа элементов 16.1 - 16.m ИЛИ; четвертая группа элементов 17.1 I7.m ИЛИ, первая группа кольцевых регистров 18.1 - iS.m сдвига, вторая группа кольцевых регистров 19.1 19.k сдвига, первая группа элементов 20 И, вторая, группа элементов 21 И, тактовый генератор 22.

Работает устройство следующим образом.

Матричный коммутатор 1 связан с шинами каналрв вычислительных машин и каналов внешних устройств. Он осуществляет переключение каналов вычислительных машин на требуемые каналы. Количество одновременно ос5тцёствляемых соединений равно числу машин в системе.

Матрица 2 управления коммутацией Лредназначена для управления коммутационной матрицей, связи с системами прерывания вычислительных машин, разрешения конфликтных ситуаций, при наличии обращений нескольких вычислительных машин к одному каналу внешнего устройства или одной вычислительной машине, путем упорядочивания поступления требования из дешифратора.

Блок 3 управления осуществляет управление работой матрицы управления коммутацией, дешифратора, а также контроль работы каналов вычислительных машин. Через блок управления оператор может управлять работой коммутационного устройства.

Дешифратор 4 предназначен для приема, хранения, обработки запросов, поступающих на входы устройства.

Устройство может работать в двух режимах в первом - объединяет в вычислите аьную систему машины и каналы; во втором - за любой вычислительной машиной закрепляет требуемый канал и каждая машина может работать со своим каналом независимо от других.

Устройство обеспечивает установлеие связи любой вычислительной машиы с любой Мсшиной и любой вычислиельной машины с любым каналом внешт их устройств, когда количество канаов машин меньше, равно или больше j оличества каналов внешних устройств.

В первом режиме устройство работа-ет следующим образом.

Информация из канала вычислительной машина 6 (фиг. 1) поступает одно- Q временно в.матричный коммутатор 1, ешифратор 4 и блок 3 управления. На начальном этапе установления связи с каналом информация через матричный коммутатор 1 в канал не поступает.

Номер требуемого канала запоминается на входных регистрах дешифратора 4 и после обработки на соответствукяцем выходе дешифратора 4 выставляется потенциал. Число выходов дешифратора 4, связанных с матрицей 2 уп- 20 равления коммутацией равно

МК + М (М - 1),

где М - количество вычислительных машин;25- К - количество каналов внешних

устройств.

ч Такое количество выходов дешифратора 4 обеспечивает возможность обращения каждой машины к любому каналу 30 внешнего устройства и к любой вычислительной машине системы.

В матрице 2 управления коммутацией осуществляется опрос выходов дешифратора 4 через элементы 20 и 21 И. Мат- 35 рица 2 управления коммутацией содержит (для упорядочивания обращения всех машин каждому, отдельному внешнему устройству и всех машин в каждой, отдельной вычислительной машине) неза- висимо. работающие первую группу 15.1 15.m и вторую группу 18.1 - 18.К кольцевых регистров сдвига, количество которых равно К -f М, а общее количество выходов кольцевых регистров сдвига равно количеству выходов дешифра- 5 тора.

Для разрешения конфликтных ситуаций, при обращении к одному каналу внешнего устройства нескольких вычислительных машин , импульс опроса по- 50 является последовательно на выходах кольцевых регистров сдвига, которые соединены с элементами 21 И таким образом, что выход п А-го кольцевого регистра сдвига опращивает у дешифра- 55 тора выход m. К-оЙ группы дешифратора 4, где А 1,2,.3,...,К - кольцевой регистр сдвига, разрешающий обращение машины к каналу внешнего устройства; п 1,2,3,...,М - номер разряда Q кольцевого регистра сдвига; ni 1,2,3,...,М - номер выхода дешифратора 4.

Для увеличения быстродействия устройства и разрешения конфликтных ей-

туаций, при обращении машины к машине, импульсы опроса появляются последовательно на выходных шинах кольцевого регистра сдвига, которые соединены элементами 20 И таким образом, что вьоходит п-1 В-ой схемы опроса опрашивает у дешифратора выход m М-ой группы выходов, причем М т,

где В 1,2,3,...,М - кольцевой регистр сдвига,: разрешающий обращение Мс1шины к машине.

Если для данного канала внешнего устройства есть обращение одной из машин, то кольцевой регистр сдвига для этого канала,, будет остановлен до окончания обмена между машиной и внешним устройством. Аналогично при обращении к каналу вычислительной машины.

Требования вычислительных машин элементов ;20 Й- (фиг. 2) и 21 (фиг. 3) в порядке, определяемом кольцевым регистром сдвига, поступают в коммутационную матрицу- 1 (фиг. 1) .

Например, при обращении М-ой вычислительной машины к 1-ой вычислительной машине, требование, пройдя через элемент 20 И (фиг.2), второй вход которого соединен с выходом кольцевого регистра 18.1 сдвига поступит в мат ичный коммутатор 1 (фиг. 1) по шинам 12.1 (фиг.2), по шинам 13.1 - в блок управления, через элемент 14 ИЛИ - в систему прерывания, а через элемент 15.1 ИЛИ продвижение в кольцевом регистре 18.1 сдвига будет остановлено до окончания обмена М-ой машины с 1-ой машиной. После оконча-, ния обмена блокировка обращений к данной машине снимается и данная схема опроса запускается.

При совпадении импульса опроса с требованием машины на контакт с каналом матрица 2 управления коммутацией (фиг. 1) по шинам 9 выдает сигнал в систему прерывания данной машины.

Это позволяет вычислительноймашине до поступления .сигнала из комму:тирующего устройства выполнять операции, не связанные с требуег-ым каналом. Одновременно с этим коммутационная матрица 1 производит подключение канала машины к требуемому каналу.

Блок 3 управления (фиг. 1) производит контроль работы коммутирующего устройства и работы каналов. При наличии ошибки или сбоя блок управления прерывает обмен.

Оператор через блок 3 управления (фиг. 1) может остановить работу кольцевых регистров 18.1 - 18.га сдвига для обращения машины к машине и оставить в работе кольцевые регистры 19 .1 -19 .ТС для. обращения машины к внешним устройствам или, наоборот, остановить работу кольцевых регистров 19.1 - 19.К сдвига для обращения машины к внешним устройствам. а в работе сзетатййть коль девие регистры ( 18.1 - 18,т) сдвига для обращения машины к машинам. В CRTрежиме оператор управления подключает к любой вычислительной мшиинё, к нескольким МаЬиййл или ко машинам каналы, связайнйе с кЪТимутавтором 1. Это позволяет любым машинам работать в составе вычислительной систег« -и -В авОДйть из состава системы любые мгшшны. Переключение каналов осуществляет коммутационная матрица 1 под в6здействием матрицы 2 управления коммутацией. управления 3 блокирует в дешифраторе 4 поступление сигналов из машины. KpoWe того, оператор М5Жётосуществлять с матрицей 2 управ ления коммутацией такие же действия, первомр ёжиме... ;; Использование данного устройства составе вычислитejibHoft ЪК&УШШ поз 1б°Лйё упроспитS организацию коммута ции,повысить надежность рабЪтВГустройства за счгет ого, что для органи | зациГ ко1 р тации не испольэуютс вычислительные машины. Возможность .опе ратора через блок управления под-, ключ:ать любые Клашины и |саналы в ;систему и выв одить; из состйва системы любые машины и Каналыувелйчйваёт во мозйностй и гибкость вычислительной; системы, повышает ее живучесть. Йс -ключает (при программировании) необ 1 оДиМОсть указывать какие группы вы чЬсЛительных машин, входящих всисте му, для решения какой задачи будут использованы. Наличие контроля работОТГайгалйв Влоко уп1эавления1-Т{бШ й Й11Гем уст ройстве повышает надежность работы каналов. , Формула изобретения 1.Коммутационное устройстйЬ Для iiS cjiftfёлЬНой сйШёмы;ебдё жШёе матричный коммутатор и блЬк ytipaBjie- ей lie rf BfШ1:) матричного коммутатора являются соответ ственной первой и второй группой вьцсодов устройства, йёрвая группа ;834одов МИтгрЙЧНбШ :Ьймутатора соединена с первой группой входов блО :Кй ухфавленйЯ и является первой группой вводов устройства, втЬрГа:я группа Ж8Ш ;йтр1чйШ0 ШШу аРгг ся второй группой входов устройства, о т л и ч: а 10 щ е е с я тем, что с ; 1 Гёяйю повышения надежности в устройст во введён дешйф1 атор и йатрфЩЖуправления KONiMyTa4Heft;r n№ M ЙЩШШГ, вТо )етья Группы выходов матрицы управления коммутацией является соотлетственно третьей группой входов

... ;МатричНогО коммутатора, третьей группой выходов устройства и второй группой вхбдЬв блока управления, первая и Мторая группы выходов дешифратора соединены соответственно с первой группой входов матрицы управления коммутацией с третьей группой Входов блока управления, первая и вторая группа исходов йоторбго соединена соответстенно со второй, группой входов матрищл управления коммутацией,-с первой группой входов дешифратора, первая группа входов устройства соединена . . Со второй группой входов дешифратора. 2. Устройство по П.1, о т л и ч а ю щ е е с я тем, что матрица управления коммутацией содержит тактовый генератор, первую и вторую группы элементоё ИЛИ, первую группу кольцевых рё1 истров сдвига по числу вычислительных машин, входящих в систему,,третьи и четвертую группу элеменfoB ИЛИ, Втърую группу кольцевых регистров сдвига по числу внешних, устройств, входящих в систему, первую и вторую группу элементов И, причём выходы первой и третьей группы элементов „ИЛИ ЯВЛЯЮТСЯ второй группой выходов матрицы управления коммутацией, каждый вьгход элемента ИЛИ второй группы 31лёментов ИЛИ соединен с блокировочным входом Соответствующего кольцевого регистра сдвига первой группы (и четвертой группы), каждый выход элемента ИЛИ, четвертой группы .элементсэв ИЛИ соединен с блокировочным входом соответствующего кольцевого регистра сдвига второй группы, информационные йыходы каждого Кольцевого регистра сдвига первой группы соединены C nepBHNtti входами соответствующих элементов и первой группы элементов И, информаЦионные выходы каждого кольцевого регистра сдвига второй группы соединены с первым входом соответствующего элемента И второй группы элементов И, вторые входы элементов И первой и второй группа являются первой группой входов матрицы управления коммутацией, ВЫХОЩ1 элементов И первой и второй iftSynriti& eMeHtbBii являются перной и третьей группой выходов матрицы управления коммутацией, выход каждого элейенТа И первой группы элементов И соединён с соответствующим входом соответствующего элемента Ш1И первой и тзтЪрбЙ групп элементов ИЛИ, выход каждого элемента И второй группы бОёДинен с соответствующим входом соответствующего элемента ИЛИ третьей и четвертой групп элементов ИЛИ выход так.тового генератора соединен рб входом сянхронизации всех кольцевйх регистров сдвига первой и второй группы, управляющие входы каждого кольцевого регистра сдвига первой и второй групп являются второй группой

входов матрицы управления коммутаци - .......

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 1 314207, кл. G 06 F 15/16.

2.Мультипроцессорные системы и параллельные вычисления. Под ред. ф.Г.Эислоу. M.,l976jc. 196-197.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2026605C1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| МАТРИЧНЫЙ КОММУТАТОР | 1994 |

|

RU2103729C1 |

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ МОНТАЖА, ПАРАМЕТРОВ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ И ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ СЛОЖНЫХ УСТРОЙСТВ ЭЛЕКТРОАППАРАТУРЫ И ТОКОРАСПРЕДЕЛИТЕЛЬНЫХ СЕТЕЙ | 2008 |

|

RU2377585C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| Коммутатор | 1982 |

|

SU1042180A1 |

| Коммутационное устройство | 1986 |

|

SU1387006A1 |

| Матричный коммутатор | 1988 |

|

SU1596342A1 |

6

д

IF11

TFU

,;...r;-; f --

5S

Авторы

Даты

1980-07-05—Публикация

1978-04-14—Подача