1

Изобретение относится к запоминающим устройствам.

Цель изобретения - повышение быстродействия устройства,

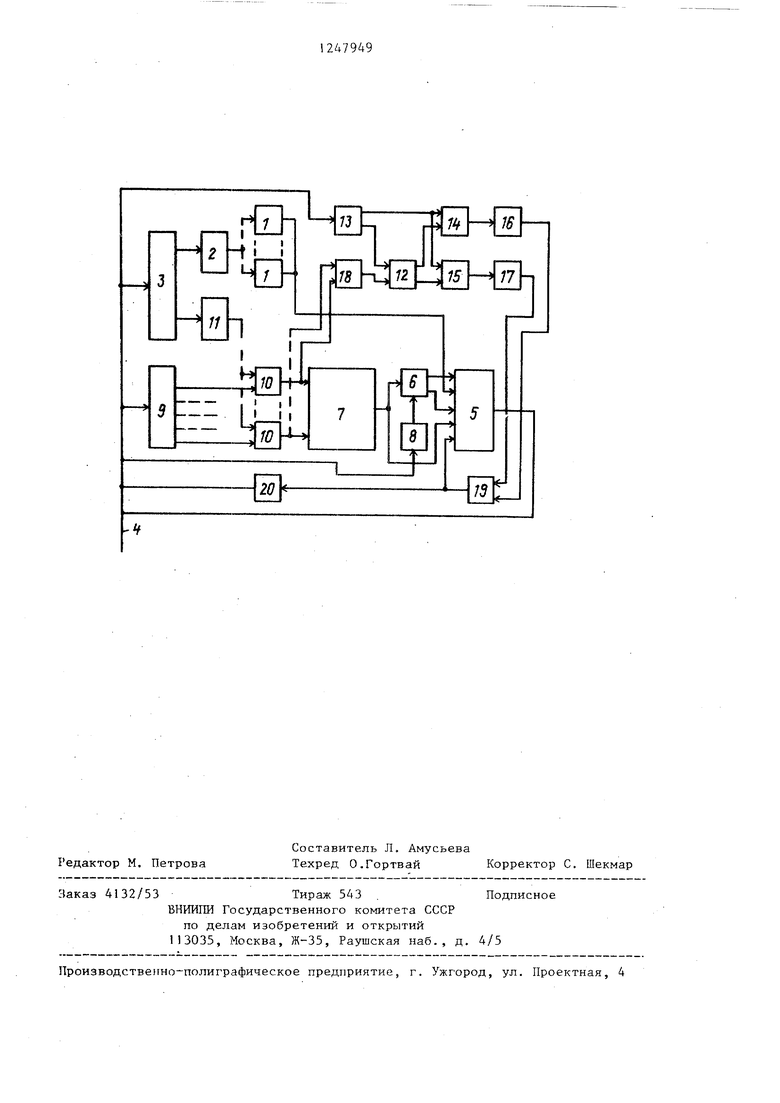

На чертеже приведена структурная схема устройства.

Устройство содержит группы накопителей 1, первый дешифратор 2, пер- вьй адресньш р егистр 3, входы адресного регистра 3 являются адресными входами 4, мультиплексор 5, блок 6 сравнения, накопитель 7, числовой регистр 8, второй адресньй регистр 9, группу элементов И 10, второй дешифратор 11, триггер 12, блок 13 задержки, два элемента И 14 и 15, первьй 16 и второй 17 одновибраторы, первый 18 и второй 19 элементы ИЛИ и третий одновибратор 20.

Устройство работает следующим образом.

В режиме считывания из шины А поступают адрес числа в адресный регистр 3, сигнал чтения на вход бпока 13 задержки и код индекса на регист-р 9. В том случае, если адрес числа содержит код зоны накопителя 7, на выходе группы элементов И 10 в соответствии с кодом регистра У вырабатывается адрес числа накопителя 7 для коррекции числа, хранящегося по соответствующему адресу в одном из накопителей i группы, которое поступает на первые входы мультиплексора 5. Однако при необходимости коррекции этого числа на второй вход мультиплексора 5 поступает сигнал с первого выхода сравнения 6, который запрещает выдачу числа из накопителей, 1 группы в шину 4, за счет того, что на первьш вход блока 6 сравнения подается код корректирующего числа из накопителя 7, а на ее второй вход - код с регистра 8, который представляет началь- ньй код числа, после которого необходима коррекция, к примеру код 0...0. При этом на третий вход мыльтиплексора 5 подается разрешающий потенциал с второго выхода блока 6 на выдачу числа, пришедшего на четвертый вход мультиплексора 5 с выхода накопителя 7, а с выхода пер вого элемента ИЛИ 18 на вход триггера 12 подается управляющий импульс,, который устанавливает его в состояние 1 (предварительно триггер 12 импульсом с первого выхода блока 13 задержки был установлен в состояние

10

15

20

25

1247949. 2

О). За счет того, что триггер 12 i находится в состоянии 1, управляющий импульс, поступающий с второго выхода блока 13 задержки, проходит , через второй элемент И 15 и запускает одновибратор 17. Длительность импульса на выходе одновибратора 17 определяет цикл обращения при наличии коррекции числа в устройстве, поскольку этот импульс через второй элемент ИЛИ 19 проходит на синхронизирующий вход мультиплексора 5 и на вход третьего одновибратора 20. Выходной импульс с третьего одновибратора 20 служит сигналом окончания цикла работы устройства. В случае, когда коррекции нет, на второй вход мультиплексора 5 поступает сигнал с первого выхода блока 6 сравнения, которьй разрешает выдачу числа, хранящегося в одном из накопителей 1, за счет отсутствия на выходе блока 6 признака коррекции, поскольку на вход блока 6 из накопителя 7 поступает код 0...0. При сравнении этого кода с начальным кодом регистра 8 на первом выходе блока 6 вырабатывается потенциал, разрешающий выдачу числа, хранящегося в одном из накопителей , а на втором выходе блока 6 вырабатывается потенциал, запрещающий выдачу числа, хранящегося в накопителе 7.

В.случае, когда коррекции нет, из накопителя 7 на первый вход блока 6 поступает код 0.,.0, а на втором входе блока 6 остается неизменным начальный код регистра 8, при этом блок 6 вырабатывает на своем первом выходе потенциал, разрешающий выдачу числа из накопителей 1, который пос- тупает на второй вход мультиплексора 5, при этом на выходе блока 6 вырабатывается потенциал, поступающий на третий вход мультиплексора 5 и запрещающий вьщачу числа из накопителя 7. В этом режиме, как и в режиме коррекции, триггер 12 импульсом с первого выхода блока 13 задержки устанавливается в состояние О и находится в этом состоянии до конца цикла работы, поскольку с выхода первого элемента ИЛИ 18 в режиме отсутствия коррекции на вход установки 1 триггера 12 не поступает управляющий импульс. За счет того, что триггер 12 находится в состоянии О, управляющий импульс, поступающий с второго выхода блока

3D

35

40

45

50

55

13 задержки, проходит через первый элемент И 14 и запускает первый одновибратор 16, Дпительность импульса на выходе одновибратора 16 определяет цикл обращения при отсутствии коррекции числа в устройстве, поскольку этот импульс через второй элемент ИЛИ 19 проходит на синхронизирующий.вход мультиплексора 5 и на вход третьего одновибратора 20, выходной импульс которого служит сигналом окончания цикла работы. За счет этого достигается меньший цикл работы устройства при отсутствии коррекции, а следовательно, увеличивается быстродействие устройства в целом.

Формула, изобретени

Постоянное запоминающее устройство, содержащее первый дешифратор, выходы которого соединены с входами соответствующих накопителей группы, выходы накопителей группы подключены к первому входу мультиплексора, выходы мультиплексора являются первым выходом устройства, входы первого дешифрат ора подключены к выходам первого адресного регистра, входы которого являются первым адресньзм входом устройства, второй дешифратор и накопитель, отличающееся тем, что, с целью повьщ1ения быстродействия устройства, в него , введены триггер, два элемента И, три одновибратора, второй адресный регистр, числовой регистр, блок сранения, блок задержки, два элемента ИЛИ и группа элементов И, первые

47949. 4

входы которых подключены к выходам второго дешифратора, входы которого подключены к соответствующим выходам первого адресного регистра, вторые входы элементов И группы подключены к выходам второго адресного регистра, входы которого являются вторым адресным входом устройства, выходы элементов И группы подключены )Q к соответствующим входам накопителя и к входам первого элемента ИЛИ, выход которого подключен к первому входу триггера, второй вход которого подключен к первому выходу блока за- 1 держки, второй выход которого подключен к первым входам первого и второ - го элементов И, вторые входы которых подключены соответственно к первому и второму выходам триггера, выход 2Q первого элемента И подключен к входу первого одновибратора, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом второго одно- 25 вибратора, вход которого подключен к выходу второго элемента И, выход второго элемента ИЛИ подключен к пятому входу мультиплексора и к входу третьего одновибратора, выход которого является вторым выходом устройства, входы числового регистра являются информационным входом устройства, а выходы подключены к второму входу блока сравнения, вход блока задержки является входом выборки 5 устройства, второй и третий входы мультиплексора соединены с выходами блока сравнения, первый вход которого соединен с выходом накопителя и четвертым входом мультиплексора.

30

Редактор М. Петрова

Составитель Л. Амусьева

Техред О.Гортвай Корректор С. Шекмар

Заказ 4132/53Тираж 543 ,Подписное

ВНдаПИ Государственного комитета СССР

по делам изобретений и открытий 1)3035, Москва, Ж-33, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления для доменной памяти | 1988 |

|

SU1566409A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| МОДУЛЬ ДЛЯ ОБМЕНА СООБЩЕНИЯМИ | 2003 |

|

RU2249849C1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

Авторы

Даты

1986-07-30—Публикация

1985-01-07—Подача