. Изобрететте относится к импульс- Hofi технике, а именно к jiorwiecKHM элементам ЭСЛ типа.

Цель изобретения - повышенна б1,1стродействия устройства.

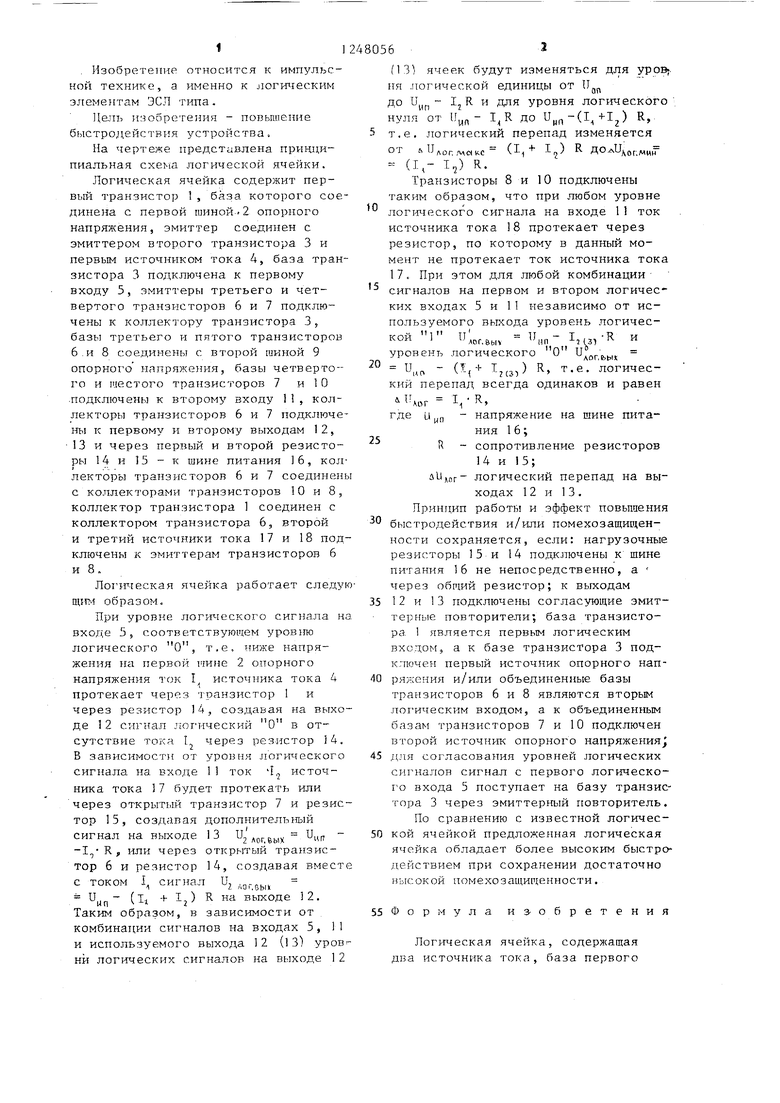

На чертеже представлена принципиальная схема логической ячейки.

Логическая ячейка содержит первый транзистор 1, база которого соединена с первой гаиной.2 опорного напряжения, эмиттер соединен с эмиттером второго транзистора 3 и первым источником тока А, база транзистора 3 подключена к первому входу 5, эмиттеры третьего и четвертого транзисторов 6 и 7 подключены к коллектору транзистора 3, базы третьего и пятого транзисторов 6.и 8 соединены с второй шиной 9 опорного напряжения, базы четвертого и шестого транзисторов 7 и 10 подключены к второму входу 1I, коллекторы транзисторов 6 и 7 подключены к первому и второму выходам 12, 13 и через первый и второй резисторы 14 и 15 - к шине питания 16, Kojr лекторы транзисторов 6 и 7 соединены с коллекторами транзисторов 10 и 8, коллектор транзистора 1 соединен с коллектором транзистора 6, второй и третий источники тока 17 и 18 подключены к эмиттерам транзисторов 6 и 8.

Лог}Г1еская ячейка работает следую образом.

При уровне логического сигнала на входе 5, соответствующем уровню логического О, т.е. ниже напряжения па первой игане 2 опорного напряжения ток 1 источника тока 4 протекает через транзистор 1 и через резистор 14, создавая на выходе 12 сигнал логический О в отсутствие тока I через резистор 14. В зависимости от уровня лоп-тческого сигнала на входе 1 1 ток 1 источника тока 17 будет протекать или через открытый транзистор 7 и резистор 15, создавая дополнительный сигнал на выходе 13 , I,,-R, или через открытый транзистор 6 и резистор 14, создавая вместе с током 1 сигнал U ... и - (ij + Ij) R на выходе 12. Таким образом, в зависимости от комбинапии сигналов на входах 5, 11 и используемого выхода 12 (13) ypoBi- ни логических сигналов на выходе 12

3) ячеек будут изменяться для УРрв-.

an

5

ня логической единицы от 11 до - Ij R и для уровня лог1гческого нуля от до ( R,. т.е. логический перепад изменяется от .MctKC- ( rj) flO U orMwif

(I,- I) R.

Транзисторы 8 и 10 подключены таким образом, что при любом уровне логютеского сигнала на входе 11 ток источника тока 18 протекает через резистор, по которому в данный момент не протекает ток источника тока 17. При этом для любой комбинации сигналов на первом и втором логических входах 5 и 11 независимо от используемого вьпсода уровень логичес- 1 и ,

кой

1П

Нзт

10

И

ЛОГ. &ы

уровень логического О U 0 р (Т

и г V - {

КИЙ перепад всегда одинаков и равен

гса)

АОГ, bbl

Т.е. логнчес лог где и

I,-R,

Mil

напряжение на шине питания 1 6; U - сопротивление резисторов

14 и 15;

ли до,-- логический перепад на выходах 12 и 13,

Лринцип работы и эффект повышения быстродействия и/или помехозащищенности сохраняется, если: нагрузочные резисторы 15 и 14 подключены к шине питания 16 не непосредственно, а через общий резистор; к выходам 12 и 13 подключены согласующие эмит- терные повторители; база транзистора 1 является первым логическим входом, а к базе транзистора, 3 подключен первый источник опорного нап- ряжения и/или объединенные базы транзисторов 6 и 8 являются вторым логическим входом, а к объединенным базам транзисторов 7 и 10 подключен второй источник опорного напряжения) для согласования уровней логических сигналов сигнал с первого логического входа 5 поступает на базу транзистора 3 через эмиттерный повторитель. По сравнению с известной логичес- кой ячейкой предложенная логическая ячейка обладает более высоким быстро- действием при сохранении достаточно нысокой помехозащищенности.

Фор мула из-обретения

Логическая ячейка, содержащая два источника тока, база первого

транзистора соединена с первой шино опорного напряжения, эмиттер соединен с эмиттером второго транзистора и первым источником тока, база второго транзистора подключена к- первому входу, эмиттеры третьего и четвертого транзисторов подключены к коллектору второго транзистора, базы третьего и пятого транзисторов соединены с второй шиной опорного напряжения, базы четвертого и шестого транзисторов подключены к второму входу, коллекторы третьего и четвертого транзисторов подключены к первому и второму выходам и соот480564

ветственно через первый и второй резисторы - к шине питания, эмиттеры пятого и шестого транзисторов , соединены, от л и ч а ю щ а я с я 5 тем, что, с целью повышения быстродействия устройства, введен третий источник тока, коллекторы третьего и четвертого транзисторов соединены соответственно с коллекторами шесто- 10 го и пятого транзисторов, коллектор первого транзистора соединен с кол- лектором третьего транзистора, а второй и третий источники тока подключены к эмиттерам третьего и пятого транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент на переключении тока | 1988 |

|

SU1631714A1 |

| Логический элемент | 1984 |

|

SU1200413A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Д-триггер с селектором на входе | 1989 |

|

SU1707741A1 |

| Логический элемент | 1985 |

|

SU1285589A1 |

| Преобразователь уровня сигнала для усилителя считывания | 1983 |

|

SU1134966A1 |

| Д-триггер ЭСЛ - типа | 1989 |

|

SU1644368A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Компаратор напряжения | 1989 |

|

SU1653149A1 |

Изобретение относится к импульс ной технике, в частности к лог№1ес- ким элементам. Цель изобретения повьппение быстродействия логического элемента достигается введением третьего источника тока и новыми функциональными связями между транзисторами. Логическая ячейка содержит транзисторы 1,3,6,7 и 8, источники тока 4, 17 и 18, резисторы 14 и 15, шины 2 и 9 опорного напряжения, шину 16 питания. Для согласования уровней логических сигналов сигнал с первого логического входа 5 поступает на базу транзистора 3 через эмиттернмй повторитель. По сравнению с известной логической ячейкой предложенная ячейка обладает более высоким быстродействием при сохранении высокой помехозащигаенности. ил. сл

| Логический элемент | 1984 |

|

SU1200413A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Алексенко А, Г., Шагурин И, И | |||

| Микросхемотехника, М.: Радио и связь, 1982, с | |||

| Спускная труба при плотине | 0 |

|

SU77A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-07-30—Публикация

1985-01-08—Подача