Изобретение относится к импульс- ной технике и предназначено для использования в логических устройствах различного назначения, содержащих элементы ЭСЛ-типа

Цель изобретения - увеличение надежности в работе логического элемента путем уменьшения амплитуды импульсов помехи на выходе.

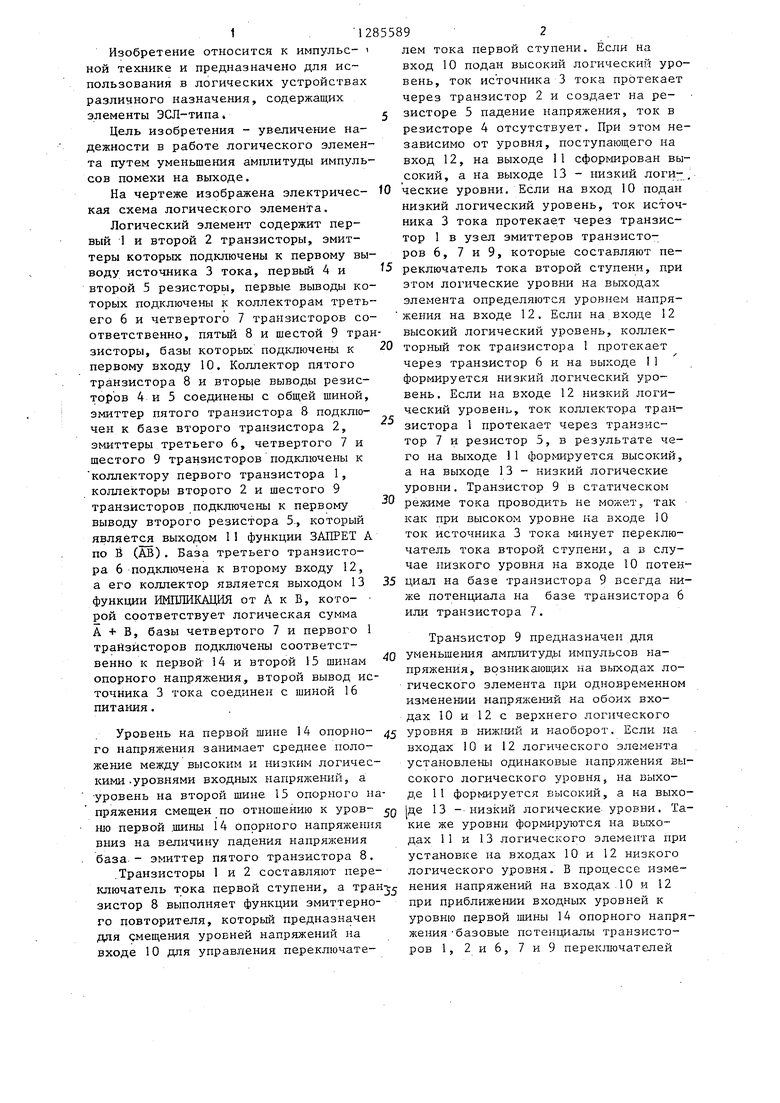

На чертеже изображена электричес- кая схема логического элемента.

Логический элемент содержит первый 1 и второй 2 транзисторы, эмиттеры которых подключены к первому выводу источника 3 тока, первый 4 и второй 5 резисторы, первые выводы которых подключены к коллекторам третьего 6 и четвертого 7 транзисторов соответственно, пятьш 8 и шестой 9 транзисторы, базы которых подкгдачены к первому входу 10, Коллектор пятого транзистора 8 и вторые выводы резисторов 4 и 5 соединены с общей шиной, эмиттер пятого транзистора 8 подключен к базе второго транзистора 2, эмиттеры третьего 6, четвертого 7 и шестого 9 транзисторов подключены к коллектору первого транзистора 1, коллекторы второго 2 и шестого 9 транзисторов подключены к первому выводу второго резистора 5., который является выходом 11 функции ЗАПРЕТ А по В (АВ). База третьего транзистора 6 подключена к второму входу 12, а его коллектор является выходом 13 функции ИМПЛИКАЦИЯ от А к Б, кото- рой соответствует логическая сумма А + В, базы четвертого 7 и первого 1 транзисторов подключены соответственно к первой 14 и второй 5 шинам опорного напряжения, второй вывод источника 3 тока соединен с шиной 16 питаьшя.

Уровень на первой шине 14 опорно- го напряжения занимает среднее поло- же1-ше между высоким и низким логическими-уровнями входных напряжений, а уровень на второй шине 15 опорного напряжения смещен по отношению к уров- ню первой .шины 14 опорного напряжения вниз на величину падения напряжения база.- эмиттер пятого транзистора 8.

.Транзисторы 1 и 2 составляют переключатель тока первой ступени, а тра зистор 8 выполняет функции эмиттерно- го повторителя, который предназначен для смещения уровней напряжений на входе 10 для управления переключате5

5 0 5

с Q

лем тока первой ступени. Если на вход 10 подан высокий логический уровень, ток источника 3 тока протекает через транзистор 2 и создает на резисторе 5 падение напряжения, ток в резисторе 4 отсутствует. При этом независимо от уровня, поступающего на вход 12, на выходе 11 сформирован высокий, а на выходе 13 - низкий логи-, ческие уровни. Если на вход 10 подан низкий логический уровень, ток источника 3 тока протекает через транзистор 1 в узел эмиттеров транзисторов 6, 7 и 9, которые составляют переключатель тока второй ступени, при этом логические уровни на выходах элемента определяются уровнем напряжения на входе 12. Если на входе I2 высокий логический уровень, коллекторный ток транзистора 1 протекает через транзистор 6 и на выходе 11 формируется низкий логический уровень. Если на входе 12 низкий логический уровень, ток коллектора транзистора 1 протекает через транзистор 7 и резистор 5, в результате чего на выходе 1 формируется высокий, а на выходе 13 - низкий логические уровни. Транзистор 9 в статическом режиме тока проводить не может, так как при высоком уровне на входе 10 ток источника 3 тока минует переключатель тока второй ступени, а в случае низкого уровня на входе 10 потенциал на базе транзистора 9 всегда ниже потенциала на базе транзистора 6 или транзистора 7.

Транзистор 9 предназначен для уменьшения амплитуды импульсов напряжения, возникающих на выходах логического элемента при одновременном изменении напряжений на обоих входах 10 и 12 с верхнего логического уровня в нижний и наоборот. Если на входах 10 и 12 логического элемента установлены одинаковые напряжения высокого логического уровня, на выходе 11 формируется высокий, а на выхо- де 13 --низкий логические уровни. Такие же уровни формируются на выходах 11 и 13 логического элемента при установке на входах 10 и 12 низкого логического уровня. В процессе изменения напряжений на входах, 10 и 12 при приближении входных уровней к уровню первой шины 14 опорного напряжения базовые потенциалы транзисторов 1, 2 и 6, 7 и 9 переключателей

31285589

тока сказываются приблизительно равными и ток источника 3 тока делится между транзисторами 1 .и 2, а коллекторный ток транзистора I делится между транзисторами 6, 7 и 9, В результате на выходе 11, на котором должен сохраниться высокий логический уровень, возникает отрицательный импульс напряжения, а на выходе 13, на котоФормула изобретения Логический элемент, содержащий

ром должен сохраниться низкий логи- Ю - транзисторов, эмиттеры первого и второго транзисторов через источник тока соединены с шиной пита- йия, эмиттеры третьего и четвертого транзисторов подключены к коллектору первого транзистора, а их коллекторы подключены сортветственно через первый и второй резисторы-к общей шине, -база пятого транзистора со- едикена с первым входом, коллектор пятого транзистора соединен общей шиной, коллектор второго транзистора подключен к коллектору четвертого транзистора, база третьего транзистора соединена с вторым входом, а базы четвертого и первого транзисторов подключень соответственно к первой и второй шинам опорного напряжения, отличающийся тем, что, с целью увеличения надежности в работе, эмиттер шестого транзистора подключен к коллектору первого транзистора, коллектор подключен к коллек тору второго транзистора, база соединена с первым входом, а эмиттер пятого транзистора соединен с базой второго транзистора.

ческий уровень, возникает положитель ный импульс. Причиной возникновения этих импульсов является разделение тока коллектора транзистора 1 между транзисторами 6, 7 и 9, амплитуда импульсов пропорциональна части тока ответвляющейся в эмиттер транзистора 6. Наличие транзистора 9 позволяет эту часть уменьшить, так как ток коллектора транзистора 1 разделяется между транзисторами 6, 7 и 9 обратно пропорционально их эквивалентным эмиттерным сопротивлениям. Эффективность транзистора 9 тем вьше, чем больше площадь его эмиттерного р-п- перехода и меньше сопротивления базовой области.

Таким образом, предлагаемое техническое решение позволяет снизить амплитуду импульсов помех, возникаю- щих на выходах двухступенчатого элемента РШШ1ИКАЦИЯ от А к В, ЗАПРЕТ А по В при одновременном одинаковом изменении входных логических уровСоставитель А. Янов Редактор Н. Тупица Техред Л.Олейник

Ко По

7535/57 Тираж 899

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

нен, что повышает надежность логических элементов либо их быстродействие за счет уменьшения логического перепада без ухудшения помехоустойчивости.

Формула изобретения Логический элемент, содержащий

- транзисторов, эмиттеры перво

го и второго транзисторов через источник тока соединены с шиной пита- йия, эмиттеры третьего и четвертого транзисторов подключены к коллектору первого транзистора, а их коллекторы подключены сортветственно через первый и второй резисторы-к общей шине, -база пятого транзистора со- едикена с первым входом, коллектор пятого транзистора соединен общей шиной, коллектор второго транзистора подключен к коллектору четвертого транзистора, база третьего транзистора соединена с вторым входом, а базы четвертого и первого транзисторов подключень соответственно к первой и второй шинам опорного напряжения, отличающийся тем, что, с целью увеличения надежности в работе, эмиттер шестого транзистора подключен к коллектору первого транзистора, коллектор подключен к коллектору второго транзистора, база соединена с первым входом, а эмиттер пятого транзистора соединен с базой второго транзистора.

Корректор А. Обручар Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Мультиплексор | 1986 |

|

SU1378048A1 |

| Дешифратор | 1986 |

|

SU1336251A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Устройство задержки | 1989 |

|

SU1793535A1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

Изобретение относится к импульс ной технике и может быть использовано в логических устройствах различного назначения, содержащих элементы ЭСЛ-типа. Цель изобретения - увеличение надежности в работе логического элемента путем уменьшения.амплитуды импульсов помехи на выходе. Устройство содержит транзисторы 1, 2, 6, 7, 8 и 9 и резисторы 4 и 5. Для достижения поставленной цели в устройстве изменены внутренние связи. ил. (Л о х ел сд 00 со

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-23—Публикация

1985-08-01—Подача