12

Изобретение относится к области вычислительной техники и может быть использовано в системах обработки информации, поступающей от большого числа быстродействующих внешних уст- ройств, а также в системах управления объектами в реальном масштабе времени.

Целью изобретения является расширение функциональных возможностей устройства за счет оргйнизации многоуровневой системы прерьтания,

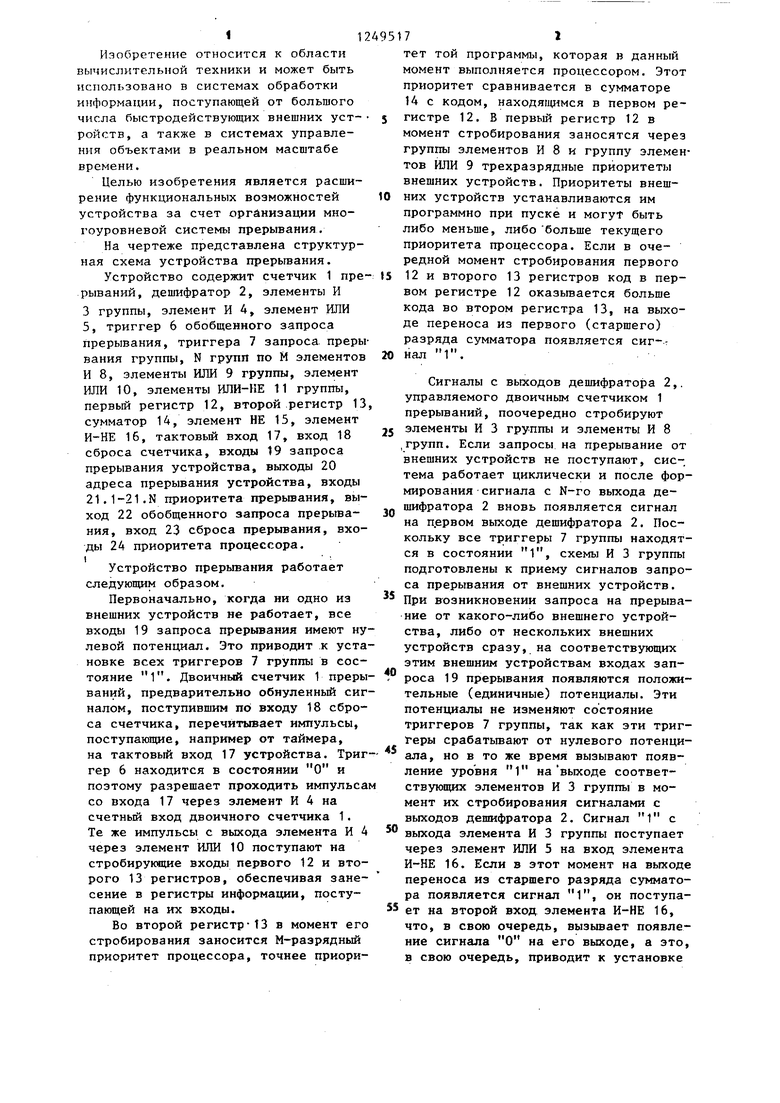

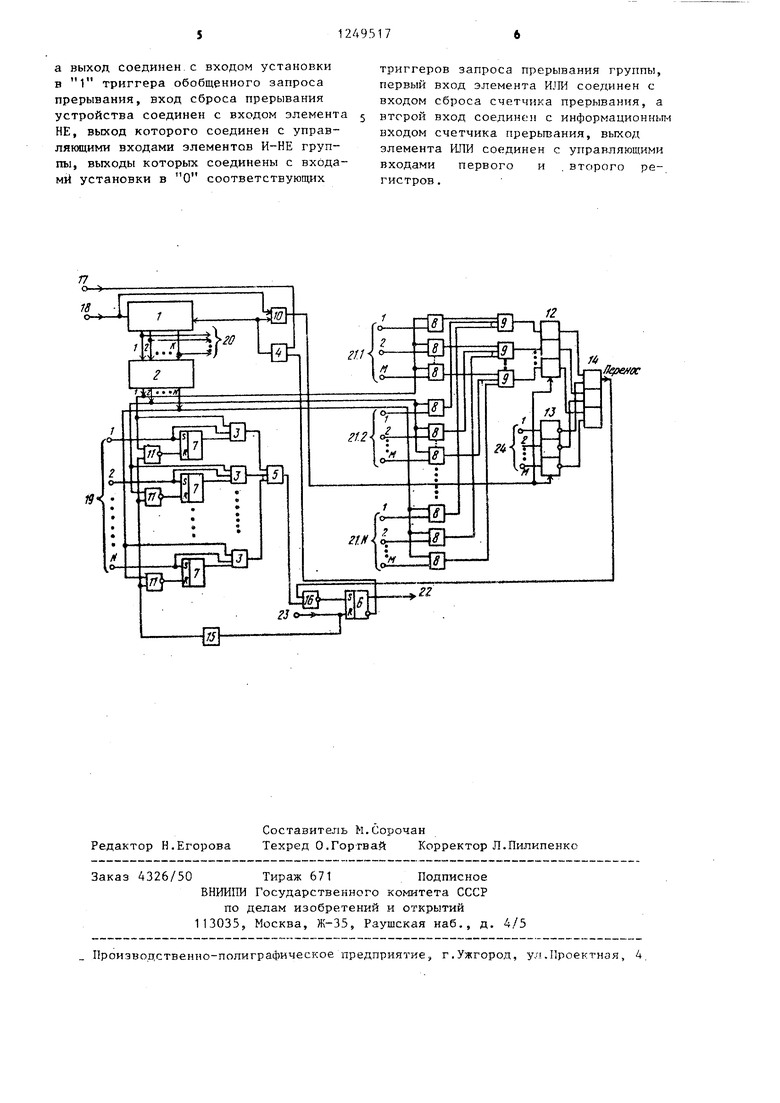

На чертеже представлена структурная схема устройства прерывания.

Устройство содержит счетчик 1 пре- рываний, дешифратор 2, элементы И 3 группы, элемент И 4, элемент ИЛИ 5, триггер 6 обобщенного запроса прерывания, триггера 7 запроса прерывания группы, N групп по М элементов И 8, элементы ИЛИ 9 группы, элемент ИЛИ 10, элементы ИЛИ-НЕ 11 группы, первый регистр 12, второй регистр 13 сумматор 14, элемент НЕ 15, элемент И-НЕ 16, тактовый вход 17, вход 18 сброса счетчика, входы 19 запроса прерывания устройства, выходы 20 адреса прерывания устройства, входы 21.1-21.N приоритета прерьшания, выход 22 обобщенного запроса прерыва- ния, вход 23 сброса прерывания, входы 24 приоритета процессора.

Устройство прерывания работает следующим образом.

Первоначально, когда ни одно из внешних устройств не работает, все входы 19 запроса прерывания имеют нулевой потенциал. Это приводит к установке всех триггеров 7 группы в состояние 1. Двоичный счетчик 1 преры ваний, предварительно обнуленньй сигналом, поступившим по входу 18 сброса счетчика, перечитывает импульсы, поступающие, например от таймера, на тактовый вход 17 устройства. Триг гер 6 находится в состоянии О и поэтому разрешает проходить импульса со входа 17 через элемент И 4 на счетный вход двоичного счетчика 1. Те же импульсы с выхода элемента И 4 через элемент ИЛИ 10 поступают на стробирующие входы первого 12 и второго 13 регистров, обеспечивая занесение в регистры информации, поступающей на их входы.

Во второй регистр-ТЗ в момент его стробирования заносится М-разрядный приоритет процессора, точнее приори

5

51

5 0 0

1 5® 55

5

7I

тет той программы, которая в данный момент выполняется процессором. Этот приоритет сравнивается в сумматоре 14 с кодом, находя1димся в первом регистре 12. В первый регистр 12 в момент стробирования заносятся через группы элементов И 8 и группу элементов ИЛИ 9 трехразрядные приоритеты внешних устройств. Приоритеты внешних устройств устанавливаются им программно при пуске и могут быть либо меньше, либо больше текущего приоритета процессора. Если в очередной момент стробирования первого 12 и второго 13 регистров код в первом регистре 12 оказьгаается больше кода во втором регистра 13, на выходе переноса из первого (старшего) разряда сумматора появляется сиг-т нал 1.

Сигналы с выходов дешифратора 2,. управляемого двоичным счетчиком 1 прерываний, поочередно стробируют элементы И 3 группы и элементы И В ,групп. Если запросы на прерывание от внешних устройств не поступают, сие-, тема работает циклически и после формирования сигнала с N-ro выхода дешифратора 2 вновь появляется сигнал на первом выходе дешифратора 2. Поскольку все триггеры 7 группы находятся в состоянии 1, схемы И 3 группы подготовлены к приему сигналов запроса прерывания от внешних устройств. При возникновении запроса на прерывание от какого-либо внешнего устройства, либо от нескольких внешних устройств сразу, на соответствующих этим внешним устройствам входах запроса 19 прерывания появляются положительные (единичные) потенциалы. Эти потенциалы не изменяют состояние триггеров 7 группы, так как эти триггеры срабатьгоают от нулевого потенциала, но в то же время вызывают появление уровня 1 на выходе соответствующих элементов И 3 группы в момент их стробирования сигналами с выходов дешифратора 2. Сигнал 1 с выхода элемента И 3 группы поступает через элемент ИЛИ 5 на вход элемента И-НЕ 16. Если в этот момент на выходе переноса из старшего разряда сумматора появляется сигнал 1, он поступает на второй вход элемента И-НЕ 16, что, в свою очередь, вызывает появление сигнала О на его выходе, а это, в свою очередь, приводит к установке

триггера 6 обобщенного запроса прерывания в состояние 1. Такая ситуация означает, что запрос на прерывание, поступивший от внешнего устройства, имеет приоритет больше, чем у процессора.

Установка триггера 6 в состояние 1 приводит, с одной стороны, к появлению сигнала на выходе 22 обобщенного запроса прерывания, а, с другой стороны, к запрету прохождения им- цульсов со входа 17 через элемент И на двоичный счетчик 1 прерываний. Счетчик 1 прерываний останавливается и на его выходах фиксируется код адреса прерывания, соответствующий номеру внешнего устройства, вызвавшего прерывание. Обобщенный запрос на прерывание, поступив в процессор, вь)зс- вет переход к процедуре обработки прерывания. После выполнения данной процедуры в устройство прерывания поступит сигнал 23 сброса прерывания (уровнем О). Этот сигнал вызовет появление на инверсном выходе триггера 6 уровня 1 и, кроме того, поступит через элемент НЕ 15 на элементы И-НЕ 11 группы. В результате на

выходе одной из схем И 11 группы, а именно на той, которая соответствует внешнему устройству, вызвавшему пре- рьшание, появится сигнал с уровнем О. Данный сигнал установит соответ- {ствующий триггер 7 группы в состояние

О, что, в конечном счете, приведет к исчезновению сигнала уровнем М на одном из входов элемента И 16. Таким образом триггер 6 окончательно установится в состояние О, что вызовет исчезновение обобщающего запроса на прерывание на выходе 22 устройства.

Формула изобретенияУстройство прерывания, содержащее k-разрядный счетчик прерьтания, где N 2, а N - количество входов запроса прерывания, дешифраторi группу из N элементов И, элемент И, элемент ИЛИ и триггер обобщенного запроса прерывания, причем выходы счетчика прерывания соединены с соответствующими входами дешифратора и являются выходами адреса прерывания устройства, выходы дешифратора соединены с первыми входами соответствующих элементов И группы, вторые вхо5

o

5

5

ды элементов И группы являются входами запроса прерывания устройства, выходы элементов И группы соединены с входами элемента ИЛИ, инверсный выход триггера обобщенного запроса прерывания соединен с первым входом элемента И, второй вход которого является тактовым входом устройства, а выход соединен с счетным входом счетчика прерывания, прямой вход триггера обощенного запроса прерывания является выходом обобщенного . запроса прерьшания устройства, а вход t:6poca прерьшания устройства соединен с входом установки в О триггера обобщенного запроса прерьшания, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет 0 организации многоуровневой системы прерывания, оно дополнительно содержит группу триггеров запроса прерывания, N дополнительных групп из М элементов, где М - количество уровней прерывания, группу из М элементов ИЛИ, второй элемент ИЛИ, группу из N элементов И-НЕ, первый и второй регистры, сумматор, элемент НЕ и элемент И-НЕ, причем третьи входы элементов И группы соединены с прямыми выходами соответствующих триггеров запроса прерывания группы, а входы установки в 1 триггеров запроса прерывания группы соединены с соответствующими входами запроса прерывания устройства, i-й (i 1... N) вьпсод дешифратора соединен с управляющими входами элементов И i-й дополнительной группы и информационным входом i-ro элемента И-НЕ группы, информационные входы элементов fcN дополнительных групп являются входами приоритета устройства, а выходы соединены с входами соответству- , ющих элементов ИЛИ группы, выходы которых соединены с соответствующими информационными входами первого регистра, выходы которого соединены с соответствующими входами первой группы сумматора, входы второй группы которого соединены с соответствующими инверсными выходами второго регистра, информационные входы которого являются входами приоритета устройства, выход переноса из старшего разряда сумматора соединен с первым входом элемента И-НЕ, второй вход которого соединен с выходом элемента ИЛИ,

0

5

0

0

5

а выход соединен с входом установки в 1 триггера обобщенного запроса прерывания, вход сброса прерывания устройства соединен с входом элемента НЕ, выход которого соединен с управляющими входами элементов И-НЕ группы, выходы которых соединены с входами установки в О соответствующих

триггеров запроса прерывания группы, первый вход элемента ИЛИ соединен с входом сброса счетчика прерывания, а второй вход соединен с информационньп-i входом счетчика прерьтания, выход элемента ИЛИ соединен с управляющими входами первого и . второго регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания программ | 1981 |

|

SU1001103A1 |

| Устройство прерывания | 1982 |

|

SU1084795A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Многоканальное устройство ввода информации | 1988 |

|

SU1529238A1 |

| Устройство прерывания | 1978 |

|

SU877542A1 |

| Устройство для прерывания программ | 1978 |

|

SU736101A1 |

| Управляемое устройство приоритета | 1984 |

|

SU1182519A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1176341A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах обработки информации с большим числом равно- значньпс внешних устройств. Данное изобретение решает задачу повышения производительности устройства при обработке информации, поступающей от множества равнозначных быстродействующих внешних устройств. Система прерывания включает в себя двоичный счетчик, дешифратор, отдельные триггеры запросов прерываний, регистры приоритетов, сумматор и элементы комбинационной логики (И, ИЛИ, НЕ. Двоичный счетчик циклически опрашивает линии прерьшаний от внешних устройств и соответствующие им линии приорите та. Если на опрашиваемой линии имеется запрос на прерывание и его приоритет на данный момент оказывается больше приоритета процессора, счетчик останавливается и происходит прерьтание процессора. После окончания процедуры прерывания счетчик вновь продолжает считать,, что дает возможность новому запросу на прерьтвание, имеющему высокий приоритет, вызвать прерывание процессора. Каждый раз, когда счетчик останавливается и происходит прерьшание, код на выходах разрядов счетчика указьшает адрес прерывания. 1 ил. (Л N Nf; СП

-i&HW- -- fjo-,

fZ

iJ O&fOC

М

Редактор Н.Егорова

Составитель М.Сорочан

Техред О.Гортвай Корректор Л.Пилипенко

Заказ 4326/50 Тираж 671 Подписное БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,, г.Ужгород, ул.Проектная, 4

| Балашов Е.П., Пузанков Д.Б | |||

| Микропроцессоры и микропроцессорные системы | |||

| М.: Радио и связь, 1981, с.155-15-8 | |||

| Стары Я | |||

| Микропроцессорные системы | |||

| Сборник | |||

| М.: Энергоиздат, 1981, с.153-154. |

Авторы

Даты

1986-08-07—Публикация

1985-01-29—Подача