Изобретение относится к измери-. тельной технике и может быть использовано в радиоэлектронных системах обработки и анализа формы сигналов, в частности при контроле микросхем по форме переходного процесса динамического тока потребления.

Целью изобретения является повышение, точности сравнения формы сигналов за счет компенсации погрешностей и расширение области применения путем расширения динамического диапазона сравниваемых сигналов за счет дифференциального сравнения форм

.сигналов. I

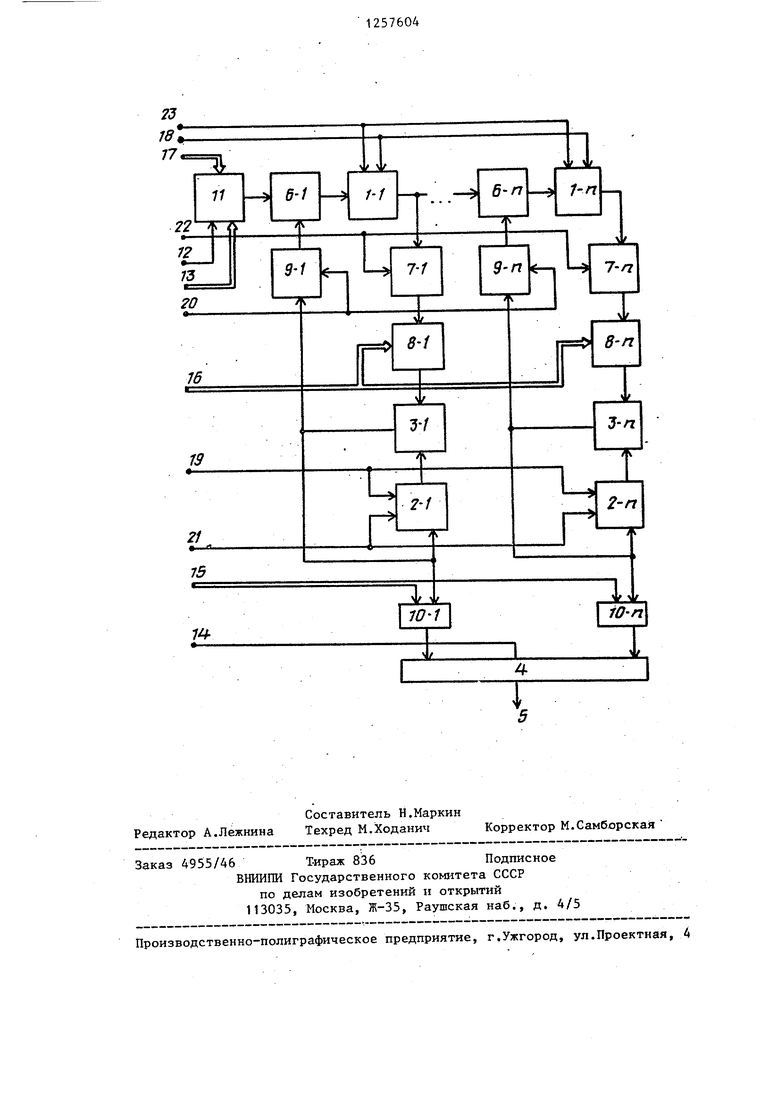

На чертеже приведена-структурная схема компаратора формы сигналов.

Компаратор формы сигналов содержит п интеграторов первой группы 1-1s...,1-n, п интеграторов второй группы 2-1,...,2-п, п элементов сравнения 3-1,.,.,3-п, элемент И 4, выход которого является выходом 5 устройства, выход каждого г-го интегратора второй группы 2-п подключен к первому входу п-го элемента сравне- . иия 3-п, сум1)аторы 6-1,,.,,6-п, аналоговые запоминающие элементы 7-1, ,,,, 7-п, усилители с программируемым коэффициентом усиления 8-1,,.,, 8-п, интеграторы третьей группы 9-1, ,,,,9-п, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 10-1,,,., 10-п, коммутатор 11, входы которого подключены к шинам исследуемого 12 и эталонных 13 сигналов, а выход подключен к первому входу первого сумматора 6-1 цепи .последовательно-поочередно соединенных сумматоров б-1,,,,,6-п и интеграторов первой .группы 1-1,.,,,1-п, при эТом выход каждого п-го интегратора первой группы 1-п через последовательно соединенные п-й аналоговый запоминающий элемент 7-п и п-й усилитель с программируемым коэс1)фициентом усиления 8-п подсоединен к второму входу п-го элемента сравнения 3-п, а выход п-го элемента сравнения 3-П Подклю-; чен к первому входу п-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10-п и информацион- ,ным входам п-х интеграторов, второй 2-п и третьей 9-п групп, причем выход п-го интегратора третьей группы 9-п подсоединен к второму входу п-го сумматора 6-п, а выходы всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10-1,.,.,10-п подключены к входам элемента И 4, дополнительный вход которого подсоеди57604J

нен к шине 14 разрешения сравнения, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10-1,..,,10-п подключены к шинам

15программирования результата срав- 5 нения, управляющие входы усилителей

с программируемым коэффициентом уси-.- ления 8-1,,..,8-п соединены с шинами

16программирования чувствительности, управляющие входы коммутатора 11 под10 ключены к шинам 17 выбора режима работы, входы разрешения интегрирования интеграторов первой группы 1-1,

. ..,,1-п соединены с шиной- 18 разрешения интегрирования входных сигна15 лов, входы разрешения интегрирования интеграторов второй группы 2-2, . .,,2-п - с шиной 19 компенсации мультипликативной погрешности, а входы разрешения интегрирования интегра20 торов третьей группы 9-1,,..,9-п . с шиной 20 слежения-запоминания фор- мы сигнала с компенсацией аддитивной погрешности, входы сброса интеграторов второй группы 2-1,,,,, 2-п

25 йодключены к шине 21 начальной установки, управляющие входы аналоговых запоминающих элементов 7-1,.,,, 7-п соединены е шиной 22 запоминания интегральньк значений, входы

30 сброса интеграторов первой группы

1-1,,,.,1-п подключены к шине 23 подготовки к интегрированию.

Компаратор формы сигналов работает следующим образом,

35 Для запоминания формы эталонного сигнала на шины 17 выбора режима ра-. боты подается комбинация управляющих сигналов, обеспечивающая подключение через коммутатор 11 к цепи пос ледоваТельно соединенных сумматоров и первых интеграторов соответственно 6-1,,,,,6-п и 1-1,..,,1-п эталонного сигнала f с шины 13, На шину 20 слежения запоминания формы сигнала по дается сигнал управления, соответствующий слежению, т.е. сигнал разрешения интегрирования интеграторами третьей группы 9-1-9-п разности интегральных значений на выходах пер50 вых интеграторов к нулевого уровня сигнала, обеспечиваемого сбросом интеграторов второй группы 2-1,..., 2-п при подаче на шину 21 сигнала, соответствующего начальной установ55 ке устройства. Процесс стхежения осуществляется за определенное количество циклов интегрирования эталонного входного сигнала f до тех пор.

пока на выходах интеграторов первой группы 1-1., ...,1-п не установятся нулевые значения. При этом на выхо- дах интеграторов третьей группы 9-Г, ...,9-п образуются средние за время интегрирования интегральные значения с обратным знаком, которые соответствуют средним интегральньгм значениям эталонного сигнала с учетом аддитивной погрешности всего тракта преобразования и сравнения. Каждый цикл интегрирования обеспечивается выполнением последовательно следующих операций: сброса интеграторов первой группы 1-1,..,,1-п по шине 23 подготовки к интегрированию; интегрирования при подаче сигнала по шине 18 разрешения интегрирования вход- них сигналов} запоминания интегральных значений с их переписью в анало-

говые -запоминающие элементы 7-1

7-п при подаче соответствующего СИ1- нала по шине 22 устройства на их уп- .равляющие входы с последующим переходом из режима выборки в режим хра- нения.

Процесс слежения заканчиваемся подачей на шину 20 в определенный момент времени сигнала, соответствую . щего переходу интеграторов третьей группы 9-1, .. . ,9-п в режим з апомина- Iния. Компенсация нестабильности коэффициентов преобразования, зависящей, в основном, от нестабильности интеграторов первой группы 1-1,...,1-п, осуществляется регулировкой уровней уставок, значения которых задаются интеграторами второй группы 2-1,..., 2-п. При подаче на входы 17 выбора режима работы устройства комбинации сигналов, обеспечивающей подключение через коммутатор 11 эталонного сигнала д+ uf, после каждого цикла интегрирования на выходах интеграторов первой группы 1-1, .. ., 1 -п образуются интегральные значения, соответствующие сигналу i f. Подачей управляющих сигналов на шины 16 программирования чувствительности осуществляется задание определенных уровней уставок, ко торые отслеживаются интеграторами второй группы 2-1,...,2-п, на входы разрешения интегрирования которьш по шине 19 компенсации мультипликативной погрешности подается- соответ ствуюшд1й уровень сигнала. При этом сигнал на шине 21 начальной установки снимается. В определенный момент

времеии установки на выходах интеграторов второй группы 2-1,...,2-п требуемых значений уставок снимается сигнал на шине 19 устройства и интеграторы второй группы 2-12-п

переходят в режим запоминания. Таким образом, устройство подготовлено к сравнению формы эталонного сигнала f и исследуемого f, так как на интеграторах третьей группы 9-1,,.., 9-п запомнены значения, соответствующие средним интегральным значениям эталонного сигнала с обратным знаком с учетом аддитивной составляющей погрешности, а на интеграторах второй группы 2-1,,..,2-п - уровни установок сравнения с учетом мультипликативной составляющей погрешности такта преобразования. При подаче на шипы 17 выбора режима работы устройства комбинации сигналов, обеспечивающей подключение через коммутатор 11 исследуемого сигнгша f, после первого цикла интегрирования на выходах интеграторов первой группы 1-1,..,,, 1-п образуются интегральные значения, соответствую1цие разностному сигналу f-fQ, Подачей на шины 16 программирования чувствительности наперед заданной комбинации сигналов осуществляется масштабирование ожидаемого отличия формы сигнала по отношению к сигналу uf, В зависимости от логики работы последующих устройств может быть интересньм не только результат совпадения формы сигналов, но и их определенные отличия, что обеспечивается заданием соответствующих сигналов По вторым входам элементов ИСКЛЮ ЧАЮЩЕЕ ИЛИ 1 О-1,...,10-п. С учетом задержек, вносимых элементами устройства, с появлением установившегося результата сравнения на вход 14 разрешения сравнения подается управляющий сигнал, обеспечивающий вьщачу результата сравнения.

Таким образом, за счет идентичности трактов преобразования зталонно -о и исслед,уемого сигналов обеспечивается возможность компенсации погрешностей и расширения динаш1ческого диапазона пре: Сразования разностного - сигнала.

55 Формула изобретения

Компаратор формы сигналов, содержащий шины, входного и исследуемого

сигналов, n интеграторов первой группы, п интеграторов второй группы, n элементов сравнения, элемент И, выход которого является выходом устройства, вьгход каждого п-го интегра- тора второй группы подсоединен к первому входу п-го элемента сравнения, отличающийся тем, что, с целью повышения точности сравнения и расишрения области применения за счет увеличения динамического диarfa- зона сравниваемых сигналов, в него дополнительно введены шина разрешения сравнения, шины программирования

результата сравнения, шины программи- js соединены к шинам программирования

рования чувствительности, шины выбора режима работы, шина разрешения интегрирования, шкна компенсации мультипликативной погрешности, пгина слежения-запоминания формы сигнала с компенсацией аддитивной погрешности, шина начальной установки, шина запоминания интегральных значений, щина подготовки к интегрированию, соответственно п сумматоров, п аналоговых запоминающих элементов, п усилителей с программируемым коэффициентом, усиления, п интеграторов третьей группы, и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, коммутатор, входы которого подключены к шинам исследуемого и эталонных сигналов, а выход подсоединен к первому входу первого сумматора цепи последовательно-поочередно соединенных п сумматоров и п интеграторов первой группы, при этом выход каждого п-го интегратора первой группы- через последовательно соединенные п-й аналоговый запоминающий элемент и п-й усилитель с программируемым коэффициентом усиления подсоединен к второму входу п-го элемента сравнения, а выход п-го элемента сравнения подсоединен к первому входу п-го элеме} та ИС-КЛЮЧАЮЩЕЕ 11ЛИ и

5 информационным входам п интеграторов второй и третьей групп, причем выход п-го интегратора третьей группы подсоединен к второму входу п-го сумматора, а выходы всех элементов ИСКПЮ10 ЧАЮЩЕЕ ИЛИ подсоединены к соответствующим входам элемента И, допол- нительный Вход которого подсоединен к шине разрешения сравнения. вторь е входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подрезультата сравнения, управляюш;ие входы усилителей с программируемым коэффициентом усиления соединены с шинами программирования чувствительности,управляющие входы коммутатора подключены к шинам выбора режима ра- боты, входы разрешения интегрирования интеграторов первой группы сое- с шиной разрешения интегрирования входньпг сигналов, входы разрешения интегрирования интеграторов второй группы - с ши Ной компенсации мультипликативной погрешности, а входы разрешения интегрирования интеграторов третьей группы - с шиной слежения-запоминания формы сигнала с компенсацией аддитивной погрешности, входы сброса интеграторов второй группы подсоединены к шине начальной

установки, управляющие входы аналоговых запоминающих элементов соединены с шиной запоминания интегральных значений, входы сброса интегра- торрв первой группы подсоединены к шине подготовки к интегрированию.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующее устройство | 1985 |

|

SU1251125A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| Способ компенсации обменной мощности в электрической системе | 1987 |

|

SU1525771A1 |

| Интерполятор | 1986 |

|

SU1334167A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Устройство для управления реостатным торможением двигателей транспортного средства | 1984 |

|

SU1240649A1 |

| Коммутационный преобразователь электрической мощности | 1986 |

|

SU1348743A1 |

| Последовательно-параллельный многоканальный интегрирующий преобразователь | 1988 |

|

SU1566376A1 |

| Интегратор хроматографических данных | 1981 |

|

SU991443A1 |

| Система автоматического регулирования турбины | 1982 |

|

SU1060797A1 |

Изобретение относится к измерительной технике и может быть использовано, в частности, при контроле микросхем по форме переходного процесса динамического тока потребления. Цель изобретения - повышение точности сравнения формы сигналов и расширение области применения. Устройство содержит группы интеграторов, элемент Н, элементы сравнения, сумматоры, аналоговые запоминающие элементы, усилители, элементы ИСКЛЮЧАКЯЦЕЕ ИЛИ, коммутатор и шины исследуемого и эталонного сигналов. Наличие шины разрешения сравнения, шины программирования результата сравнения, шины программирования чувствительности, шины выбора режима работы, шины разрешения интегрирования входных сигналов, шины .компенсации мультипликативной погрешности, шины слежения-запоминания формы сигнала с компенсацией ади-о тивной погрешности, шины начальной установки, шины запоминания интегральных значений и шины подготовки к интегрированию и соединение их с элементами устройства компенсирует погрешности и расширяет динамический диапазон сравниваемых, сигналов за счет 5ИФФspeнциaльнoгo сравнения форм сйг напов. 1 ил. ю(Л

| Макаров Р.А | |||

| Средства технической диагностики машин | |||

| М.: Наука, 1981, С | |||

| Плуг с фрезерным барабаном для рыхления пласта | 1922 |

|

SU125A1 |

| Компаратор формы моноимпульсных сигналов | 1982 |

|

SU1115217A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-15—Публикация

1985-02-08—Подача