t

Изобретение относится к вычислительной технике и может быть использовано в составе многопроцессорных выч11слительных систем как быстродействующее многофункциональное вычис- лительное устройство для вычисления произведения трех или двух переменных, квадрата или куба числа, а так- I же произведения квадратного числа на произвольный код.

Целью изобретения является расширение функциональных возможностей за счет возможности вычисления функций t (zx и .

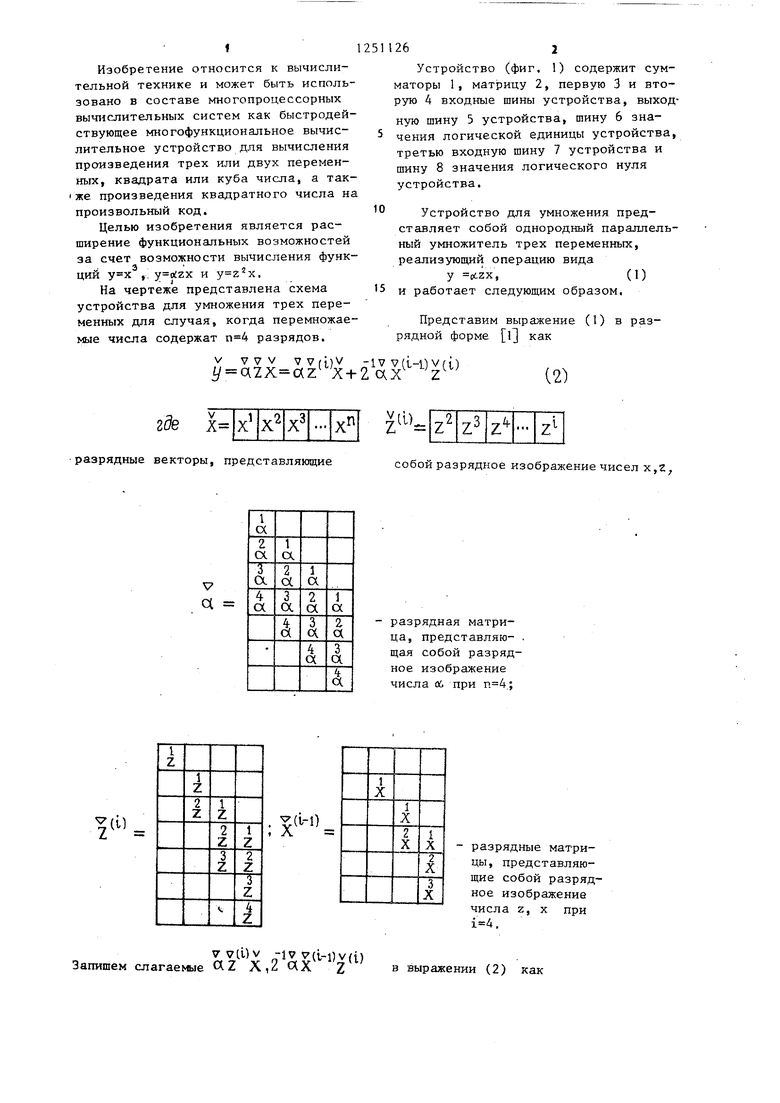

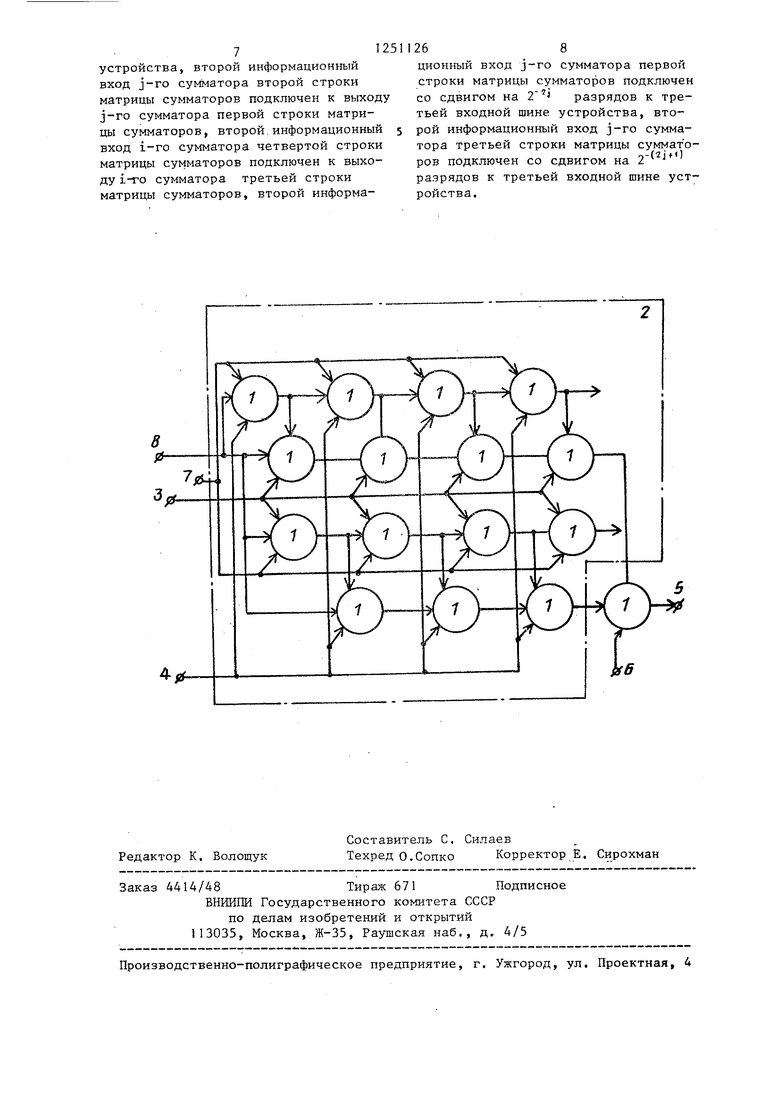

На чертеже представлена схема устройства для умножения трех переменных для случая, когда перемножаемые числа содержат разрядов.

V VVV VVfilV -IVVfi-lWn l

i/ azx az x-h2 (xF z

разрядные векторы, представляющие

V 01

v,t,

. (t-1)

« л

7 7ti)v -17 7(i-l)vn)

Запишем слагаемые «Z Х,2 аХ Z

1262

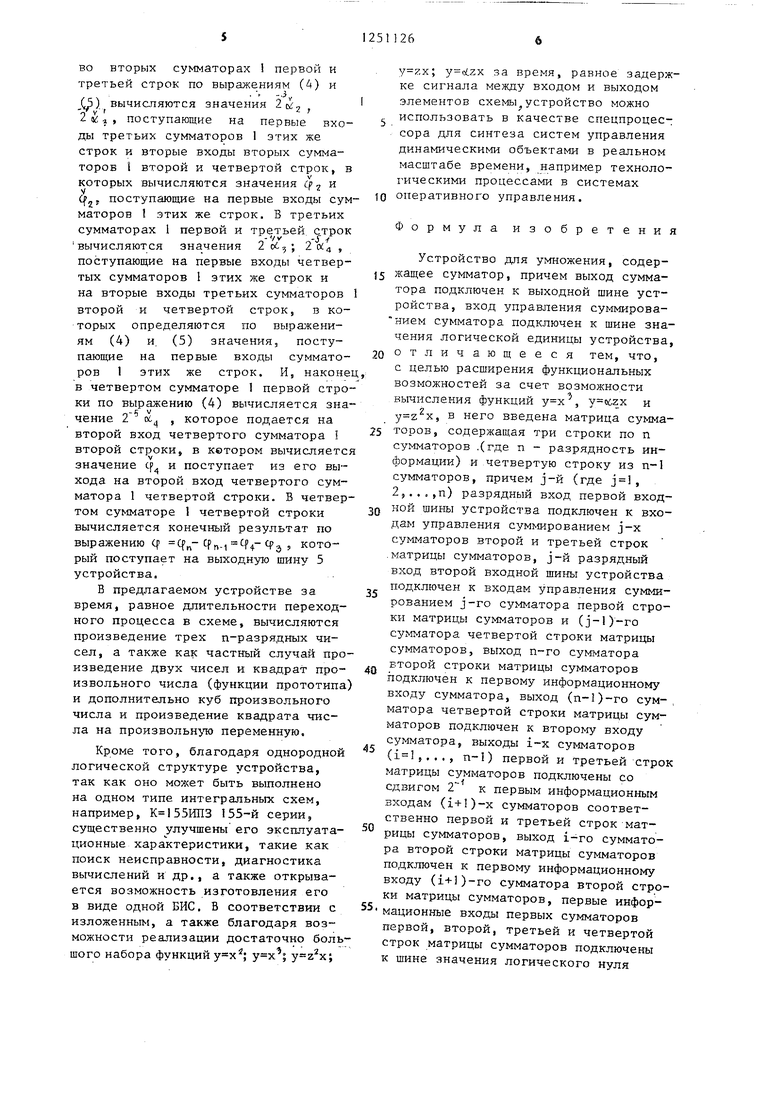

Устройство (фиг. 1) содержит сумматоры 1, матрицу 2, первую 3 и вторую 4 входные шины устройства, выходную шину 5 устройства, шину 6 значения логической единицы устройства, третью входную шину 7 устройства и шину 8 значения логического нуля устройства.

Устройство для умножения представляет собой однородный параллельный умножитель трех переменных, реализующий операцию вида

у ix.zx,(1)

и работает следующим образом.

Представим выражение (I) в разрядной форме l как

(2)

собой разрядное изображение чисел х,г.

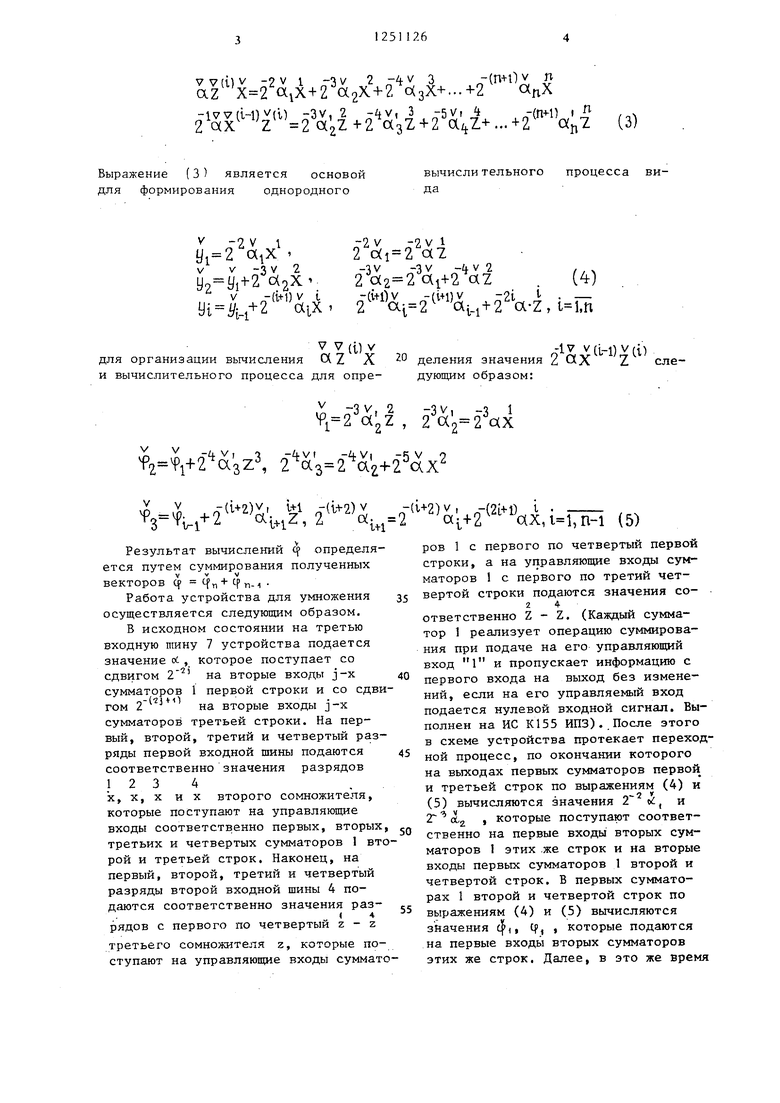

разрядная матрица, представляющая собой разрядное изображение числа л при ,;

разрядные матрицы, представляющие собой разрядное изображение числа Z, X при ,

в выражении (2) как

vv(i)v -2V 1 -3V 2 n

az ajX+2 a2X+2 сХзХ+...+2 «nX

-lvv(l-l)) -3V, 2 -ifV, 3 -5Vr -(ПЧ) I

2 cxx z 20( a3Z + ...+2

Выражение (3) является основой для формирования однородного

V 3V 2 У1+2 ( -(1+1) V L

i/H+2 txtx

V V (t) V

для организации вычисления CX Z X

и вычислительного процесса для опреV

, , (

,

vp 4.о) 7 , 2 а

Результат вычислений определяется путем суммирования полученных векторов CF Ч п + п-1

Работа устройства для умножения осуществляется следующим образом.

В исходном состоянии на третью входную тину 7 устройства подается значение ос , которое поступает со сдвигом на вторые входы j-x сумматоров 1 первой строки и со сдвигом 2 на вторые входы j-x сумматоров третьей строки. На первый, второй, третий и четвертый разряды первой входной щины подаются соответственно значения разрядов

1234

х, X, X их второго сомножителя,

которые поступают на управляющие входы соответственно первых, вторых третьих и четвертых сумматоров 1 втрой и третьей строк. Наконец, на первый, второй, третий и четвертый разряды второй входной шины 4 подаются соответственно значения раз( 4 рядов с первого по четвертый z - z

третьего сомножителя z, которые поступают на управляющие входы суммат(3)

вычисли тельного да

процесса ви2 , -3V -ЗУ -4 V 2 2 ai4-2 az ;rcH)v

(4)

-Citljv -(1+15V -2i I .

2 X-1+2 a-z, ,n

деления значения дующим образом:

2l§(l-i)vci)

слеU1

я..,i lTTPi (5)

ров 1 с первого по четвертый первой строки, а на управляющие входы сум5

0

5

0

5

маторов 1 с первого по третий четвертой строки подаются значения со2 4

ответственно Z - Z. (Каждый сумматор 1 реализует операцию суммирования при подаче на его управляющий вход 1 и пропускает информацию с первого входа на выход без изменений, если на его управляемый вход подается нулевой входной сигнал. Выполнен на ИС К155 ИПЗ)..После этого в схеме устройства протекает переходной процесс, по окончании которого на выходах первых сумматоров первой и третьей строк по выражениям (4) и

вычисляются значения 2 «1

-2

И

(5)

Т 2. I которые поступают соответственно на первые входы вторых сумматоров 1 этих .же строк и на вторые входы первых сумматоров 1 второй и четвертой строк. В первых сумматорах 1 второй и четвертой строк по выражениям (4) и (5) вычисляются зйачения с(, р, j которые подаются на первые входы вторых сумматоров этих же строк. Далее, в это же время

во вторых сумматорах первой и третьей строк по выражениям (А) и () вычисляются значения 2 2 1Й, , поступающие на первые вхо- ды третьих сумматоров 1 этих же строк и вторые входы вторых сумматоров 1 второй и четвертой строк, в которых вычисляются значения ер и поступающие на первые входы сум маторов 1 этих же строк. В третьих сумматорах 1 первой и третьей, строк вычисляются зна чения 2 схС, ; 2 « 9 поступающие на первые входы четвертых сумматоров 1 этих же строк и на вторые входы третьих сумматоров второй и четвертой строк, в которых определяются по выражениям (4) и, (5) значения, поступающие на первые входы суммато- ров 1 этих же строк. И, наконе в четвертом сумматоре 1 первой строки по выражению (4) вычисляется зна- С V

чение 2 обц , которое подается на второй вход четвертого сумматора I второй строки, в квтором вычисляетс значение ср и поступает из его выхода на второй вход четвертого сумматора 1 четвертой строки. В четвертом сумматоре 1 четвертой строки вычисляется конечный результат по выражению ср „,, , который поступает на выходную шину 5 устройства.

В предлагаемом устройстве за время, равное длительности переходного процесса в схеме, вычисляются произведение трех п-разрядных чисел, а также как частный случай произведение двух чисел и квадрат про- извольного числа (функции прототипа и дополнительно куб произвольного числа и произведение квадрата числа на произвольную переменную.

Кроме того, благодаря однородной логической структуре устройства, так как оно может быть выполнено на одном типе интегральных схем, например, К 155ИПЗ 155-й серии, существенно улучшены его эксплуата- ционные характеристики, такие как поиск неисправности, диагностика вычислений и др., а также открывается возможность изготовления его в виде одной БИС. В соответствии с изложенным, а также благодаря возможности реализации достаточно большого набора функций

y(lzx за время, равное задержке сигнала между входом и выходом элементов схемы,,устройство можно использовать в качестве спецпроцессора для синтеза систем управления динамическими обьектами в реальном масштабе времени, например технологическими процессами в системах оперативного управления.

Формула изобретени

Устройство для умножения, содержащее сумматор, причем выход сумматора подключен к выходной шине устройства, вход управления суммирова- нием сумматора подключен к шине значения логической единицы устройства отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности вычисления функций , .zx и , в него введена матрица сумматоров, содержащая три строки по п сумматоров .(где п - разрядность информации) и четвертую строку из п-1 сумматоров, причем j-й (где j, 2,..,,п) разрядный вход первой входной шины устройства подключен к входам управления суммированием j-x сумматоров второй и третьей строк .матрицы сумматоров, j-й разрядный вход второй входной шины устройства подключен к входам управления суммированием j-ro сумматора первой строки матрицы сумматоров и (j-l)-ro сумматора четвертой строки матрицы сумматоров, выход п-го сумматора второй строки матрицы сумматоров подключен к первому информационному входу сумматора, выход (n-l)-ro сумматора четвертой строки матрицы сумматоров подключен к второму входу сумматора, выходы i-x сумматоров (,..,, п-1) первой и третьей стро матрицы сумматоров подключены со сдвигом 2 к первым информационным входам (i+)-x сумматоров соответственно первой и третьей строк матрицы сумматоров, выход i-ro сумматора второй строки матрицы сумматоров подключен к первому информационному входу (i+l)-ro сумматора второй строки матрицы сумматоров, первые информационные входы первых сумматоров первой, второй, третьей и четвертой строк матрицы сумматоров подключены к шине значения логического нуля

71251

устройства, второй информационный вход j-ro сумматора второй строки матрицы сумматоров подключен к выходу j-ro сумматора первой строки матрицы сумматоров, второй,информационный 5 вход i-ro сумматора четвертой строки матрицы сумматоров подключен к выходу i-To сумматора третьей строки матрицы сумматоров, второй информа268

ционный вход j-ro сумматора первой строки матрицы сумматоров подключен со сдвигом на 2 разрядов к третьей входной шине устройства, второй информационный вход j-ro сумматора третьей строки матрицы суммат о- ров подключен со сдвигом на 2 разрядов к третьей входной шине устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Однородная вычислительная структура для @ разложения матриц | 1984 |

|

SU1249531A1 |

| Однородная параллельная вычислительная структура для вычисления произведения матрицы на вектор | 1984 |

|

SU1236500A1 |

| Устройство для вычисления суммы квадратов К @ -разрядных чисел | 1981 |

|

SU993256A1 |

| Однородная вычислительная структура | 1985 |

|

SU1251104A1 |

| Асинхронный матричный вычислитель обратных тригонометрических функций | 1982 |

|

SU1132286A1 |

| Вычислительное устройство | 1985 |

|

SU1291978A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1108440A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

Изобретение относится к вычислительной технике и может быть использовано в составе многопроцессорных вычислительных систем как быстродействующее многофункциональное вычислительное устройство для вычисления произведения трех или двух переменных, квадрата или куба числа, а также произведения квадрата числа на произвольный код. Целью изобретения является расширение функциональ- ных возможностей за счет возможностей вычисления функций , и X. Устройство содержит матри- . цу из (4п-1) сумматоров, сумматор, три входные шины устройства и выходную шину устройства. В предлагаемом устройстве за время, равное длительности переходного процесса, в схеме вычисляется произведение трех п-разрядных чисел, а также как частный случай вычисляется произведение двух чисел и квадрат, произвольного числа и дополнительно вычисляются куб произвольного числа и произведения квадрата на произвольную переменную. 1 ил. , Q (Л to СП ю а

4

Редактор К. Волощук

Составитель С. Силаев

Техред О.Сопко Корректор Е, Сирохман

Заказ 4414/48Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для умножения трех переменных | 1981 |

|

SU1024908A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для регулирования передвижения пленки в фотографическом аппарате | 1927 |

|

SU9207A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-02—Подача