Изобретение относится к вычислительной технике и может быть применено в автономно специализированных вычислителях или в комплексе в. большой ЭВМ в качестве функциональ- ного расширителя.

Целью изобретения является расширение класса решаемых задач за счет возможности вычисления выражения виг.Z.X

да - .

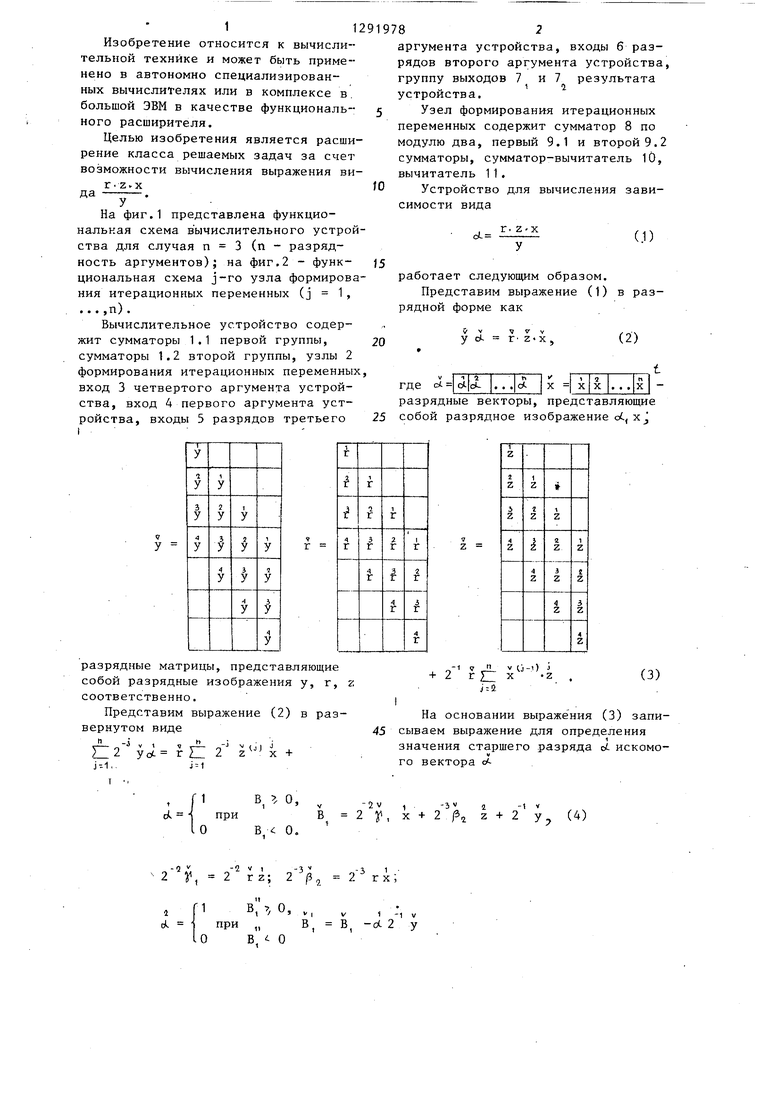

На фиг.1 представлена функциональная схема в ычислительного устройства для случая п 3 (п разрядность аргументов); на фиг.2 - функ- циональная схема j-ro узла формирования итерационных переменных (j 1 , ...,п).

Вычислительное устройство содержит сумматоры 1.1 первой группы, сумматоры 1.2 второй группы, узлы 2 формирования итерационных переменных вход 3 четвертого аргумента устройства, вход 4 первого аргумента устройства, входы 5 разрядов третьего

7 У

т

„- V V 0-1) J + 2 г J3I 2 j S.

(3)

разрядные матрицы, представляющие собой разрядные изображения у, г, 7. соответственно.I

Представим выражение (2) в раз- На основании выраже ния (3) запи- вернутом виде45 сываем выражение для определения

у n - О) j ,значения старшего разряда d искомоjT J-,го вектора сА.

I

t fl В, . О, -2V , -3V ,

й1 -( при В 2 у, X + 2 /3 Z + 2 у., (4)

О

В, 0.

-1 -1 ч -1 « -л 1 .

2 У, 2 rz;

i Г1 В, 7, О, ,, , при „ В, В, -оС 2 у 10 В i О

аргумента устройства, входы 6 разрядов второго аргумента устройства, группу выходов 7 и 7 результата устройства.

Узел формирования итерационных переменных содержит сумматор 8 по модулю два, первый 9.1 и второй 9.2 сумматоры, сумматор-вычитатель 10, вычитатель 11.

Устройство для вычисления зависимости вида

dL

г. Z-х

(.1)

работает следующим образом.

Представим выражение (1) в разрядной форме как

Y ч V V V

У с. г Z X

(2)

и

X 1

где а

разрядные векторы, представляющие

собой разрядное изображение ot xj

„- V V 0-1) J + 2 г J3I 2 j S.

(3)

1291978

и в общем случае для вычисления каж-

дого последующего значения разряда

(jC, j

. 1 В. ,о, ,

о1 - при В. В +2

Iо J 1

10 В, i 0.

1

J-1

d. © d 1,

пру.

, s- J-i

И d. Q.

I

(jC, j 1 сооответственно как

- 21 -, -J V

У. +.2 Р,,. Z - у;

(5)

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный вычислитель | 1985 |

|

SU1265765A1 |

| Матричный вычислитель | 1985 |

|

SU1283791A1 |

| Матричный вычислитель | 1985 |

|

SU1247864A1 |

| Вычислительное устройство | 1985 |

|

SU1272330A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Вычислительное устройство для поворота вектора | 1982 |

|

SU1109742A1 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1476462A1 |

| Устройство для деления | 1986 |

|

SU1381492A1 |

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Матричный вычислитель | 1989 |

|

SU1647558A1 |

Устройство может быть использовано автономно в специализированных вычис лителях или в комплексе с большой ЭВМ в качестве функционального расширителя. Целью изобретения является расширение класса решаемых задач за счет возможности вычисления выражений видаоС Х г Z/y. Устройство содержит сумматоры 1.1 первой группы, сумматоры 1.2 второй группы, узлы 2 формирования итерационных переменных, входы 3,4,5,6 аргументов, выходы 7, 7 результата. Вычисление производится на основе оперирования с числами, представленными в разряднотаналоговой форме. Совокупность уравнений (по числу разрядов в числах) реализуется последовательно за один такт в узлах вычисления итерационных переменных 2, аргументы для вычисления которых представляют сумматоры первой группы 1.1 и второй группы 1.2. 2 ил. сл tsD О ;о 00

-(ij+1)

« J г X

Результат вычислений при этом представляется как

ct

Б каждом J-M сумматоре первой группы сумматоров 1.1 образуется значение 2 которое поступает на вход второго слагаемого (j-fD-ro сумматора первой группы сум- маторов 1.1 со сдвигом на один разряд в сторону младших разрядов.

В каждом J-M сумматоре второй группы сумматоров 1 .2 образуется зна-(j + i) л чение 2 Т , которое поступает

на вход второго слагаемого (j + 1)-ro сумматора этой группы со сдвигом на один разряд в сторону мпадших разрядов

В каждом J-M узле формирования итерационных переменных формируются на сумматоре-вычитателе 10 и вычитателё 1.1 значения знаковых разрядов по выра/ г Ч V

жению (5)oL,c(-,. На выходе вычитателя 11 вычисляется значение В ,. На выходе сумматора 8 по модулю два образуется значение . Значения знаковых разрядов oL, с/., поступают на выходные шины j j

7, Tj . Значение В j поступает на вход второго слагаемого второго сумматора 9.2 (j +1) -го узла формирования итерационных переменных. Значение j поступает на управляющий вход сумматора-вычи- тателя (j + 1)-ro узла формирования итерационных переменных.

Группа выходов i , ы ,,..., ы образуе группу выходов результата устройства.

25

5

0

-30

5

0

Вычислительное устройства является однородным, т.е. содержит одинаковые элементы и связи для всех j, таких как 1 j с п. При j 1 отличие заключается в том, что на вход второго слагаемого второго сумматора 9.2 первого узла формирования итерационных переменных поступает значение нуля, а на управляющий вход сум- матора-вычитателя 10 этого узла поступает сигнал, определяющий режим вычитания.

При j п не существует связей от сумматора 1.1 первой группы, сумматоров 1.2 второй группы, узла 2 формирования итерационных переменных к следующим соответствующим элементам и узлам.

1 Формула изобретения

Вычислительное устройство, содержащее первую группу сумматоров,причем вход первого аргумента устройства соединен со сдвигом на 2j разрядов в сторону младших разрядов с входом первого слагаемого j-ro сумматора первой группы (,...,n) j(n - разрядность аргументов), вход j-ro разряда второго аргумента устройства соединен с входом стробиро- вания первого слагаемого j-ro сумматора первой группы, отличающееся тем, что, с целью расширения класса решаемых задач за счет Возможности вычисления выражения вида ot

, в него дополнительно

введены вторая группа сумматоров и группа узлов формирования итерационных переменных, причем каждый узел формирования итерационных переменных групп содержит два сумматора, сумматор-вычитатель, вычитатель и сумматор по модулю два, причем вход первого аргумента устройства соединен со сдвигом на (2J+1) разрядов в сторону младших разрядов с входом первого слагаемого j-ro сумматора второй группы, вход j-ro разряда третьего аргумента устройства соединен с входом стробирования первого слагаемого j-ro сумматора второй группы, выходы i-x сумматоров (,

.., п-1) первой и второй групп соединены со сдвигом на один разряд в сторону младших разрядов с входами вторых слагаемых (i+1)-x сумматоров первой и второй групп соответственно, вход четвертого аргумента устройства соединен со сдвигом на j разрядов в сторону младших разрядов с входом вычитаемого вычитателя и входом первого слагаемого сумматора-вы- читателя j-ro узла формирования итерационных переменных, выходы j-x сумматоров первой и второй групп соединены с входами первых слагаемых соответственно первого и второго сумматоров j-ro узла формирования итерационных переменных, вход j-ro разряда третьего аргумента устройства соединен с входом стробирования первого слагаемого второго сумматора j-ro узла формирования итерационных

.

/ /

переменных, вход j-ro разряда второго аргумента устройства соединен с входом стробирования первого слагаемого первого сумматора j-ro узла формирования итерационных переменных, выход второго сумматора j-ro узла формирования итерационных переменных соединен с входом второго слагаемого первого сумматора этого узла, выход первого сумматора j-ro узла формирования итерационных переменных соединен с входом второго слагаемого сумматора-вычитателя этого узла, информационный вход и выход

5

управления сложением-вычитанием сумматора-вычитателя и входом второго слагаемого второго сумматора (i+1)-ro узла формирования итерационных переменных, группа выходов знаковых разрядов сумматоров-вычитателей и вычитателей узлов формирования итерационных переменных группы является группой выхЬдов результата устройства.

Составитель С, Куликов Редактор Н. Лазаренко Техред И.Попович Корректор С. Черни

Заказ 272/48Тираж 673 - Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

| Вычислительное устройство | 1981 |

|

SU1086426A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Стасюк А.И | |||

| Однородные многофункциональные матричные процессоры,Киев.: 1983 (Препринт АН УССР, Институт электродинамики, № 351), с | |||

| Насос | 1917 |

|

SU13A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-23—Публикация

1985-07-08—Подача