/V

00 Од 00

эо ел

1

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения арифметико-логических устройств ЭВМ и спецпроцессоров.

Цель изобретения - расширение функциональных возможностей за счет реализации операцийсложения и вычитания над о ратньмикодами двоичных чисел.

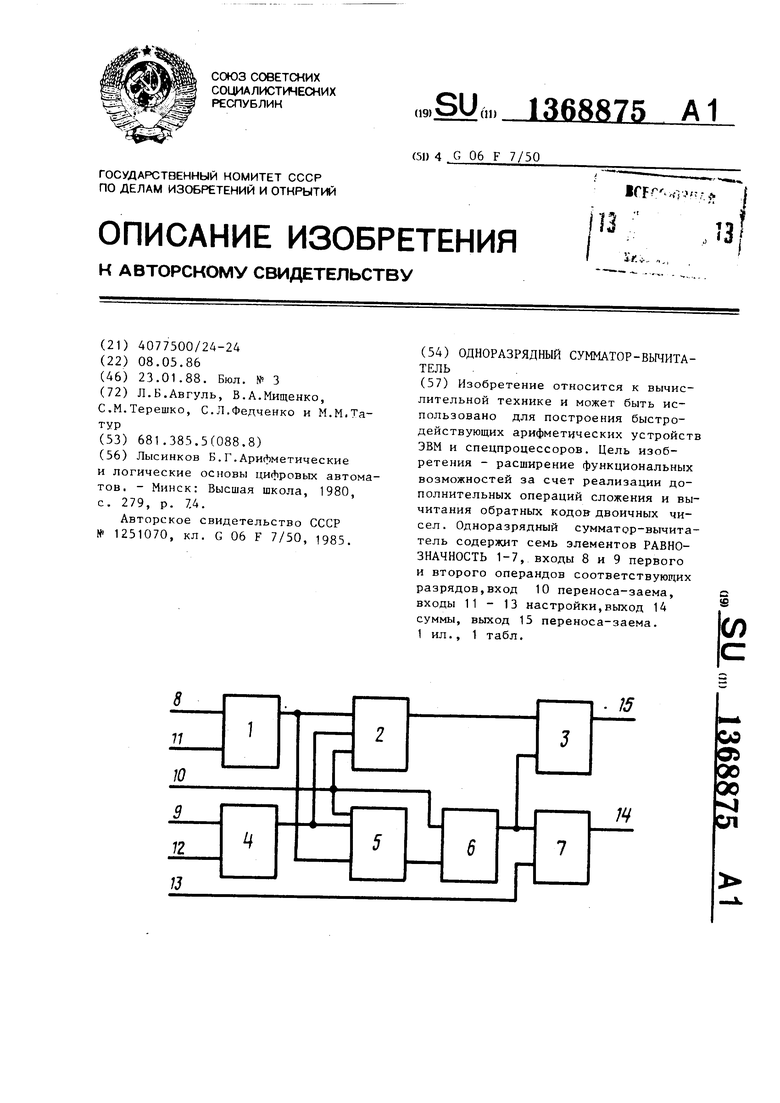

На чертеже представлена схема предлагаемого одноразрядного сумма- тора-вычитателя.

Одноразрядный сумматор-вычита- тель содержит элементы РАВНОЗНАЧНОСТЬ 1- 7, вход 8 i-ro разряда первого операнда, вход 9 i-ro разряда второго операнда, вход 10 переноса- заема из (i-l)-ro разряда, 11 - 13 настройки, выход 1А суммы- разности i-ro двоичного разряда, выход 15 переноса-заема в (1+1)-й разряд.

Устройство работает следующим об- райом.

На вход 8 подается прямой код i-r разряда первого операнда х, , на на вход 9 - прямой код i-ro разряда второго операнда yj, на вход 10 - сигнал переноса-заема из (i-l)-ro разряда Р;, , на входы 11... 13 - сигналы настройки U ,... Uj соответственно. На выходе 14 реализуется логическая функция, соответствующая значению суммы-разрядности i-M двоичном разряде, на выходе 15 логическая функция,.соответствующая сигналу переноса-заема в (i+1)-й разряд.

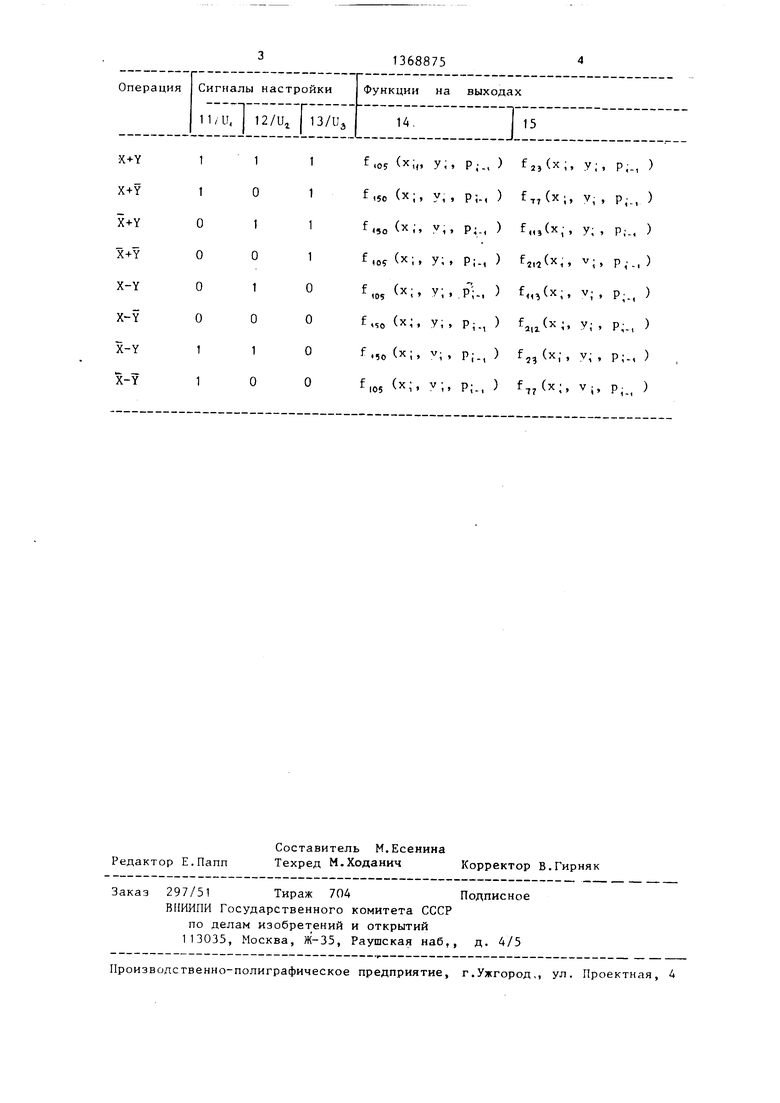

Коды настроек на выполнение восьми арифметических операций приведены в таблице..

Достоинством предлагаемого устройства являются широкие функциональные возможности, простая конструкция, однородная структура и высокое быстродействие.

Формула

и

2

зоб

р е т е н и я

5

0

5

0

5

40

45

Одноразрядный сумматор-вычитатель, содержащий элементы РАВНОЗНАЧНОСТЬ, причем вход i-ro разряда первого операнда сумматора-вычитателя, i 1, п, п-разрядность операндов соединен с первым входом первого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с первым настроечным входом сумматора-вычитателя, а выход соединен с первым входом второго элемента РАВНОЗНАЧНОСТЬ и первым входом третьего элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом четвертого элемента РАВНОЗНАЧНОСТЬ, а второй вход соединен с входом переноса-заема из (i-1)-ro разряда сумматора-вычитателя и вторым входом второго элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом пятого элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с выходом переноса-заема в ()-й разряд сумматора-вычитателя, отличающий- с я тем,что,с целью расширения функциональных возможностей за счет реализации операций сложения и вычитания над обратными кодами двоичных чисел, вход i-ro разряда второго операнда соединен с певрым входом шестого элемента РАВНОЗНАЧНОСТЬ, второй вход которого сЪединен с вторым настроечным входом сумматора-вычитателя, а выход соединен с третьим входом второго элемента РАВНОЗНАЧНОСТЬ и вторым входом четвертого элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с вторым входом пятого элечента РАВНОЗНАЧНОСТЬ и первым входом седьмого элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с третьим настроечным входом сумматора-вычитателя, а выход-соединен с выходом суммы-разности i-ro разряда сумматора-вычитателя.

1 1

0 0 0 0

1 1

1

0

1

0

1

0

1

0

1

1 1

0 0 0 0

f,o5 (xi,,y;,p... )f2,(x;,

f (50 (x;,y,.p;-, )f 77 (x;.

f (50 (. Vi P4-. )f..i(x;,

f ,09 (x;,y; ,P;., )(х,,

f ,05 .. f«n(;

(x;,y;,P;., )fjiiCx;,

f .50 (x;,v; ,p. )f (x; ,

f ,05 (.P;.. ) (.

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный двоичный сумматор-вы-чиТАТЕль | 1979 |

|

SU824205A1 |

| Одноразрядный четверичный сумматор-вычитатель | 1984 |

|

SU1229756A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для вычитания десятичных чисел | 1975 |

|

SU607216A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Одноразрядный десятичный сумматор | 1975 |

|

SU690479A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018925C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств ЭВМ и спецпроцессоров. Цель изобретения - расширение функциональных возможностей за счет реализации дополнительных операций сложения и вычитания обратных кодон двоичных чисел. Одноразрядный сумматор-вычита- тель содерзкит семь элементов РАВНОЗНАЧНОСТЬ 1-7, входы 8 и 9 первого и второго операндов соответствующих разрядов,вход 10 переноса-заема, входы 11-13 настройки,выход 14 суммы, выход 15 переноса-заема. 1 ил., 1 табл. сл

| Лысинков Б.Г.Арифметические и логические основы цифровых автоматов | |||

| - Минск: Высшая школа, 1980, с | |||

| АППАРАТ ДЛЯ ОБОГАЩЕНИЯ РУД ПО МЕТОДУ ВСПЛЫВАНИЯ | 1915 |

|

SU279A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Сумматор-вычитатель | 1985 |

|

SU1251070A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-23—Публикация

1986-05-08—Подача