и ь г {( (Mine птноситгя к вычисли- 1с:|т,и(Й тел)1пке н преднагэначается дни нптльчорлПИЯ в арифметических VI трштстиях иычислительн1)1х машин, . ;тя111их приводах и других П1тиборах, ivie иптольчуется мно- 1 офачныр код,.

Цель изобретения - повышение бы- стродрйс т яия при работе в миог офаз- иых кодах.

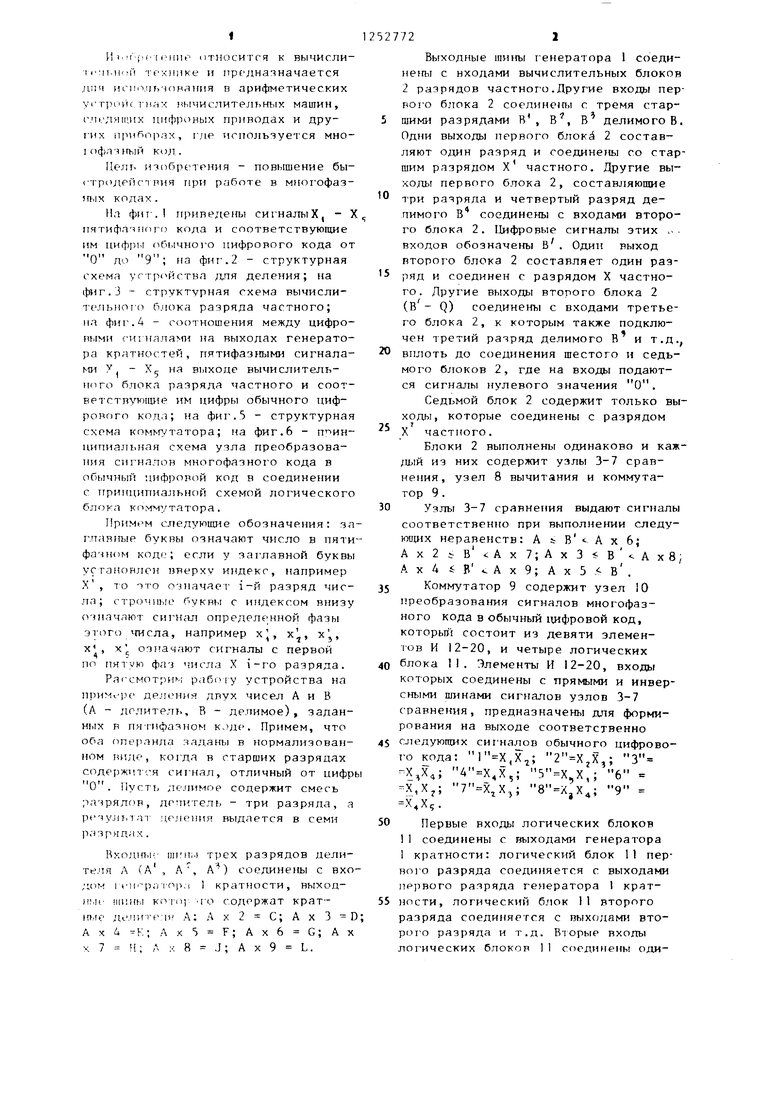

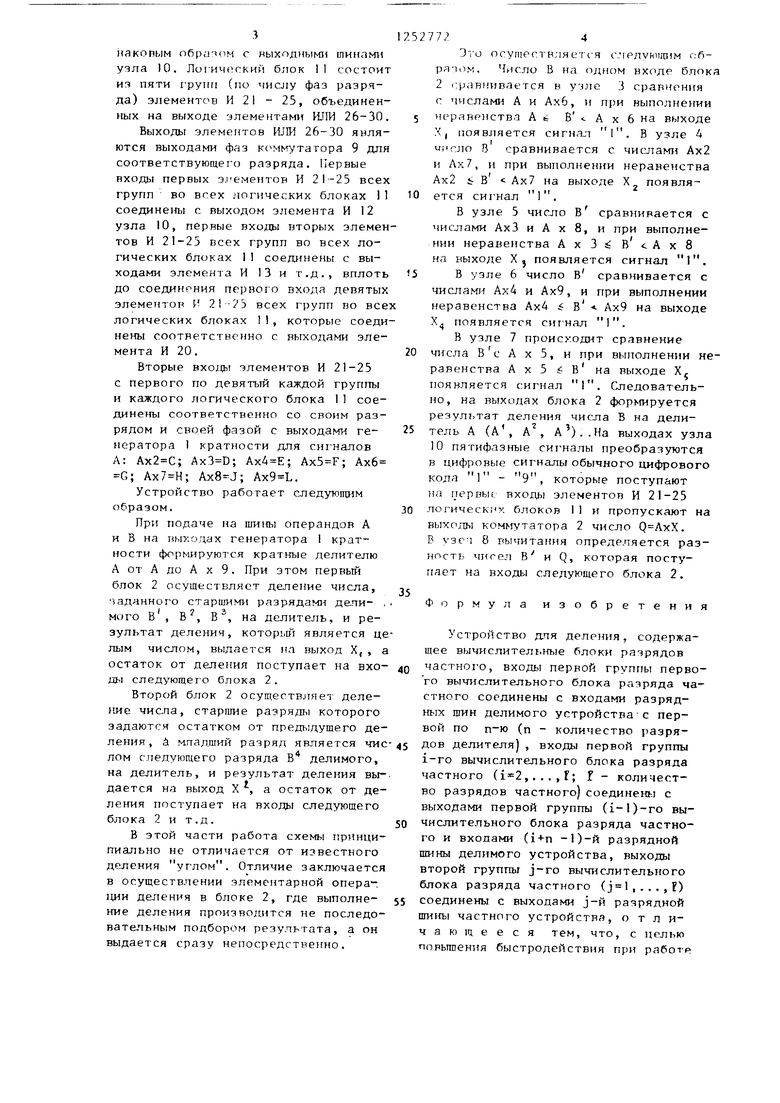

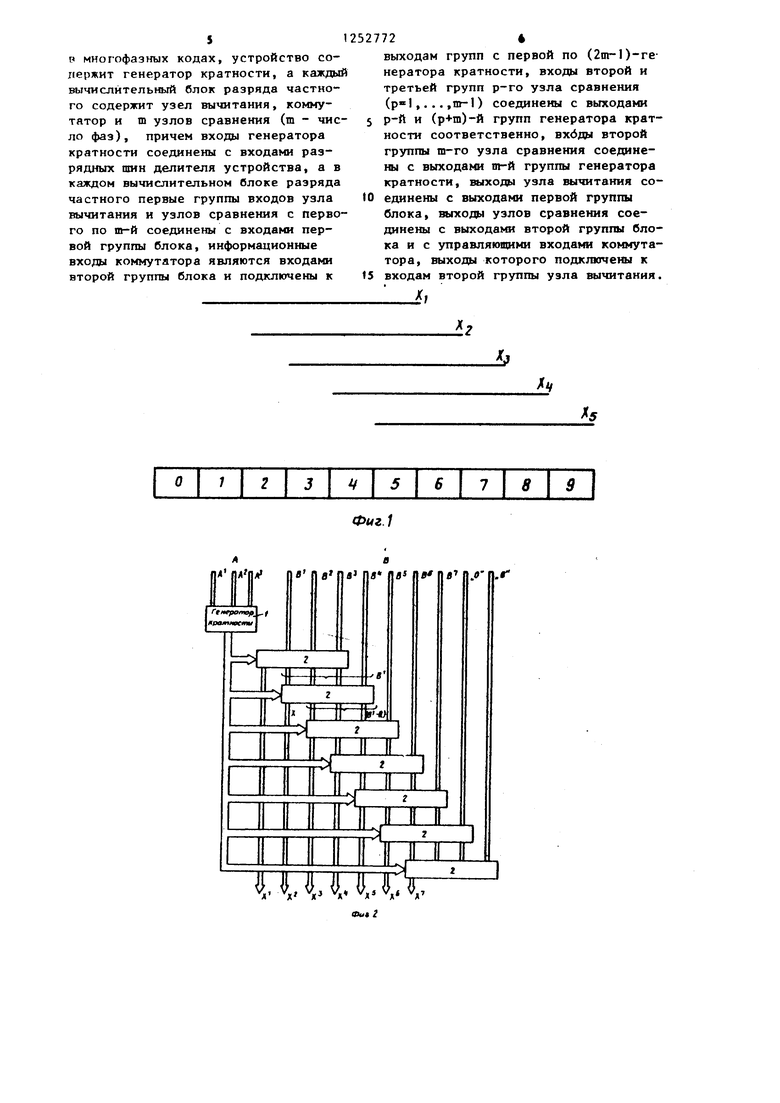

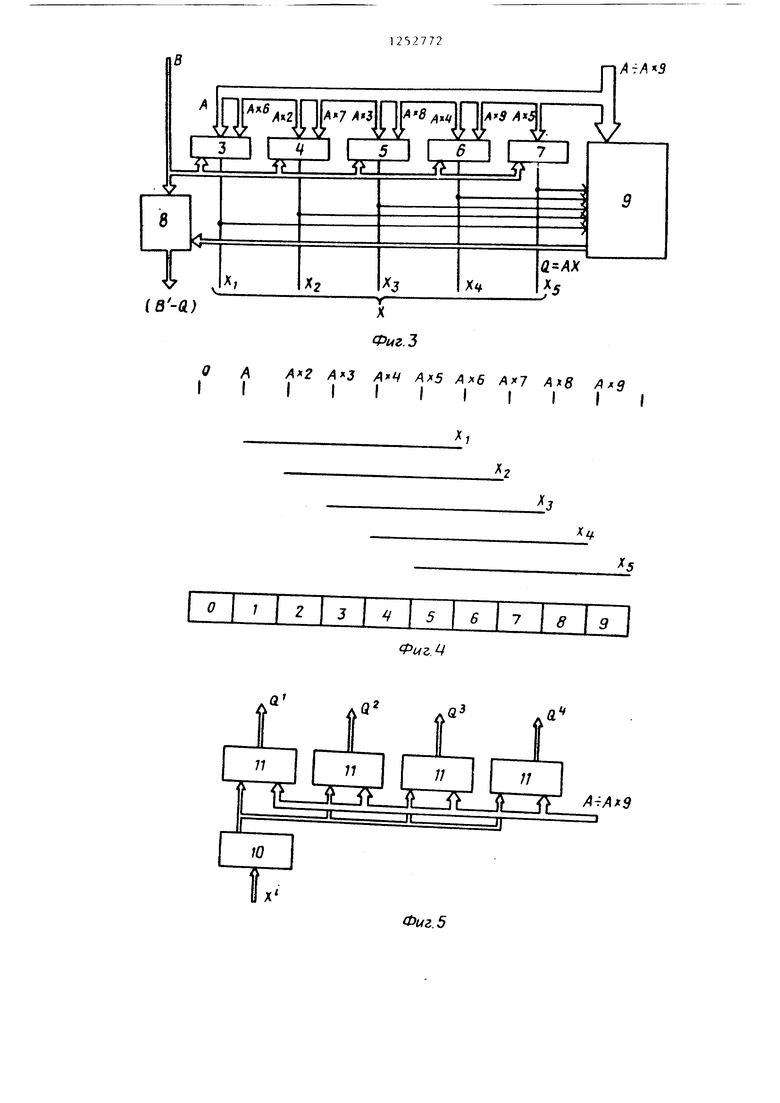

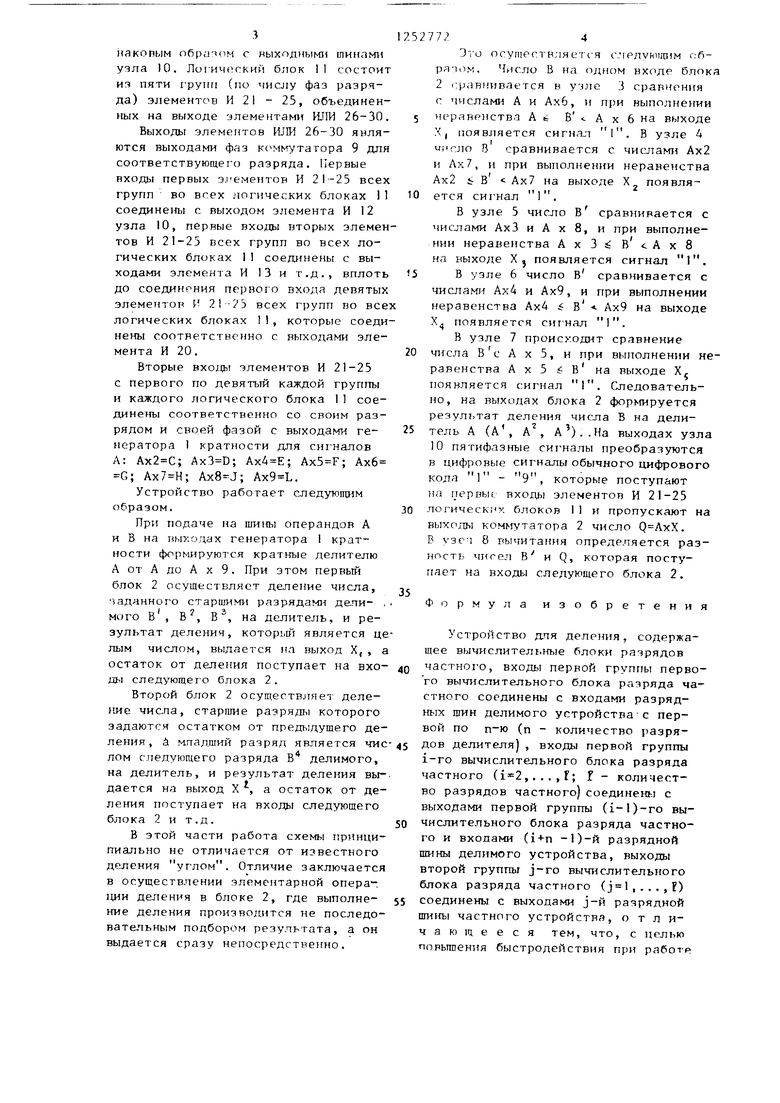

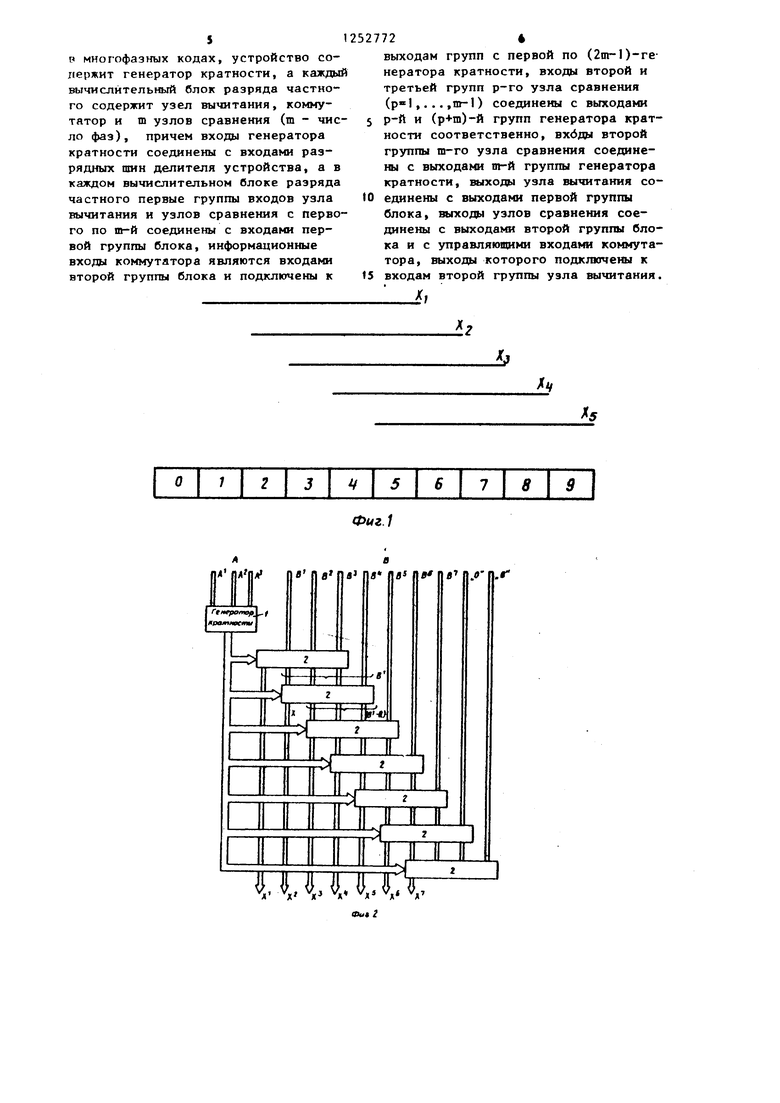

Нл фи1-.1 приведены сигналыХ, - Х пятифачног кода и соответствующие им пифры обычного цифрового кода от О до на фиг.2 - структурная схема устройства ;1/1я деления; на фиг.З - структурная схема вычисли- тель)1О1-о блока разряда частного; на фиг.4 - соотношения между цифровыми си1иала ш на выходах генератора кратностей, пятифазными сигнала- ьпл У. - Xj на выходе вычислительного блока разряда частного и соответствующие им цифры обычного цифрового кода; на фиг.З - структурная схема KON r/TOTopa; на фиг.6 - ципиальная схема узла преобразования сигналов многофазного кода в обычный цифровой код в соединении с принципиальной схемой логического блока к о т о р а.

Примем следующие обозначения: заглавные буквы означают число в пяти фачном кодс ; если у заглавной буквы установлен вверху И}щекс, например X , то ото означает i-и разряд числа; cTpo uiiiie буквы с индексом внизу (ги1ачлют сигНс цч определенной фазы этогочисла, например х ,, х , х ,, X , X . означают сигналы с первой по ПЯТУЮ фаз числа X i-ro разряда.

Рассмотриь рабогу устройства на приме,н дел1М1ия двух чисел А и В (А - делитель, В - делимое), заданных в пятифазном к-)де. Примем, что оба операнда заданы в нормализованном виде, когда в старших разрядах содержится сигнал, отличный от цифр О. Пусть делимое содержит смесь разрядов, дгттитель - три разряда, а резул1л;п целения выдается в семи р.чзрндих .

ВходШ 1г шг11;.1 трех разрядов делителя Л (А , А , А ) соединены с входом re ii p;v I ор.1 1 кратности, выход- и,е типы КОГО ч о содержат крат- Hi,ie Д1 ли ге:|1; А: А х 2 С; А х 3 D А X 4 -К; А X 3 F; А X 6 G; А X X 7 Я; А л 8 J; А X 9 L.

527722

Выходные шины генератора 1 соединены с входами вычислительных блоков 2 разрядов частного.Другие входы первого блока 2 соединеШ) с тремя стар5 шими разрядами В, в , В делимого В, Одни выходы первого блоке 2 составляют один разряд и соединены со старшим разрядом х частного. Другие выходы первого блока 2, составляющие

три разряда и четвертый разряд делимого В соединены с входами второго блока 2. Цифровые сигналы этих . . входов обозначены в . Один выход второго блока 2 составляет один раз 5 ряд и соединен с разрядом X частного. Другие выходы второго блока 2 (в - Q) соединены с входами третьего блока 2, к которым также подключен третий разряд делимого в и т.д.

вплоть до соединения шестого и седьмого блоков 2, где на входы подаются сигналы нулевого значения О.

Седьмой блок 2 содержит только выходы, которые соединены с разрядом X частного.

Блоки 2 выполнены одинаково и каж- ;шй из них содержит узлы 3-7 сравнения, узел 8 вычитания и коммутатор 9 .

30 Узлы 3-7 сравнения выдают сигналы соответственно при выполнении следу- юишх неравенств: А ь В - А х 6;

JJ

«:Ах7;АхЗ В Ах8; Ах4 В Ах9;Ах5ЛВ .

35 Коммутатор 9 содержит узел 10 преобразования сигналов многофазного кода в обычный цифровой код, которьш состоит из девяти элементов И 12-20, и четыре логических

40 блока II. Элементы И 12-20, входы которых соединены с прямыми и инверсными щинами сигналов узлов 3-7 сравнения, предназначены для формирования на выходе соответственно

45 следующих сигналов обычного цифрового кода: ,Х,,; ,; 3 -Х,Х,; ,Х,; X,; 6 --Х,Х,; ,Х,; 9

х,х,.

50 Первые входы логических блоков 11 соединены с выходами генератора 1 кратности: логический блок 11 первого разряда соединяется с выходами первого разряда генератора I крат55 ности, логический блок 11 второго разряда соединяется с выходами второго разряда и т.д. Вюрые входы логических блоков 11 соединены оди3

иакопым обра:(1м с выходным шинами узла 10. Ло1 ич(ский блок 11 состоит из пяти г рутгп (по числу фаз разряда) элементов И 21 - 25, объединенных на выходе элементами ИЛИ 26-30. Выходы элементов Ш1И 26-30 являются выходами фаз к(мм татора 9 для соответствующег о разряда. Первые входы первых э.г ементов И 21-25 всех групп во всех логических блоках 11 соедине1Л1 с выходом элемента И 12 узла 10, первые входы вторых элементов И 21-25 всех групп во всех логических блоках 11 соединены с выходами элемента И 13 и т.д., вплоть до соединения первого входа девятых элементов И всех групп во все логических блоках 11, которые соединены соответственно с вьгходами элемента И 20.

Вторые Bxo;jj3i элементов И 21-25 с первого по девятый каждой группы и каждого логического блока I1 соединены соответственно со своим разрядом и своей фазой с выходами генератора 1 кратности для сигналов А: Ах6 G; .

Устройство работает следующим образом.

При подаче на пшны операндов А и В на ныу.одах генератора 1 кратности формируются кратные делителю А от А до А X 9. При этом первый блок 2 осуществляет деление числа, наданного старшими разрядами д&пи- , мого в , В, В, на делитель, и результат деления, которой является целым числом, выдается на выход X, , а остаток от деления поступает на входы следующего блока 2.

Второй блок 2 осуществляет деление чиспа, старшие раэряд1 | которого задаются остатком от предыдущего деления, и мпадший разряд является числом следующего разряда В делимого, на делитель, и результат деления выдается на выход X , а остаток от деления поступает на входы следующего блока 2 и т.д.

В этой части работа схемы принципиально не отличается от известного деления углом. Отличие заключается в осуществлении элементарной опера деления в блоке 2, где выполнение деления производится не последовательным подбором результата, а он выдается сразу непосредственно.

527724

Это осуп1еств;1яетс Я с.чрдук1щим ( ;б- ря юм. Число В на одном входе блока 2 сравнивается в узле 3 сравнения с числами А и Ахб, и при выполнении 5 неравенства А ь В «- А х 6 на выходе X, появляется сигнал 1. В узле 4 число в сравнивается с числами Ах2 и Ах7, и при выполнении неравенства Ах2 В Ах7 на выходе Х появля- 0 ется сигнал 1.

В узле 5 число В сравнивается с числами АхЗ и А х 8, и при выполнении неравенства сАхЗ на выходе Xj появляется сигнал 1. 5В узле 6 число В сравнивается с

числами Ах4 и Ах9, и при выполнении неравенства Ax-i В Ах9 иа выходе появляется сиг на.п 1.

В узле 7 происходит сравнение

0 числа В с А х 5, и при выполнении неравенства А X 5 в на выходе X, появляется сигнал I. Следовательно, на выходах блока 2 формируется результат деления числа В на дели5 тель А (А, А , А )..На выходах узла 10 пятифазные сигналы преобразуются в цифровые сигналы обычного цифрового кода 1 - 9, которые поступают на первые входы элементов И 21-25

0 логических блоков I1 и пропускают на выходы ком гутатора 2 число . В узеч 8 вычитания определяется разность чисел в и Q, которая поступает на входы следующего блока 2.

35

Формула изобретения

Устройство дня деления, содержащее вычислительные блоки разрядов

частного, входы первой группы перво- го вычислительного блока разряда частного соединены с входами разрядных шин делимого устройства с первой по п-ю (п - количество разряДов делителя) , входь первой группы i-ro вычислительного блока разряда частного (,..,,Г; Г - количество разрядов частного) соединены с выходами первой группы (i-l)-ro вычислительного блока разряда частного и входами (i-t-n -1)-й разрядной пшны делимого устройства, выходы второй группы j-ro вычислительного блока разряда частного ()

соединены с выхода чи j-й разрядной шины частного устройства, отличающееся тем, что, с целью ппрьппения быстродействия при работе

р многофазных кодах, устройство содержит генератор кратности, а каждый вычислительный блок разряда частного содержит узел вычитания, коммутатор и m узлов сравнения (т - число фаз), причем входы генератора кратности соединены с входами разрядных шин делителя устройства, а в каждом вычислительном блоке разряда частного первые группы входов узла вычитания и узлов сравнения с первого по т-й соединены с входами первой группы блока, информационные входа коммутатора являются входами второй группы блока и подключены к

iiiii5..V

52772«

выходам групп с первой по (2т-1)-ге- нератора кратности, входы второй и третьей групп р-го узла сравнения (,... ,пг-1) соединены с выходами

5 р-й и (р+т)-й групп генератора кратности соответственно, вхбды второй группы т-го узла сравнения соединены с выходами т-й группы генератора кратности, выходы узла вычитания со10 единены с выходами первой группы блока, выходы узлов сравнения соединены с выходами второй группы блока и с управляющими входами коммутатора, выходы которого подключены к

t5 входам второй группы узла вычитания,

6l

В

JI

гу Lf Ul N I Чп ч i v I чг

Хг

ffl-fi)

. 5

X Ф«г.З

ff А А Ч Лл5 Лх/ Алд I I I I I I I I f I

J

х

. 5

Ф1АгМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1291974A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Конвейерное арифметическое устройство | 1984 |

|

SU1203511A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для последовательного деления | 1986 |

|

SU1304017A1 |

Изобретение относится к вычислительной технике и предназначается для использования в арифметических узлах вычислительных машин и следящих цифровых приводах. Цель изобретения - псвьппение быстродействия при работе в многофазных кодах. Цель достигается тем, что в устройстве, содержащем вычислительные блоки разрядов частного, разрядные шины делимого к:тройства с первой по п-ю (п - количество разрядов делителя), введен генератор кратности, а каждый вычислительный блок содержит узел вычитания, коммутатор и m узлов сравнения (га - число фаз). 6 ил. с Ф (/)

f

G ..а

t

77

.Q

//

/7

1C-3E3ElJ i: ELir Ty

}Q

и

/4т/4ж5

Фиг.б

Редактор В.Петраш

Согтавитель В.Версзкин

Техррд В.адарКорректор Е. Сирохман

Тираж 671 Подписное

Заказ 4621/ 9

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рпушская наб., д.А/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

| Прангишвили И.В | |||

| и др | |||

| Микроэлектроника и однородные структуры для построения логических и вычислительных устройств | |||

| - М.: Наука, 1967, с.181-184 | |||

| Беркс и др | |||

| Предварительное рассмотрение логической конструкции электронного вычислительного устройства | |||

| - Кибернетический сборник | |||

| М | |||

| Прибор для заливки свинцом стыковых рельсовых зазоров | 1925 |

|

SU1964A1 |

Авторы

Даты

1986-08-23—Публикация

1984-04-26—Подача