ка, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ К -го вычислительного блока соединен с информационным входом младшего разряда регистра частного (К+1)-го вычислительного блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последнего вычислительного блока является младшим разрядом выхода частного устройства, вход задания режима которого соединен с входом установки в О триггера, входами установки в О разрядов, кроме третьего, регистра делителя, первого вычислительного |блокаи входом установки в 1 (К + 2)- го разряда регистра делителя К-го вычислительного блока, выход регистр делителя последнего вычислительного блока является выходом значения

Изобретение относится к вычислительной технике и предназначено для использования в специализ ированных цифровых вычислительных машинах высокой производительности.

Цель изобретения - повьшение быстродействия.

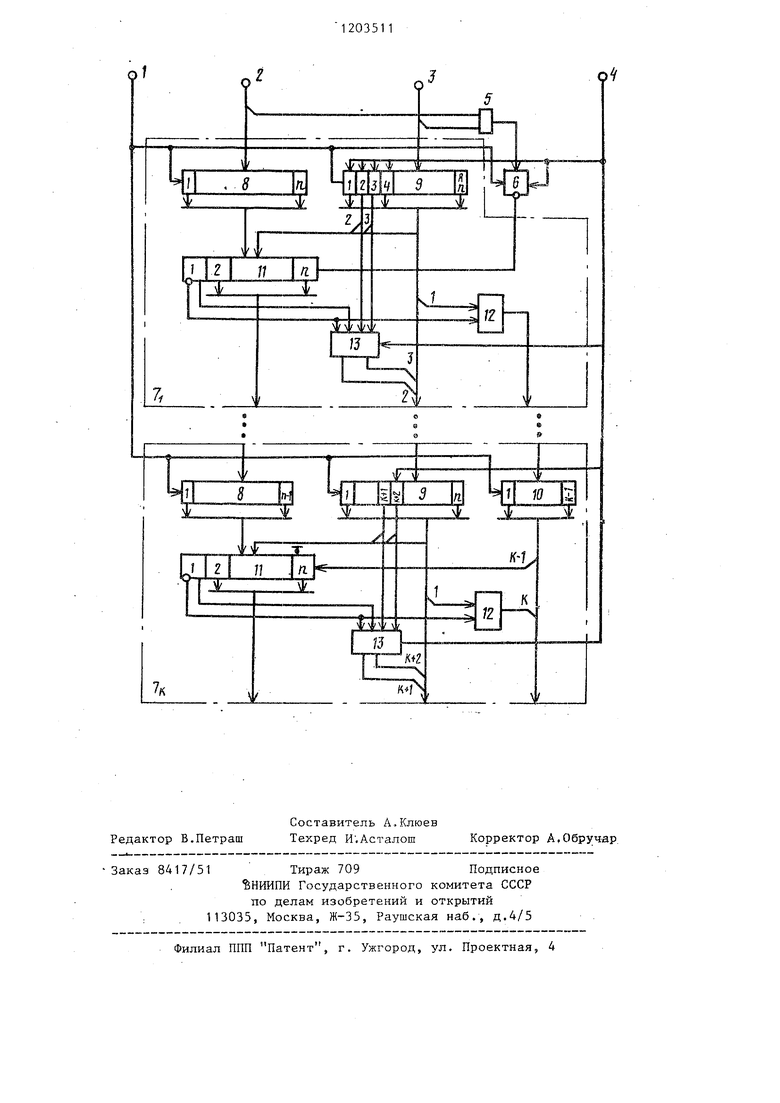

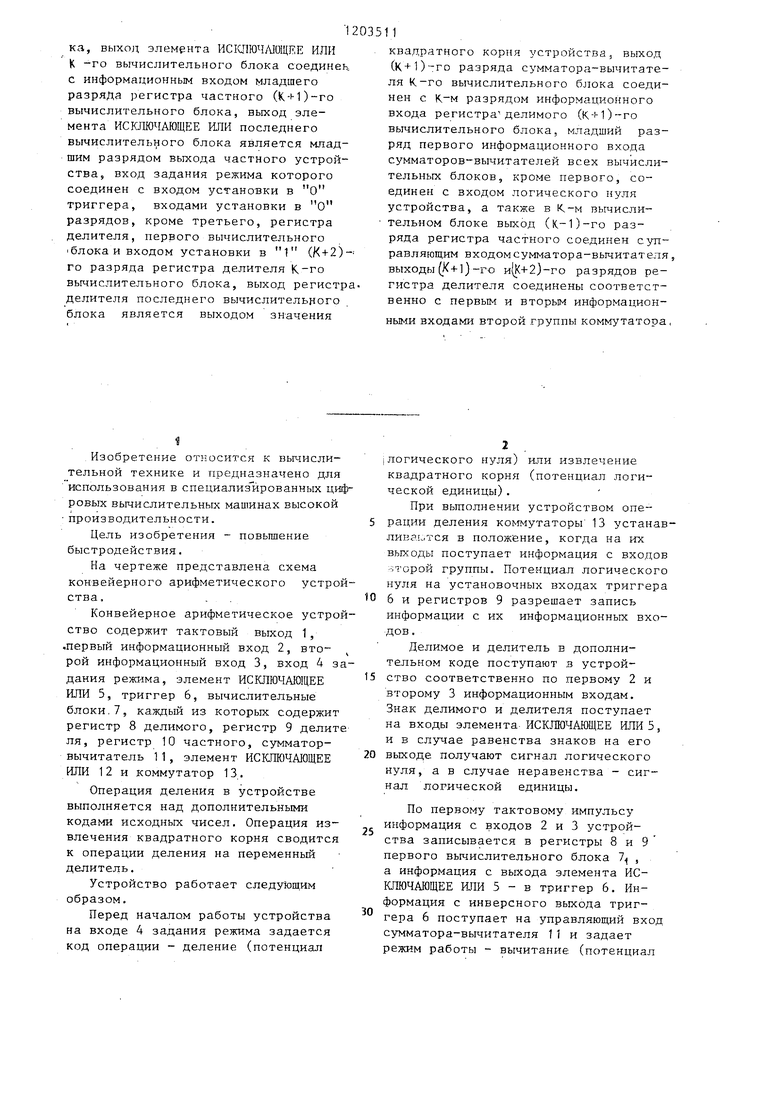

На чертеже представлена схема конвейерного арифметического устроства.

Конвейерное арифметическое устроство содержит тактовый выход 1, .первый информационный вход 2, второй информационный вход 3, вход 4 здания режима, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, триггер 6, вычислительные блоки,, каждый из которых содержит регистр 8 делимого, регистр 9 делит ля, регистр 10 частного, сумматор- вычитатель 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12 и коммутатор 13..

Операция деления в устройстве выполняется над дополнительными кодами исходных чисел. Операция извлечения квадратного корня сводится к операции деления на переменный делитель.

Устройство работает следующим образом.

Перед началом работы устройства на входе 4 задания режима задается код операции деление (потенциал

квадратного корня устройства, выход (К+1)-го разряда сумматора-вычитате- ля К-го вычислительного блока соединен с K-M разрядом информационного входа регистра делимого (K-f-l)ro вычислительного блока, младший разряд первого информационного входа сумматоров-вычитателей всех вычислительных блоков, кроме первого, соединен с входом логического нуля устройства, а также в К-м вычислительном блоке выход (К,-1)-го разряда регистра частного соединен суп- равляЕощим входом сумматора-вычитат еля выходы (K+l)-го и{К+2)-го разрядов регистра делителя соединены соответственно с первым и вторым информационными входами второй группы коммутатора

Логического нуля) или извлечение квадратного корня (потенциал логической единицы),

При вьгаолнении устройством операции деления коммутаторы 13 устанав- линэлится в положение, когда на их выходь поступает информация с входов чторой группы. Потенциал логического нуля на установочных входах триггера

6 и регистров 9 разрешает запись

информации с их информационных входов .

Делимое и делитель в дополнительном коде поступают в устройство соответственно по первому 2 и второму 3 информационным входам. Знак делимого и делителя поступает на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, и в случае равенства знаков на его

выходе получают сигнал логического нуля, а в случае неравенства - сигнал логической единицЕ 1.

По первому тактовому импуотьсу информация с входов 2 и 3 устройства записывается в регистры 8 и 9 первого вычислительного блока 7 , а информация с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 - в триггер 6, Информация с инверсного выхода триггера 6 поступает на управляющий вход сумматора-вычитателя 11 и задает режим работы - вычитание (потенциал

логической единицы) или суммирование (потенциал логического нуля). Знак результата операции с инверсного выхода первого разряда сумма- тора-вычитателя 11 поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 на первый вход которого поступает знак делителя с выхода первого регистра 9, и в зависимости от равенства или неравенства информации на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 1 2 получают логический нуль или логическую единицу. Информация на выходе данного элемента является первым разрядом частного, а также опреде- ляет код операции сумматора-вычита- теля 11 второго вычислительного блока 1 ч.

По второму тактовому импульсу в регистры 8 и 9 первого вычислпггель- ного блока 7 записываются новые элементы обрабатываемого массива, а в триггер 6 - информация с вьгхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Одновременно в регистры 8 - 10 второго РЛЛ числительного блока Уг записыв;;ется информация с выходов первого вычислительного блока 7 .Во втором вычислительном блоке 1 выполняется вторая итерация операции деления, т.е. вычитание делителя с первым частным остатком, сдвинутым влево на один разряд.

Знак результата операции с инверсного вьгхода первого разряда .с мматора-вычитателя 11 поступает н второй вход элемента ИСКЛЮЧАКЩЕЕ ИЛИ 12, на первый вход которого.поступает знак делителя, и в зависимости от равенства или неравенства входной информации на выходе данног элемента получают О или 1.

По следующим тактовым импульсам устройство работает аналогично, т.е в каждом вычислительном блоке 7 выполняется одна итерация алгоритма деления.

Старшие разряды результата деления получаются на выходе регистра 1 а младший - на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 вычислительного блока 7| после прохождения данных через все вычислительные блоки.

При выполнении операции извлечения квадратного корня на вход 4 задания режима подается потенциал логической единицы, который устанав- 6 в о,

ливает триггер

а коммутато10

5

20

25

ры 13 - в положение,, когда tia их пыход поступает информация с входов первой группы.

Потенциал логической единицы на 5 установочных входах регистра 9 пер- вого вычислительного блока 7 устанавливает его третий разряд в 1, а все остальные в О. В других вычислительных блоках 1 в данном режиме выход (К+2)-го разряда регистра 9 устанавливается в единицу.

По первому тактовому импульсу первое подкоренное число с первого информационного входа 2 записывается в регистр 8 первого вычислительного блока 1. . С регистра 8 число поступает на первые входы сумматора- вычитателя 11, на вторые входы которого поступает информация с регистра 9. На выходе сумматора-вычитате- ля 11 первого вычислительного блока получают результат вычитания, кото-, рый определяет старший разряд результата Z (результат вычитания больше или равен нулю - Z( 1, меньше нуля - Z 0) и код операции для сумматора-вьгчитателя 11 второго вычислительного блока 77 (результат вычитания больше и.пи равен нулю - вычитание, меньше нуля с ум- ьшрование).

По второму тактовому импульсу в регистр 8 первого вычислительного бл-ока 7/( записывается новое подкоренное число, от которого вычитается число, записанное в регистре 9. Одновременно в регистры 8-10 второго вычислительного блока 7.i записывается информация с выходов перво- го вычислительного блока 7.,. . Во втором вычислительном блоке 1 происходит суммирование или вычитание числа, записанного в регистре 9 от первого частотного остатка, сдвинутого влево на один разряд. Б зависимости от результата операций получается следующий разряд результа- та. По следующим тактовым импульсам устройство работает аналогично, т. е. в каждом вычислительном блоке 7 вьшолняется одна итерация алгоритма извлечения квадратного корня. Результат извлечения квадратного корня получают на выходе регистра 9 вычислительного блока 7н, после прохождения данных через .все вычислительные блоки.

30

35

40

45

50

55

Редактор В.Петраш

Составитель А.Клюев Техред И .Асталош

8417/51

Тираж 709Подписное

НИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Корректор А,0бручар

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Арифметическое устройство | 1985 |

|

SU1290299A1 |

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1984 |

|

SU1242935A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для деления десятичных чисел | 1990 |

|

SU1774328A1 |

| Устройство для деления десятичных чисел | 1989 |

|

SU1688239A1 |

| Устройство для деления | 1980 |

|

SU898425A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU942005A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-07—Публикация

1984-07-16—Подача