.Изобретение относится к вычислительной технике и предназначается для использования в арифметических устройствах вычислительных машин, следящих цифровых приводах.

Цель изобретения - расширение области применения за счет возможности деления чисел в произвольной позиционной системе счисления.

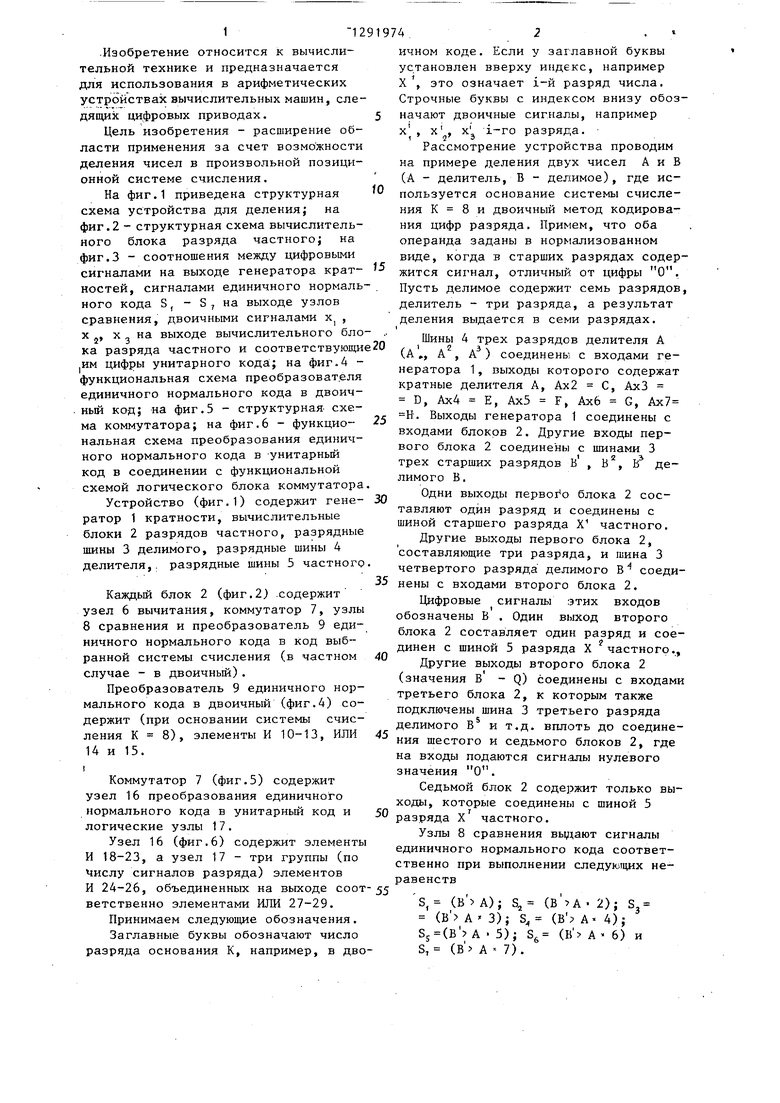

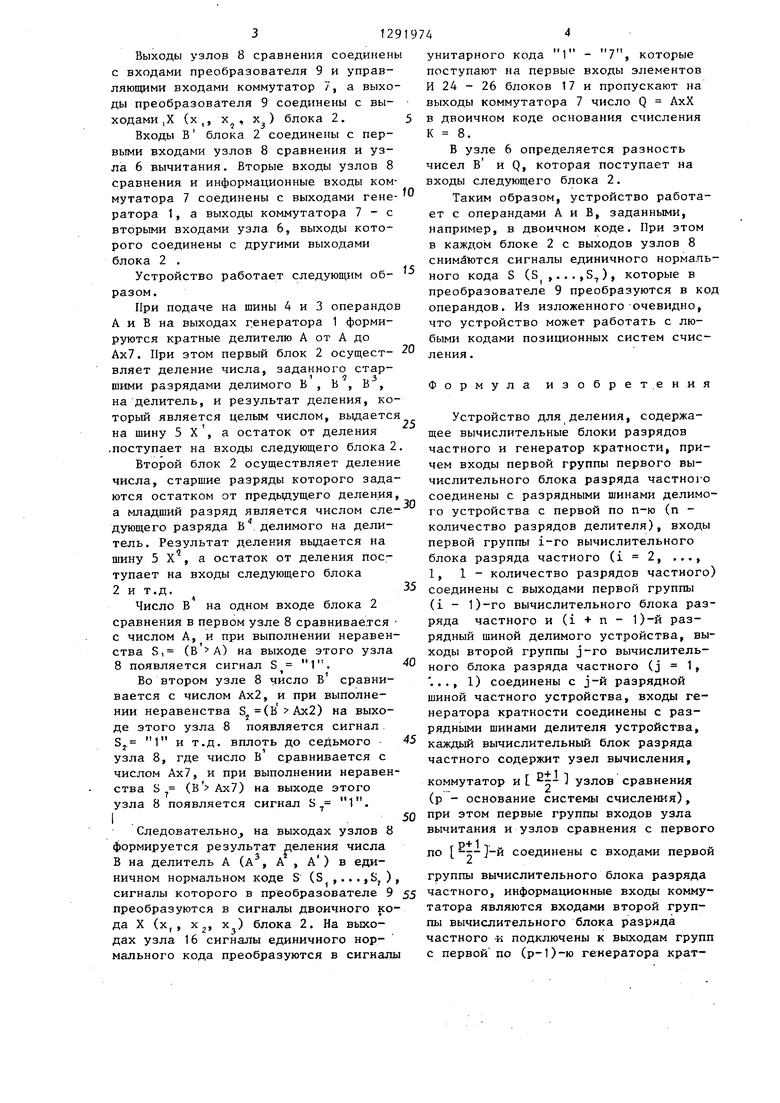

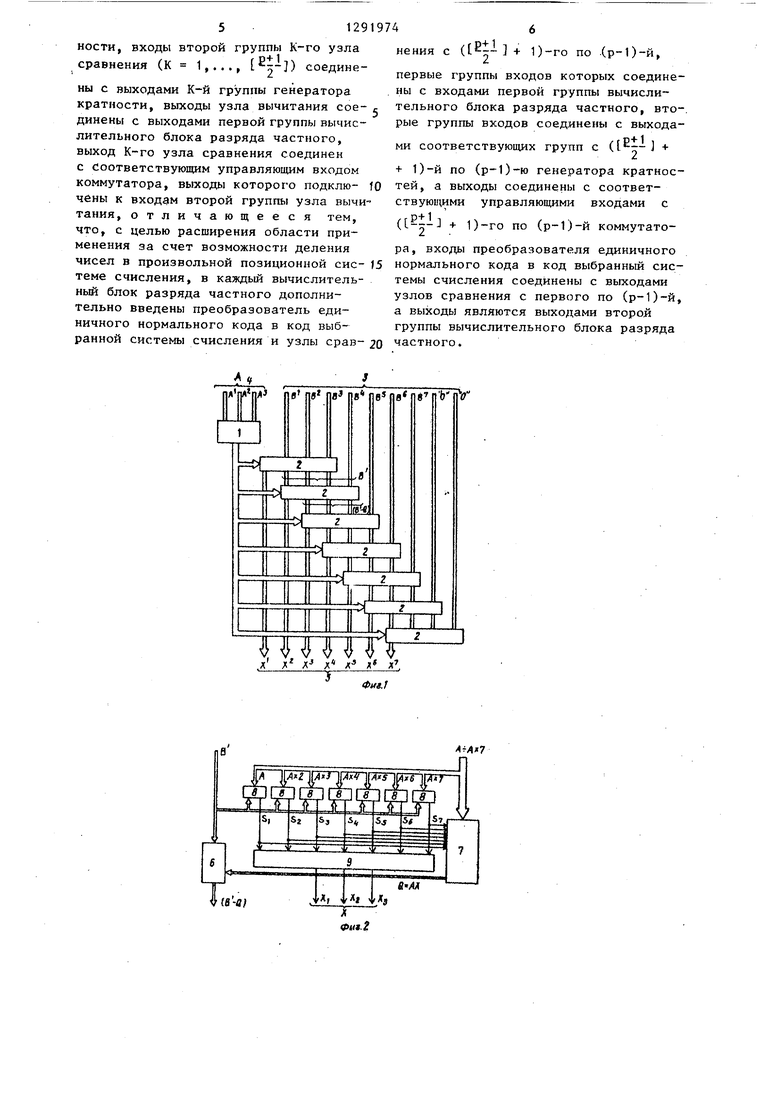

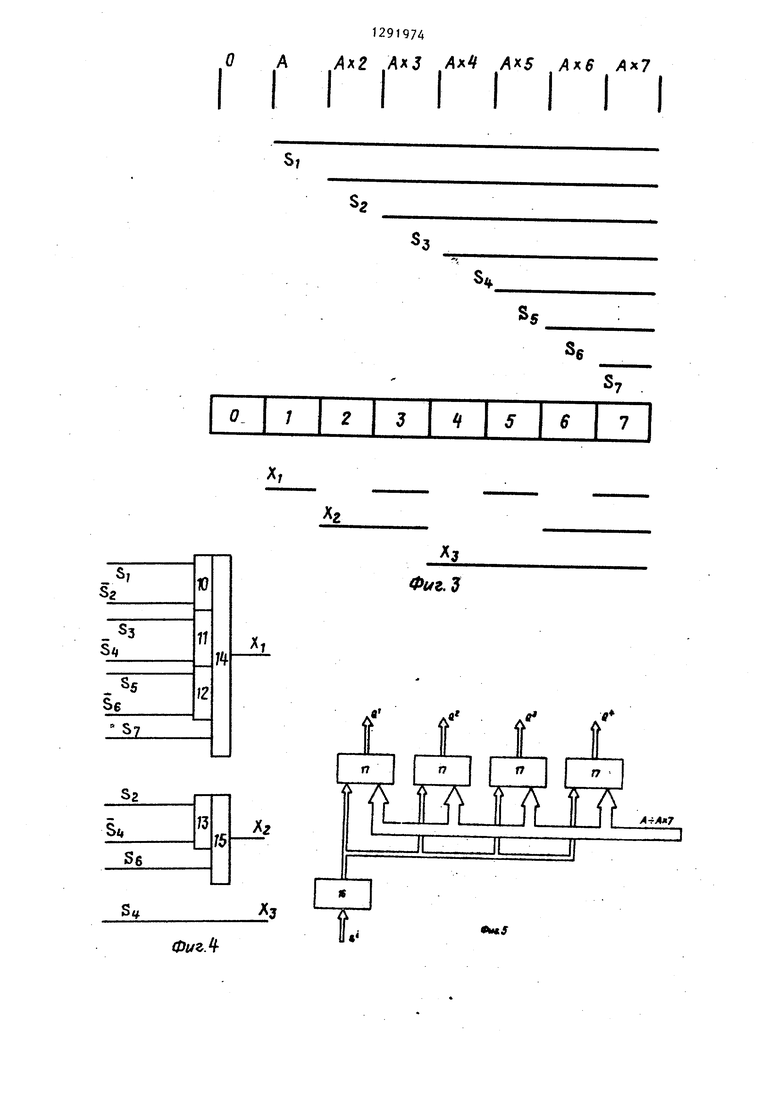

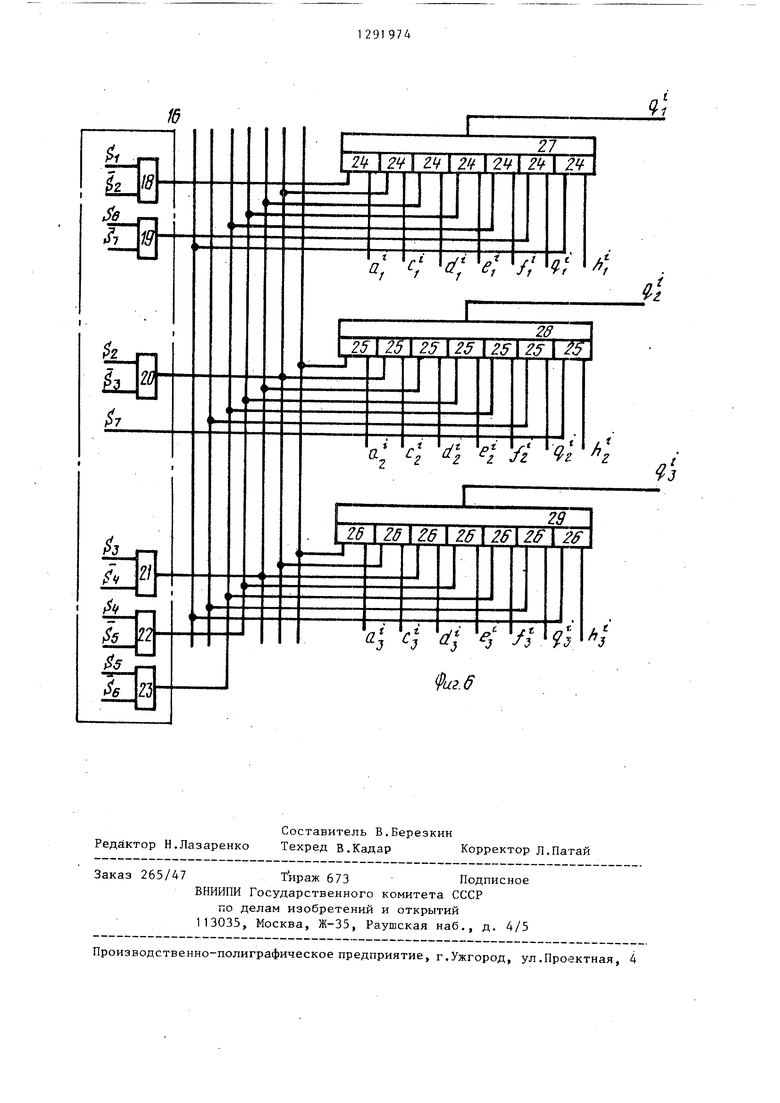

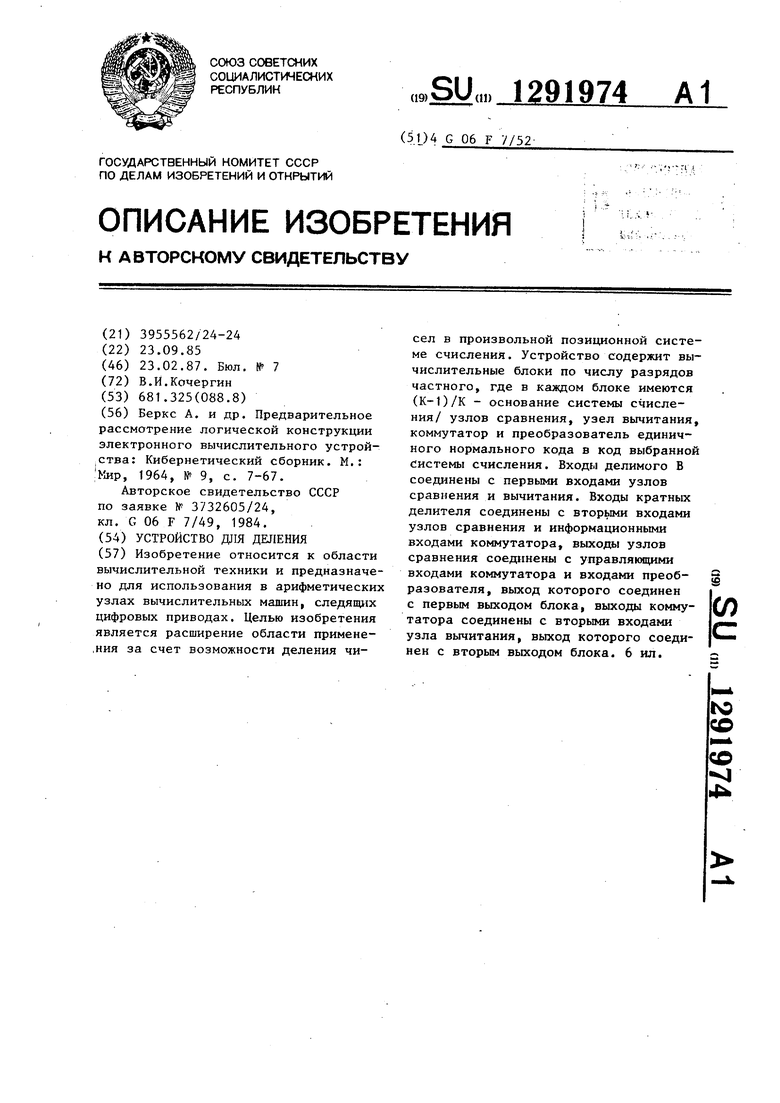

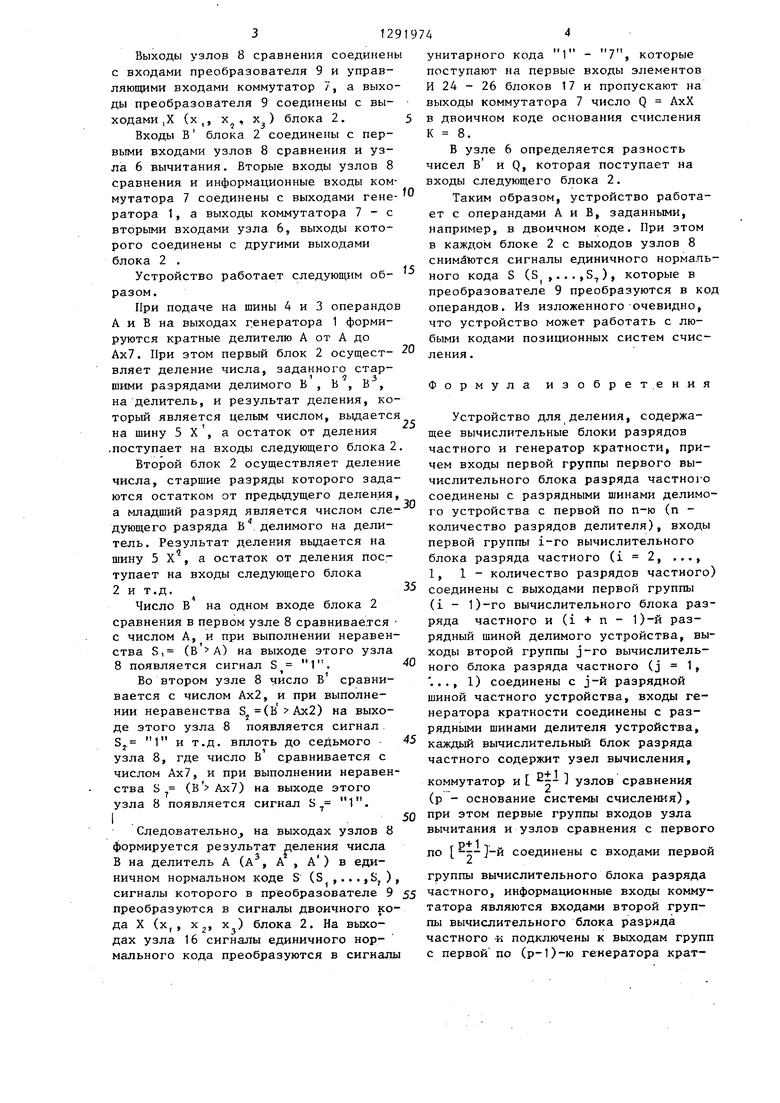

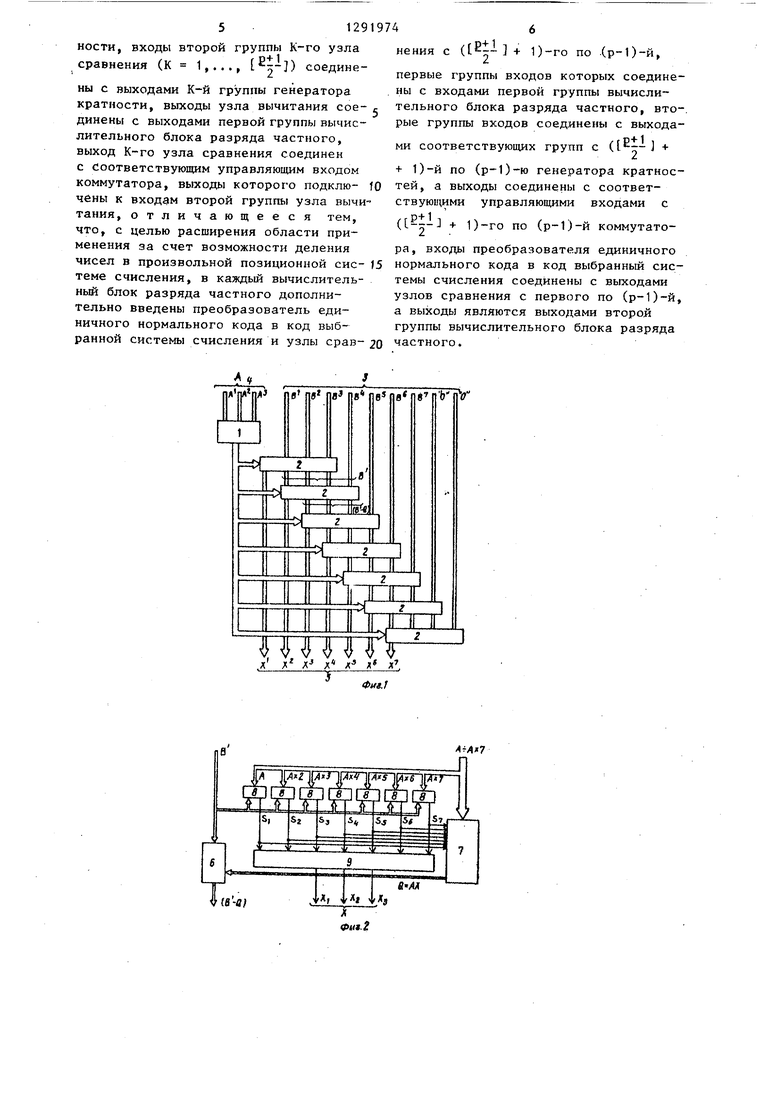

На фиг.1 приведена структурная схема устройства для деления; на фиг.2 - структурная схема вычислительного блока разряда частного; на фиг.З - соотношения между цифровыми сигналами на выходе генератора крат- костей, сигналами единичного нормаль ного кода S, - S, на выходе узлов сравнения, двоичными сигналами х , X , X - на выходе вычислительного бло ка разряда частного и соответствующи им цифры унитарного кода;; на фиг.4 - функциональная схема преобразоват.еля единичного нормального кода в двоичный код; на фиг.З - структурная- схема коммутатора; на фиг.6 - функциональная схема преобразования единичного нормального кода в унитарный код в соединении с функциональной схемой логического блока коммутатора

Устройство (фиг.1) содержит генератор 1 кратности, вычислительные блоки 2 разрядов частного, разрядные шины 3 делимого, разрядные шины 4 делителя,, разрядные шины 5 частного

Каждый блок 2 (фиг.2) .содержит узел 6 вычитания, коммутатор 7, узлы 8 сравнения и преобразователь 9 единичного нормального кода в код выбранной системы счисления (в частном случае - в двоичный).

Преобразователь 9 единичного нормального кода в двоичный (фиг.4) содержит (при основании системы счисления К 8), элементы И 10-13, ИЛИ 14 и 15.

Коммутатор 7 (фиг.З) содержит узел 16 преобразования единичного нормального кода в унитарный код и логические узлы 17.

Узел 16 (фиг.6) содержит элементы И 18-23, а узел 17 - три группы (по Числу сигналов разряда) элементов И 24-26, объединенных на выходе соответственно элементами ИЛИ 27-29.

Принимаем следующие обозначения.

Заглавные буквы обозначают число разряда основания К, например, в дво

е12919742.

ичном коде. Если у заглавной буквы установлен вверху индекс, например X , это означает i-й разряд числа. Строчные буквы с индексом внизу обозначают двоичные сигналы, например

O

5

. .. О

5

0

5

0

5

5

трех разрядов делителя А А ) соединены с входами геX , X , Xj 1-го разряда.

Рассмотрение устройства проводим на примере деления двух чисел А и В (А - делитель, В - делимое), где используется основание системы счисления К 8 и двоичный метод кодирования цифр разряда. Примем, что оба операнда заданы в нормализованном виде, когда в старших разрядах содержится сигнал, отличный от цифры О. Пусть делимое содержит семь разрядов, делитель - три разряда, а результат деления выдается в семи разрядах.

Шины 4 (А-., А

нератора 1, выходы которого содержат кратные делителя А, Ах2 С, АхЗ D, Ах4 Е, АхЗ F, Ахб G, Ах7 Н:. Выходы генератора 1 соединены с входами блоков 2. Другие входы первого блока 2 соединены с шинами 3 трех старших разрядов в , в . В делимого В.

Одни выходы первох о блока 2 составляют один разряд и соединены с шиной старшего разряда X частного.

Другие выходы первого блока 2, составляющие три разряда, и шина 3 четвертого разряда делимого В соединены с входами второго блока 2.

Цифровые сигналы этих входов обозначены В . Один выход второго блока 2 составляет один разряд и соединен с шиной 3 разряда X частного..

Другие выходы второго блока 2 (значения в - Q) соединены с входами третьего блока 2, к которым также подключены шина 3 третьего разряда делимого В ния шестого

на входы подаются сигн.алы нулевого значения О.

Седьмой блок 2 содержит только выходы, которые соединены с шиной 3 разряда х частного.

Узлы 8 сравнения вьщают сигналы единичного нормального кода соответственно при выполнении следующих неравенств

S, (В А); S (. 2); S (В А 3); S, (В А« 4); 85(В А . 3); S (В А 6) и S, (В А 7).

и т.д. вплоть до соедине- и седьмого блоков 2, где

312

Выходы узлов 8 сравнения соединен с входами преобразователя 9 и управляющими входами коммутатор 7, а выходы преобразователя 9 соединены с выходами ,Х (х,, х, X ) блока 2.

Входы В блока 2 соединены с первыми входами узлов 8 сравнения и узла 6 вычитания. Вторые входы узлов 8 сравнения и информационные входы коммутатора 7 соединены с выходами гене ратора 1, а выходы коммутатора 1-е вторыми входами узла 6, выходы которого соединены с другими выходами блока 2 .

Устройство работает следующим образом.

При подаче на шины 4 и 3 операндо А и В на выходах генератора 1 формируются кратные делителю А от А до

Ах7. При этом первый блок 2 осущест- вляет деление числа, заданного стар З 3

шими разрядами делимого В , В , В , на делитель, и результат деления, который является целым числом, выдаетс на шину 5 х , а остаток от деления .поступает на входы следующего блока 2

Второй блок 2 осуществляет делени числа, старшие разряды которого задаются остатком от предыдущего деления а младший разряд является числом следующего разряда В . делимого на делитель. Результат деления выдается на шину 5 х , а остаток от деления поступает на входы следующего блока 2 и т.д.

Число В на одном входе блока 2 сравнения в первом узле 8 сравнивается с числом А, и при выполнении неравенства S, () на выходе этого узла 8 появляется сигнал S 1.

Во втором узле 8 число В сравнивается с числом Ах2, и при выполнении неравенства Sj() на выходе этого узла 8 появляется сигнал . Sj, 1 и т.д. вплоть до седьмого узла 8, где число В сравнивается с числом Ах7, и при выполнении неравенства S (в Ах7) на выходе этого узла 8 появляется сигнал S 1.

Следовательно, на выходах узлов 8 формируется результат деления числа В на делитель А (А, А , А ) в единичном нормальном коде S (S ,...,8) сигналы которого в преобразователе 9 преобразуются в сигналы двоичного кода X (х,, х, X ) блока 2. На выходах узла 16 сигналы единичного нормального кода преобразуются в сигналы

унитарного кода 1 - 7, которые поступают на первые входы элементов И 24 - 26 блоков 17 и пропускают на выходы коммутатора 7 число Q АхХ в двоичном коде основания счисления К 8.

В узле 6 определяется разность чисел в и Q, которая поступает на входы следующего блока 2.

Таким образом, устройство работает с операндами А и В, заданными, например, в двоичном коде. При этом в каждом блоке 2 с выходов узлов 8 снимаются сигналы единичного нормального кода S (S,...,S), которые в преобразователе 9 преобразуются в код операндов. Из изложенного очевидно, что устройство может работать с любыми кодами позиционных систем счис5

5

0

5

0

5

ления .

Формула изобрет.ения

Устройство для деления, содержащее вычислительные блоки разрядов частного и генератор кратности, причем входы первой группы первого вычислительного блока разряда частного соединены с разрядными шинами делимого устройства с первой по п-ю (п - количество разрядов делителя), входы первой группы i-ro вычислительного блока разряда частного (, ..., 1, 1 - количество разрядов частного) соединены с выходами первой группы (i - 1)-го вычислительного блока разряда частного и (i п - 1)-й разрядный шиной делимого устройства, выходы второй группы j-ro вычислительного блока разряда частного (j 1, .. . , 1) соединены с j-й разрядной шиной частного устройства, входы генератора кратности соединены с разрядными шинами делителя устройства, каждый вычислительный блок разряда частного содержит узел вычисления,

коммутатор и -- 1 узлов сравнения (р - основание системы счисления), при этом первые группы входов узла вычитания и узлов сравнения с первого

г р-И т - по ---J-и соединены с входами первой

группы вычислительного блока разряда частного, информационные входы коммутатора являются входами второй группы вычислительного блока разряда частного -и подключены к выходам групп с первой по (р-1)-ю генератора кратности, входы второй группы К-го узла сравнения (К 1,..., соединены с выходами К-й группы генератора кратности, выходы узла вычитания соединены с выходами первой группы вычислительного блока разряда частного, выход К-го узла сравнения соединен с соответствующим управляющим входом коммутатора, выходы которого подключены к входам второй группы узла вычитания, отличающееся тем, что, с целью расширения области применения за счет возможности деления чисел в произвольной позиционной системе счисления, в каждый вычислительный блок разряда частного дополнительно введены преобразователь единичного нормального кода в код выбранной системы счисления и узлы сравТТТЛГПг

л л л л л1 д д.

Фиг.}

нения с ( 1)-го по .(р-1)-й,

первые группы входов которых соединены с входами первой группы вычислительного блока разряда частного, вто-. рые группы входов соединены с выходами соответствующих групп с (I г

+ 1)-й по (р-1)-ю генератора кратнос- тей, а выходы соединены с соответствующими управляюпщми входами с

(P±Ij + 1)-го по (р-1)-й коммутатора, входы преобразователя единичного

нормального кода в код выбранньш системы счисления соединены с выходами узлов сравнения с первого по (р-1)-й, а выходы являются выходами второй группы вычислительного блока разряда

частного.

Фиг.}

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1984 |

|

SU1252772A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для деления чисел на константу типа 2 @ + 1 | 1990 |

|

SU1791813A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Устройство для деления чисел в системе остаточных классов | 1985 |

|

SU1287152A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для деления | 1983 |

|

SU1151955A1 |

| Устройство для деления | 1980 |

|

SU928344A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

Изобретение относится к области вычислительной техники и предназначено для использования в арифметических узлах вычислительных машин, следящих цифровых приводах. Целью изобретения является расширение области примене- ,ния за счет возможности деления чисел в произвольной позиционной системе счисления. Устройство содержит вычислительные блоки по числу разрядов частного, где в каждом блоке имеются (К-1)/К - основание системы счисления/ узлов сравнения, узел вычитания, коммутатор и преобразователь единичного нормального кода в код выбранной системы счисления. Входы делимого В соединены с первыми входами узлов сравнения и вычитания. Входы кратных делителя соединены с вторыми входами узлов сравнения и информационньми входами коммутатора, выходы узлов сравнения соединены с управляющими входами коммутатора и входами преобразователя, выход которого соединен с первым выходом блока, выходы коммутатора соединены с вторыми входами узла вычитания, выход которого соединен с вторым выходом блока. 6 ил. i сл to со со ч 4ib

1291974

О А ,Ах2 MS .Ах A)iS .yixff qx7

Ю

ft

JZ

J

XT

s

Sz

Si.

/3

Г5

Лг

Se

. J

л

s

fLJGUDUDI

}| II (I

Sv

3

ФигЛ

Г

Ам5

| Беркс А | |||

| и др | |||

| Предварительное рассмотрение логической конструкции электронного вычислительного устройства: Кибернетический сборник | |||

| М.: Мир, 1964, № 9, с | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Авторское свидетельство СССР по заявке № 3732605/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-09-23—Подача