Итобретеине относится к нифро- Boi i вычислительной технике и может быть использовано в запоминающих устройствах и многоканальных устройствах коммутации.

Цель изобретения. - повышение достоверности контроля.

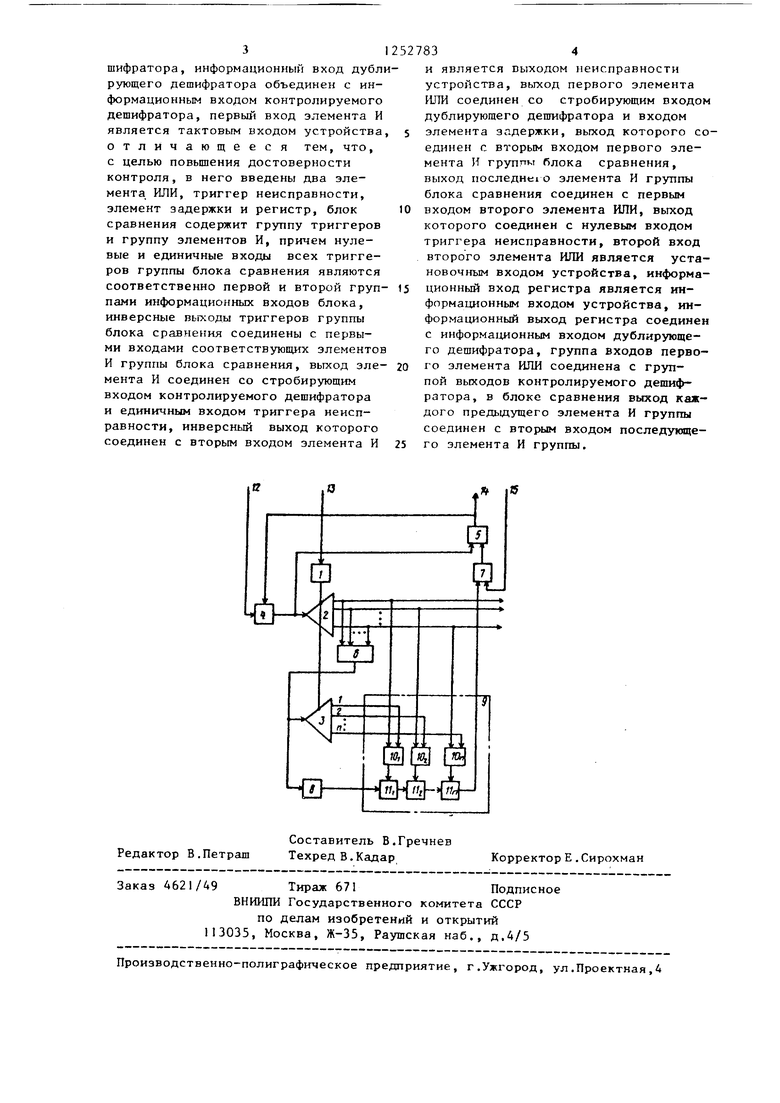

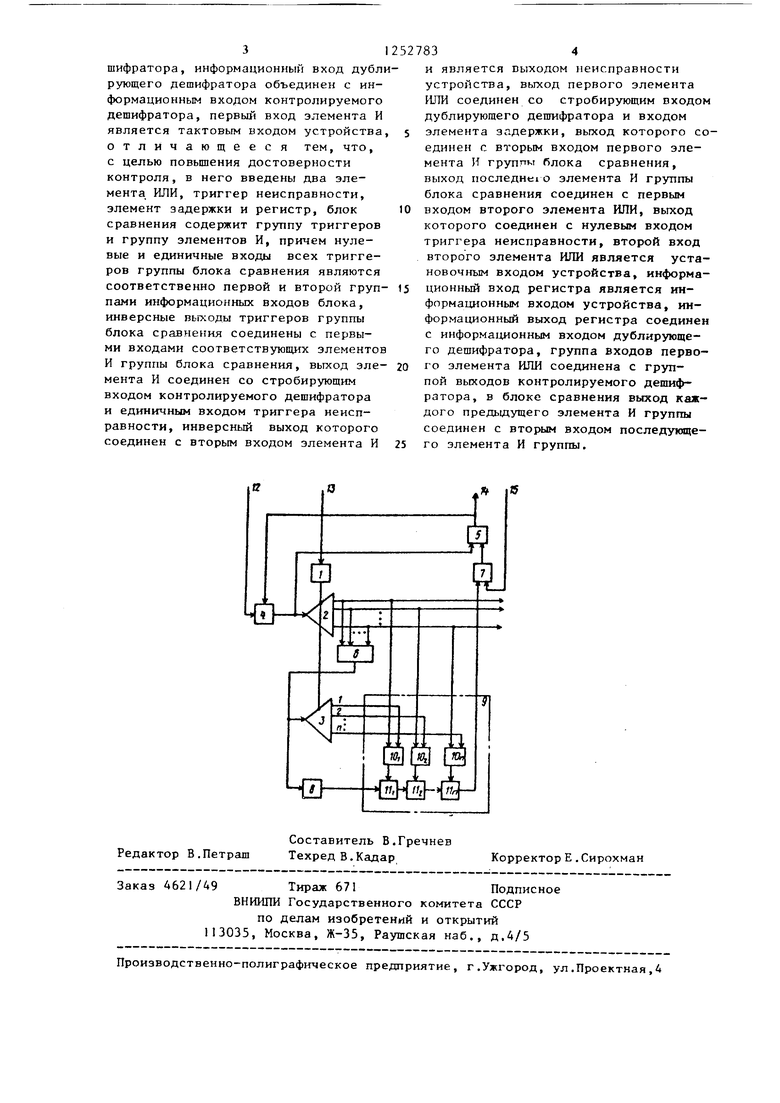

На чертеже приведена функциональная схема устройства для контроля дешифратора и подключенный к нему контролирумый дешифратор.

Приняты следующие обозначения: регистр 1, контролируемый 2 и дублирующий 3 дешифраторы, элемент И 4, триггер 5 неисправности, элементы ИЛИ 6 и 7, элемент 8 задержки, блок 9 сравнения, группа 10 триггеров блока 9 сравнения, группа 11 элементов И блока 9 сравнения, тактовый вход 12 устройства, информаци- оиньгй вход 13 устройства, выход 14 неисправности устройства, установочный вход 15 устройства.

Устройство работает следующим образом.

Дешифрируемый код с информационного входа 13 устройства поступает на регистр 1, с выхода которого поступает на информационные входы контролируемого 2 и дублирующего 3 дешифраторов , Сигнал опроса поступает с тактового входа 12 устройства на первый вход элемента И 4. В исходном состоянии триггер 5 неисправности находится в нулевом состоянии, поэтому сигнал опроса проходит через элемент И 4 на стробирующий вход контролируемого дешифратора 2 и eдии гчный вход триггера 5 неисправности, запрещая прохождение очередного импульса опроса.

Сигнал с выхода контролируемого дешифратора 2 устанавливает в едининое состояние соответствующий тригг группы 10 и через первый элемент ИЛИ 6 поступает на стробирукиций вхо дублирующего дешифратора 3 и элемента 8 задержки.

Сигнал с выхода дублирующего дешифратора 3 устанавливает в нулевое состояние соответствующий триггер группы 1 О.

Если деш {фраторы 2 и 3 работают правильно, то к моменту поступления сигнала на второй вход первого элемента И группы 11 с выхода элемента 8 задержки все триггеры группы 10 оудут находиться в нулевом состояни

0

и сигнал с выхода элемента 8 задержки пройдет через последовательно соединенные элементы И группы 1 1 на вход второго элемента ИЛИ 7 и установит в нулевое состо5}ние триггер неисправности. Таким образом, разрешается прохождение очередного сигнала опроса через элемент И 4.

В том случае, когда один из дешифраторов 2 и 3 неисправен, сигналы у них могут формироваться на разных выходах. При этом один из триггеров группы 10, установленный-в единичное состояние сигналом с вы- 5 хода дешифратора 2, не будет сброшен в нулевое состояние сигналом с выхода дешифратора 3. Сигнал с вькода элемента 8 задержки не пройдет на установку в нулевое состояние триггера 5 неисправности. На выходе 14 неисправности устройства при этом формируется нулевой сигнал, говорящий о неисправности дешифратора, и дальнейший опрос дешифратора 2 будет запрещен до того момента, пока триггер 5 неисправности не будет установлен в нулевое состояние сигналом начальных установок по установочному входу 15 устройства.

Если неисправность контролируемого дешифратора 2 приводит к отсутст- ,вию сигналов на его выходах, то и в этом случае триггер 5 неисправности останется в единичном состоянии, поскольку будет отсутствовать сигнал на выходе первого элемента ИЛИ 6.

Выбранная структура блока 9 сравнения позволяет обнаружить короткие импульсные помехи, возникающие на выходах контролируемого дешифратора 2 в интервалах между сигналами опроса.

Состояние триггеров группы 10 блока 9 сравнения позволяет определить неисправный выход контролируемого дешифратора 2.

5

0

5

0

5

Формула изобретени

Устройство для контроля дешифратора, содержащее дублирующий дешифратор, блок сравнения и элемент И, причем группа выходов дублирующего дешифратора соединена с первой груп- пой информационных входов блока сравнения, вторая группа информа- ционньп входов которого соединена с группой выходов контролируемого де3

шифратора, информационный вход дублирующего дешифратора объединен с информационным входом контролируемого дешифратора, первый вход элемента И является тактовым входом устройства отличающееся тем, что, с целью повьш1ения достоверности контроля, в него введены два элемента ИЛИ, триггер неисправности, элемент задержки и регистр, блок сравнения содержит группу триггеров и группу элементов И, причем нулевые и единичные входы всех триггеров группы блока сравнения являются соответственно первой и второй груп- пами информационных входов блока, инверсные выходы триггеров группы блока сравнения соединены с первыми входами соответствующих элементов И группы блока сравнения, выход эле- мента И соединен со стробирующим входом контролируемого дешифратора и единичным входом триггера неисправности, инверсный выход которого соединен с вторым входом элемента И

834

и является выходом неисправности устройства, выход первого элемента ИЛИ соединен со стробирующим входом дублирующего дешифратора и входом элемента задержки, выход которого соединен с вторым входом первого элемента И группм блока сравнения, выход последие о элемента И группы блока сравнения соединен с первым входом второго элемента ИЛИ, выход которого соединен с нулевым входом триггера неисправности, второй вход второго элемента ИЛИ является установочным входом устройства, информационный вход регистра является информационным входом устройства, информационный выход регистра соединен с информационным входом дублирующего дешифратора, группа входов первого элемента ИЛИ соединена с группой выходов контролируемого дешифратора, в блоке сравнения выход каждого предыдущего элемента И группы соединен с вторым входом последующего элемента И группы.

в

Редактор В.Петраш

Составитель В.Гречнев Техред В.Кадар

Заказ 4621/49 Тираж 671Подписное

ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор Е. Сирохман

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дешифратора | 1987 |

|

SU1495801A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU972598A1 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| Устройство для поиска перемежающихся неисправностей | 1985 |

|

SU1262502A1 |

| Устройство для считывания информации | 1983 |

|

SU1140138A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Тренажер оператора радиоэлектронной аппаратуры | 1989 |

|

SU1658193A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1072102A1 |

| Устройство для ввода информации | 1988 |

|

SU1539763A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в запоминающих устройствах при контроле адресных трактов и в многоканальных устройствах коммутации. Целью устройства является повьппение достоверности контроля. Сигналы с выхода ; контролируемого дешифратора устанавливают в единичное состояние соответствующие триггеры группы блока сравнения и через первый элемент ИЛИ. опрашивает дублирующий дешифратор, информационные входы которого объединены с информационным входом контролируемого дешифратора. Выходы дублируклцего дешифратора устанавливают в нулевое состояние соответстг- вующие триггеры группы блока сравнения . После этого через элемент задержки анализируется состояние группы триггеров. При ненулевом состоянии триггеров формируется сигнал неисправности. 1 ил. i

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| - М: Мир, 1972, с | |||

| Приспособление для нагрузки тендеров дровами | 1920 |

|

SU228A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Там же, с | |||

| Приспособление для подачи воды в паровой котел | 1920 |

|

SU229A1 |

Авторы

Даты

1986-08-23—Публикация

1983-04-20—Подача