31495801

Изобретение относится к автоматике и вычислительной т€ хнике и может быть использовано при построении запоминающих устройств и многоканальных уст- ройстн коммутации.

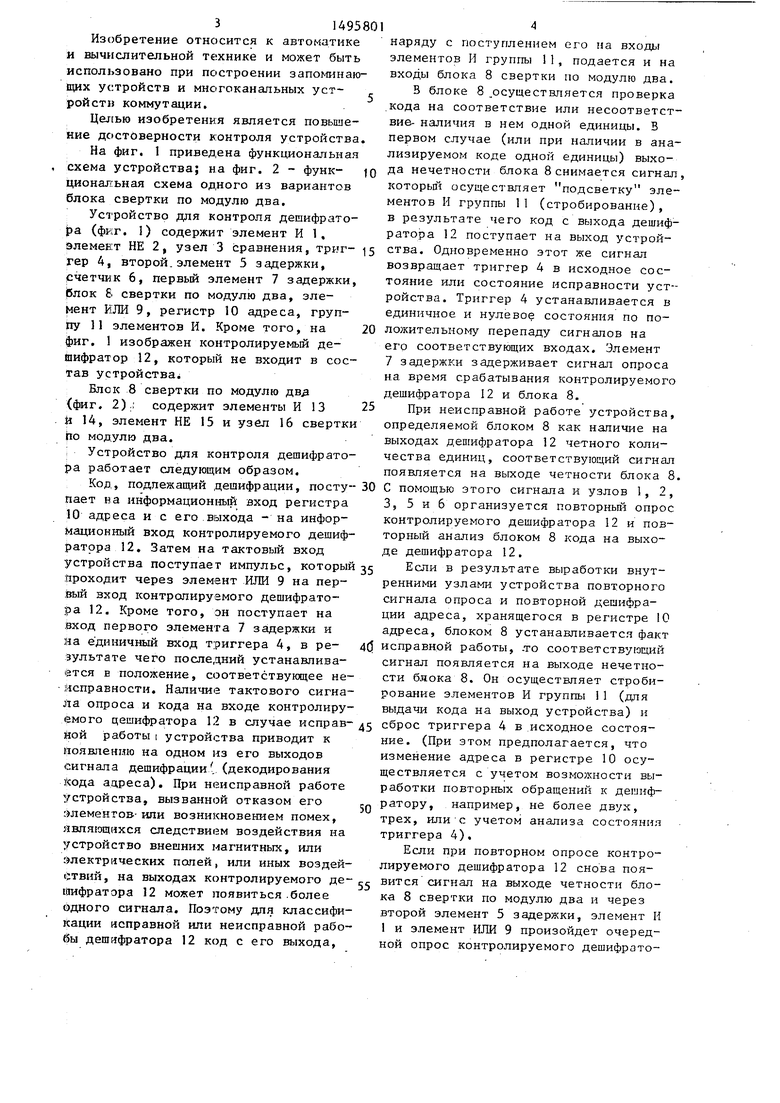

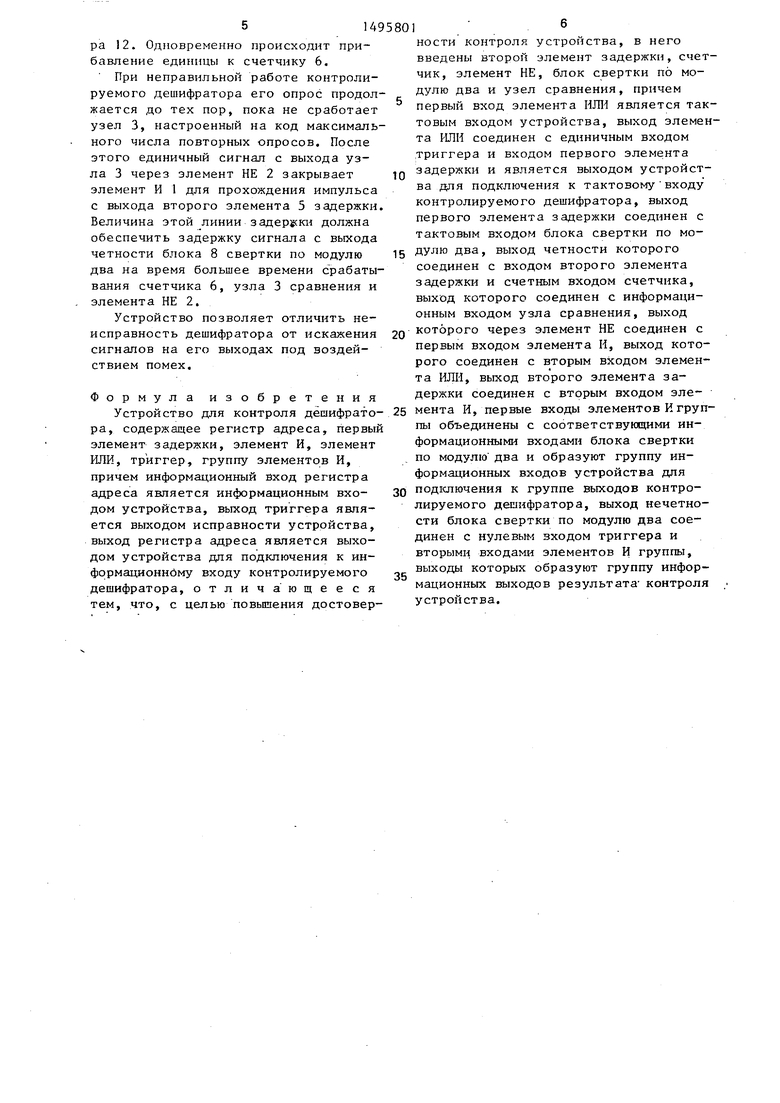

Uejrbra изобретения является повышение достоверности контроля устройства. На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функ- ю ционал:ьная схема одного из вариантов блока свертки по модулю два.

Устройство для контроля дешифратора (фкг. I) содержит элемент И 1, элемент НЕ 2, узел 3 сравнения, триг- 5 гер А, второй.элемент 5 задержки, счетчик 6, первьй элемент 7 задержки, блок 8 свертки по модулю два, элемент ИЛИ 9, регистр 10 адреса, группу 11 элементов И. Кроме того, на 20 фиг. 1 изображен контролируемый дешифратор 12, который не входит в состав устройства

Блек 8 свертки по модулю двд (фиг. 2).; содержит элементы И 13 25 .и 14, элемент НЕ 15 и узел 16 свертки по модулю два.

: Устройство для контроля дешифратора работает следующим образом.

Код, подлежащий дешифрации, посту- 30 пает на информационный вход регистра 10 адреса и с его выхода - на информационный вход контролируемого дешифратора 12, Затем на тактовый вход устройства поступает импульс, который 35 йроходит через элемент ИЛИ 9 на пер- :Вый вход контролируемого дешифратора 12. Кроме того, он поступает на вход первого элемента 7 задержки и на единичный вход триггера 4, в ре- дО зультате чего последний устанавлива- йтся Е положение, соответствующее неисправности. Наличие тактового сигнала опроса и кода на входе контролируемого дешифратора 12 в случае исправ- дз ной работы I устройства приводит к иоявленшо на одном из его выходов сигнала дешифрации/, (декодирования Кода адреса). При неисправной работе устройства, вызванной отказом его . ; лементов-ипи возникновением помех, 55вля1ощихся следствием воздействия на устройство внешних магнитных, или .электрических попей, или иных воздействий, на выходах контролируемого де- с Ейифратора 12 может появиться .более одного сигнала. Поэтому для классификации нсправной или неисправной рабо- $ы дешифратора 12 код с его выхода.

наряду с поступлением его на входы элементов И группы 11, подается и на входы блока 8 свертки по модулю два.

В блоке 8 осуществляется проверка кода на соответствие или несоответствие- наличия в нем одной единицы. В первом случае (или при наличии в анализируемом коде одной единицы) выхода нечетности блока 8 снимается сигнал которьй осуществляет подсветку элементов И группы 11 (стробирование), в результате чего код с выхода дешифратора 12 поступает на выход устройства. Одновременно этот же сигнал возвращает триггер 4 в исходное состояние или состояние исправности устройства. Триггер 4 устанавливается в единичное и нулевое состояния по положительному перепаду сигналов на его соответствующих входах. Элемент 7 задержки задерживает сигнал опроса на время срабатывания контролируемого дешифратора 12 и блока 8.

При неисправной работе устройства, определяемой блоком 8 как наличие на выходах дешифратора 12 четного количества единиц, соответствующий сигнал появляется на выходе четности блока 8 С помощью этого сигнала и узлов 1, 2, 3, 5 и 6 организуется повторньй опрос контролируемого дешифратора 12 и повторный анализ блоком 8 кода на выходе дешифратора 12.

Если в результате выработки внутренними узлами устройства повторного сигнала опроса и повторной дешифрации адреса, хранящегося в регистре 10 адреса, блоком 8 устанавливается факт исправной работы, .то соответствующий сигнал появляется на выходе нечетности блока 8. Он осуществляет стробирование элементов И группы 11 (для выдачи кода на выход устройства) и сброс триггера 4 в исходное состояние. (При этом предполагается, что изменение адреса в регистре 10 осуществляется с учетом возможности выработки повторных обращений к дешифратору, например, не более двух, трех, или с учетом анализа состояния триггера 4).

Если при повторном опросе контролируемого дешифратора 12 снова появится сигнал на выходе четности блока 8 свертки по модулю два и через второй элемент 5 задержки, элемент И 1 и элемент ИЛИ 9 произойдет очередной опрос контролируемого дешифрато514

ра 12. Одновременно происходит прибавление единицы к счетчику 6.

При неправильной работе контролируемого дешифратора его опрос продолжается до тех пор, пока не сработает узел 3, настроенный на код максимального числа повторных опросов. После этого единичный сигнал с выхода узла 3 через элемент НЕ 2 закрывает элемент И 1 для прохождения импульса с выхода второго элемента 5 задержки Величина этой линии задер$ски должна обеспечить задержку сигнала с выхода четности блока 8 свертки по модулю два на время большее времени срабатывания счетчика 6, узла 3 сравнения и элемента НЕ 2.

Устройство позволяет отличить неисправность дешифратора от искажения сигналов на его выходах под воздействием помех.

Формула изобретения

Устройство для контроля дешифрато- ра, содержащее регистр адреса, первый элемент задержки, элемент И, элемент ИЛИ, триггер, группу элементов И, причем информационный йход регистра адреса является информационным вхо- дом устройства, выход триггера является выходом исправности устройства, выход регистра адреса является выходом устройства для подключения к ин- формационнйму входу контролируемого дешифратора, отличающееся тем, что, с целью повышения достовер1 . .

ности контроля устройства, в него введены второй элемент задержки, счетчик, элемент НЕ, блок свертки по модулю два и узел сравнения, причем первый вход элемента ИЛИ является тактовым входом устройства, выход элемета ИЛИ соединен с единичным входом триггера и входом первого элемента задержки и является выходом устройства для подключения к тактовому входу контролируемого дешифратора, выход первого элемента задержки соединен с тактовым входом блока свертки по модулю два, выход четности которого соединен с входом второго элемента задержки и счетным входом счетчика, выход которого соединен с информационным входом узла сравнения, выход которого через элемент НЕ соединен с первым входом элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход второго элемента задержки соединен с вторым входом элемента И, первые входы элементов И группы объединены с соответствующими информационными входами блока свертки по модулю два и образуют группу информационных входов устройства для подключения к группе выходов контролируемого дешифратора, выход нечетности блока свертки по модулю два соединен с нулевым входом триггера и вторыми входами элементов И группы, выходы которых образуют группу информационных выходов результата контроля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1072102A1 |

| Запоминающее устройство с автономным контролем | 1987 |

|

SU1439685A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU972598A1 |

| Устройство для контроля обработки двоичной информации | 1982 |

|

SU1089581A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для сопряжения абонентов с общей магистралью | 1981 |

|

SU1022142A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении запоминающих устройств и многоканальных устройств коммутации. Цель изобретения - повышение достоверности контроля устройства. Устройство содержит элемент И 1, элемент НЕ 2, узел 3 сравнения, триггер 4, второй элемент задержки 5, счетчик 6, первый элемент задержки 7, блок 8 свертки по модулю два, элемент ИЛИ 9, регистр 10 адреса, группу 11 элементов И. На информационный вход контролируемого дешифратора 12 поступает код с регистра 10 адреса. Через элемент ИЛИ 9 происходит опрос контролируемого дешифратора 12, выходы которого соединены с входами блока 8 свертки по модулю два и первыми входами соответствующих элементов И группы 11. Если появляется сигнал на выходе нечетности блока 8, то разрешается прохождение сигналов с выходов дешифратора 12 через элементы И группы 11 на выход устройства и сбрасывается в нулевое состояние триггер 4 (он был установлен в единичное состояние одновременно с опросом дешифратора 12). Если появляется сигнал на выходе четности блока 8, то прибавляется единица к счетчику 6 и происходит повторный опрос дешифратора 12 через второй элемент задержки 5, элемент И 1 и элемент ИЛИ 9. Так продолжится до появления сигнала на выходе четности блока 8 или появления сигнала на выходе узла 3 сравнения, который с помощью элемента НЕ 2 блокирует элемент И 1. 2 ил.

7

И

7

Фиг. I

/

| Устройство для контроля дешифратора | 1984 |

|

SU1179343A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля дешифратора | 1983 |

|

SU1252783A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-23—Публикация

1987-11-23—Подача