Изобретение относится к запоминающим устройствам и может быть исполь зовано в составе специализированных цифровых вычислительных машин (CIIBM) или систем обработки и передачи цифровых данных.

Известно запоминающее устройство с автономным контролем, содержащее два поля памяти, одно из которых служит для хранения информации, а в другом расположено содержимое адреса ячейки ЗУ, к которой в настоящий момент происходит обращение, а также содержит адресный блок, включающий регистр адреса и дешифратор адресов, выходной -регистри схему сравнения текущего адреса с содержимым, хранящимся в дополнительной части ячё$1ки поля памяти, выбираемой по адресу 1 .

Недостатком этого устройства является отсутствие в его составе . средств контроля информационной части, а также тракта дэиифратора и накопителя, что снижает его надежность.

Наиболее близким техническим решением к изобретению, являе1ся запоминающее устройствос автономным : контролем/- содержащее регистр адреса, выход которого через дешифратор

адресов подключен ко входу накопителя, соединенного соответствующими выходами со входами регистра, причем любая ячейка памяти наряду с информационной частью имеет дополнительные разряды, в которых хранятся контрольные признаки свертки (например, по модулю 2 или 3), относящиеся как к коду числа, так и к коду

10 адреса, по которому выбирается дан-; ная ячейка 2.

Недостатком известного устройства является низкая разрешающая способ ность автоматического определения

15 места неисправности, что снижает его надежность. .

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается

20 тем, что в запоминающее устройство с автономным контролем, содержащее регистр адреса, выходы которого соединены .с первым входом дешифратора адреса и входами первого блока

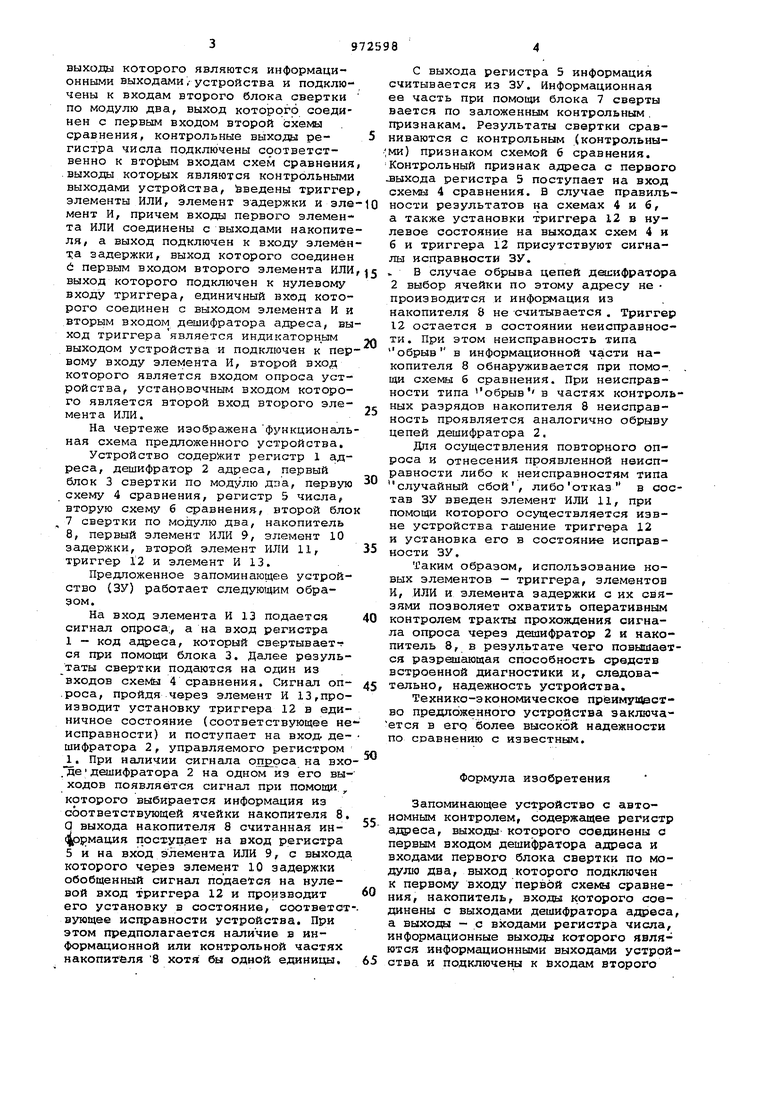

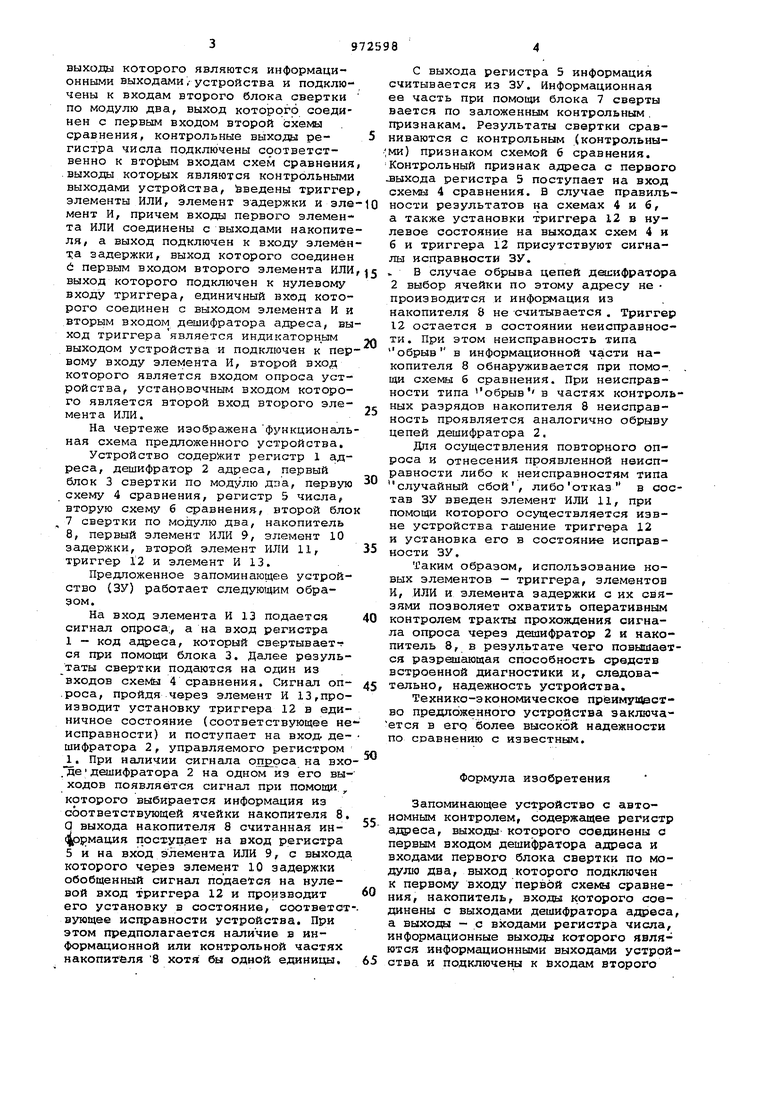

25 свертки по модулю два, выход которого подключен к первому входу первой схекы сравнения, накопитель, входы которого соединены с выходами дешифратора адреса, а выходы - с вхо30дами регистра числа, информационные выходы которого являются информационными выходами,-устройства и подключены к входам второго блока сзвертки по модулю два, выход которого соединен с первым входом второй схемы сравнения, контрольные выходы регистра числа подключены соответственно к вторым входам схем сравнения .выходы которых являются контрольными выходами устройства, введены триггер элементы ИЛИ, элемент задержки и эле мент И, причем входы первого элемента ИЛИ соединены с выходами накопите ля, а выход подключен к входу элемён т:,а задержки, выход которого соединен U первым входом второго элемента ИЛИ выход которого подключен к нулевому входу триггера, единичный вход которого соединен с выходом элемента И и .вторым входом дешифратора адреса, вы ход триггера является индикаторн.ым выходом устройстйа и подключен к пер вому входу элемента И, второй вход которого является входом опроса устройства, установочным входом которого является второй вход второго элемента ИЛИ. На чертеже изображена функциональ ная схема предложенного устройства. Устройство содер5кит регистр 1 адреса, дешифратор 2 адреса, первый блок 3 свертки по модулю дза, первую схему 4 сравнения, регистр 5 числа, вторую схему б сравнения, второй бло 7 свертки по модулю два, накопитель 8, первый элемент ИЛИ 9, элемент 10 задержки, второй элемент ИЛИ 11, триггер 12 и элемент И 13. Предложенное запоминающее устройство (ЗУ) работает следующим образом. На вход элемента И 13 подается сигнал опроса;, а на вход регистра 1 - код адреса, который свертывается при ПОМОВ5И блока 3. Далее результаты свертки подаются на один из входов cxeNfei 4 сравнения. Сигнал оп.роса, пройдя через элемент И 13,производит установку триггера 12 в единичное состояние (соответствующее не исправности) и поступает на вход, дешифратора 2, управляемого регистром 1. При наличии сигнала опроса на вхо .де дешифратора 2 на одном иэ его выходов появляется сигнал при помощи , которого выбирается информация из соответствующей ячейки накопителя 8. а выхода накопителя 8 считанная ин |ррмация поступает на вход регистра 5 и на вход элемента ИЛИ 9, с выхода которого через элемент 10 задержки обобщенный сигнсш подается на нулевой вход триггера 12 и производит его установку в состояние, соответст вующее исправности устройства. При этом предполагается наличие в информационной или контрольной частях накопителя 8 хотя бы одной единицы. С выхода регистра 5 информация считывается из ЗУ. Информационная е часть при помощи блока 7 сверты вается по заложенным контрольным. признакам. Результаты свертки сравниваются с контрольным (контрольныи) признаком схемой б сравнения. Контрольный признак адреса с первого выхода регистра 5 поступает на вход схемы 4 сравнения. В случае правильности результатов на схемах 4 и б, а также установки триггера 12 в нулевое состояние на выходах схем 4 и 6 и триггера 12 присутствуют сигналы исправности ЗУ. - В случае обрыва цепей донифратора 2 выбор ячейки по этому адресу не производится и информация из накопителя 8 не считывается . Триггер 12 остается в состоянии неисправности. При этом неисправность типа обрыв в информационной части накопителя 8 обнаруживается при помо-. щи схемы 6 сравнения. При неисправности типа обрыв в частях контрольных разрядов накопителя 8 неисправность проявляется аналогично обрыву цепей дешифратора 2, Для осуществления повторного опроса и отнесения проявленной неисправности либо к неисправностям типа случайный сбой , либоотказ в состав ЗУ введен элемент ИЛИ 11, при помощи которого осуществляется извне устройства гашение триггера 12 и установка его в состояние исправности ЗУ. Таким образом, использование новых элементов - триггера, элементов И, ИЛИ и элемента задержки с их связями позволяет охватить оперативным контролем тракты прохождения сигнала опроса через дешифратор 2 и накопитель 8, в результате чего повышается разрешающая способность средств встроенной диагностики и, следовательно, надежность устройства. Технико-экономическое преимущество предложенного устройства эаключается в его более высокой надежности по сравнению с известным. Формула изобретения Запоминающее устройство с автономным контролем, содержащее регистр адреса, выходы- которого соединены с первым входом дешифратора адреса и входами первого блока свертки по модулю два, выход которого подключен к первому входу первой схемы сравнения, накопитель, входы которого соединены с выходами дешифратора адреса, а выходы - с входами регистра числа, информационные выходы которого являются информационными выходами устройства и подключены к йходам второго

блока свертки по модулю два, выход которого соединен с первым входом .второй схемы сравнения, контрольные выходы регистра числа подключены соответственно к вторым входам схем сравнения, выходы которых являются контрольными выходами устройства, отличающееся тем, что, с целью повышения надежности устройст|ва, в него введены триггер, элементы ИЛИ, элемент задержки и элемент И, причем входы первогоэлемента ИЛИ соединены с выходами накопителя, а выход подключен к входу элемента эа;Держки, выход которого соединен с первым входом второго элемента ИЛИ, выход которого подключен к нулевому

входу триггера, единичный вход которого соединен с выходом элемента И я вторым входом дешифратора адреса, выход триггера является индикаторным выходом устройства и подключен к первому входу элемента И, второй вход которого является входом опроса устройства, установочным входом которого является второй вход второго элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. Патент США 3963908, кл. G06 FH/IO, опублик. 1975. 2. Авторское свидетельство СССР 467409, кл. G 11 С 29/00, 1974

5 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1072102A1 |

| Запоминающее устройство с автономным контролем | 1987 |

|

SU1439685A1 |

| Устройство для контроля дешифратора | 1987 |

|

SU1495801A1 |

| Устройство для сопряжения магистралей | 1986 |

|

SU1365088A1 |

| Запоминающее устройство с резервированием | 1980 |

|

SU963088A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Запоминающее устройство с контролем | 1988 |

|

SU1508287A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1185400A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

Авторы

Даты

1982-11-07—Публикация

1981-04-15—Подача