Изобретение относится к цифровой вычислительной технике и предназначено для использования в составе сп циализированных цифровых вычислител ных машин (liBrJ или систем обработк и передачи цифровых данных. Известно запоминающее устройство (ЗУ) с автономным контролем, содержащее регистр адреса, выход которог чррез дешифратор адресов подключен к входу накопителя, соединенного со отвётствующими выходами с входами регистра. Любая ячейка этого ЗУ нар ду с информационной частью имеет до полнительные разряды, в которых хра нятся контрольные признаки свертки (например, по модулю 2 или 3) , относящиеся как к коду числа, так и к коду адреса, по которому выбирается данная ячейка. В процессе считывания содержимого из ячейки происходит свертывание ее информационной части и сравнение результатов свертки с соот ветствующими контрольными признаками Второй контрольный признак (признаки сравнивается с результатом свертки содержимого регистра адреса 1, I Недостатком известного устройства является отсутствие в его составе средств контроля тракта дешифратора и накопителя, что ограничивает область применения. Наиболее близким по технической сущности к предлагаемому является запоминающее устройство с автономным контролем, состоящее из регистра адреса, связанного через дешифратор с накопителем, в котором Нар5аду с числовой информацией хранятся контрольные признаки информационной части и текущего адреса, регистра числа подключенного к выходам накопителя, блоков сравнения, связанных с соответствующими блоками сверток и с кон трольными разрядами регистра числа, элемента ИЛИ, сопряженного с выходом накопителя, триггера контроля цепей опроса дешифратора и накопителя и элемента И, первый вход которого явл ется входом опроса устройства. Второй вход элемента И связан с выходом триггера контроля. Вход первого блока свертки подключен к выходу .регистра адреса, вход второго блока свертки - к выходу регистра числа. Однако несмотря на наличие в составе ЗУ встроенных средств диагностики основных частей устройства решение о состоянии его исправности принимается либо при применении специальных проверочных стендов, либо в устройстве управления используемой аппаратуры (СОВМ, система для обработки цифровых-данных} на основе .прогона ряда диагностическихтестов. Это приводит к увеличению времени, необходимого для оперативного анализа состояния ЗУ при каждом обращении к нему, а следовательно, к снижению быстродействия устройства. Цель изобретения - повышение бы-; стродействия устройства. I Поставленная цель достигается тем. что в устройство, содержащее регистр адреса, выход которого соединен с первым входом дешифратора и с входом первого блока свертки по модулю два, выход которого подключен к первому входу первого блока сравнения, накопитель , входы которого соединены с выходами дешифратора, а выходы - с входами первого элемента ИЛИ и с входами регистра адреса, информационные выходы которого являются информационными выходами устройства и подключены к входам второго блока свертки по модулю два, выход которого соединен с первым входом второго блока сравнения, первый элемент И, выход которого подключен к второму входу дешифратора и к первому входу первого триггера, второй вход которого соединен с выходом, второго элемента ИЛИ, выход первого триггера подключен к первому входу первого элемента И и является индикаторным выходом устройства, второй вход первого элемента И является входом опроса устройства, установочным входом которого является первый вход второго элемента ИЛИ, контрольные выходы регистра адреса подключены соответственно к вторым входам первого и второго блоков сравнения, введены .элементы задержки/ элементы И, второй, третий и четвертый триггеры, первые входы которых соединены с вторым входом дешифратора и подключены к входу первого элемента задержки, выход которого соединен с первыми входами второго и третьегоэлементов И и с входом второго элемента задержки, выход которого соединен с первым входом четвертого элемента И, выход последнего соединен с вторым входом второго элемента ИЛИ, второй вход второго элемента И соединен .с выходом первого блока сравнения, второй вход третьего элемента И соединен с выходом второго блока сравнения, выход первого элемента ИЛИ подключен к второму входу второго триггера, выходы второго и третьего элементов И подключены к вторым входам третьегр и четвертого триггеров, выходы второго, третьего и четвертого .триггеров подключены соответственно к второму, третьему и четвертому входам четвертого элемента И и соединены с первыми входами пятого, шестого и седьмого элементов И, вторые входы которых являются управляющим входом устройства, выходы пятого, шестого и седьмого элементов И являются контрольными выходами устройства.

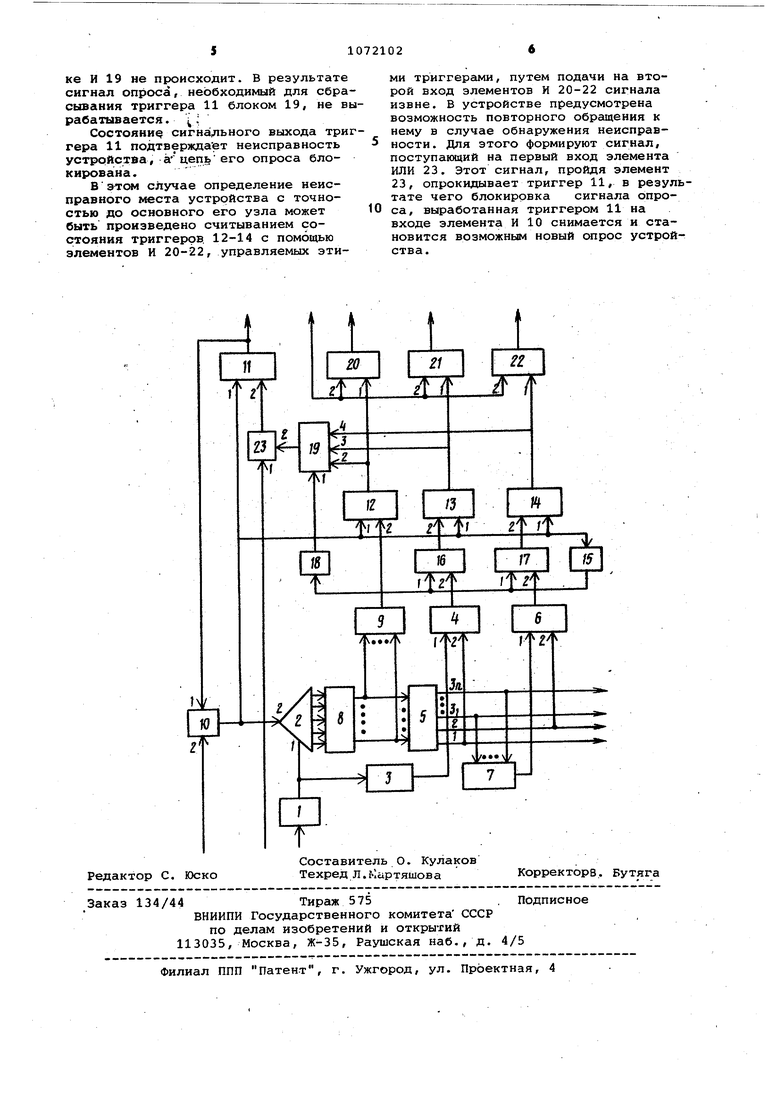

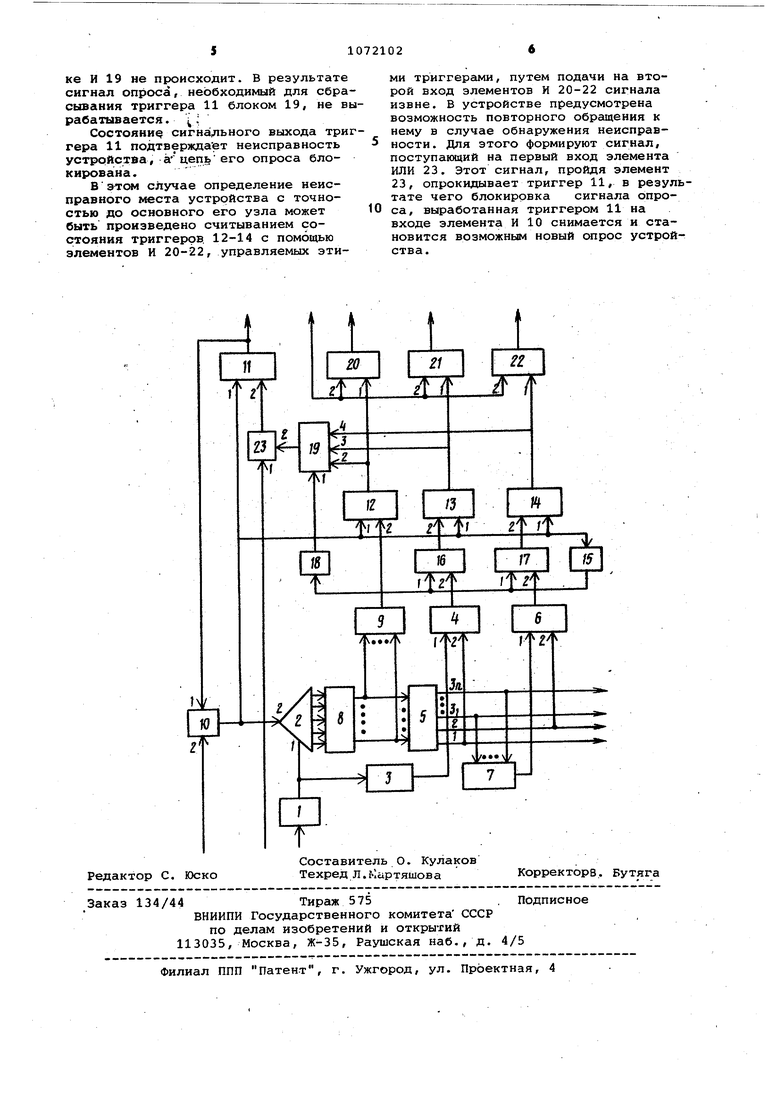

На чертеже приведена блок-схема запоминающего устройства с автономным контролем.

Выход регистра адреса 1 связан с первым входом дешифратора 2 и через первый блок 3 свертки подключен к первому входу первого блока 4 сравнения. Второй вход блока 4 подключен к первому выходу регистра 5 числа, второй и третьи выходы которого соединены соответственно с вторым входом второго блока- 6 сравнения и с входами второго блока 7 свертки. Выход блока соединен с первым входом блока 6. Каждый из входов регистра 5 подключен к соответствующему выходу накопителя 8 и связан с одним, из входов первого элемента ИЛИ 9. Вход накопителя 8 соединен с выходом дешифратора 2, второй вход которого подключен к выходу первого элемента И 10, к первому входу триггеров 11-14 и к входу первого элемента 15 задержки. Выход элемента 15 связан с первым входом второго и третьего элементов И 16 и 17 и через второй элемент 18задержки подключен к первому входу четвертого элемента И 19, второй, третий и четвертый входы которого соединены соответственно с единичным выходом триггеров 12-14 и с первым входом пятого, шестого и седьмого элементов И 20-22. Вторые входы элементов 2022 объединены и являются управляющим входом устройства. Второй ( установочный j вход устройства соединен с первым входом второго элемента ИЛИ 23,,второй вход которого подключен к выходу элемента 19. Выход элемента 23 подсоединен к второму входу триггера 11, единичный выход которого является индикаторным выходом устройства и связан с первым входом элемента 10, второй вход которого является входом опроса устройства. Выход элемента ИЛИ 9 соединен с вторым входом триггера 12. Выход блока сравнения 4 подключен к второму входу элемента И 16, выход блока сравнения б - к вто рому входу элемента И 17. Выходы, элементов 16 и 17 подключены соответственно к второму входу триггеров 13 и 14. Выходы регистра 5 числа являются информационными выходами устройства, контрольными выходами которого являются выходы элементов 20-22.

Запоминающее устройство работает следующим образом.

Ка вход элемента И 10 подается опроса, а на вход регистра I код адреса, который свертывается при помощи блока 3. Далее результаты свертки подаются на первый вход блока 4 сравнения. Сигнал опроса, пройдя

через элемент И 10, производит установку триггеров 11-14 в единичное состояние (соответствующее неисправности и поступает на вход элемента 15 задержки и на вход дешифратора 2, управляемого регистром 1. При наличии сигнала опроса на входе дешифратора 2 на одном из его выходов появляется сигнал, при помощи которого выбирается информация из соответствующей ячейки накопителя 8. С выхода накопителя 8 считанная информация поступает на вход регистра 5 и на вход элемента ИЛИ 9. Числовой код, зафиксированный в регистре 5, свертывается при помощи блока 7 свертки и поступает на первый вход блока 6 сравнения. На второй вход этого блока подается значение контрольного признака частности числовой информации , который также считывается из накопителя 8 и запоминается в регистре 5. Значение второго (адресного) контрольного признака подается на второй вход блока 4 сравнения. Информация, считанная из выбранной ячейки накопителя 8, пройдя элемент ИЛИ 9, поступает на второй вход триггера 12, в результате чего последний меняет свое состояние. Состояние триггера 12 будет соответствовать состоянию исправности (при этом предполагается, что из выбранно ячейки накопителя 8 будет считана хотя бы одна единица). Этот случай соответствует исправности цепей опроса дешифратора и накопителя. Результаты контроля правильности считанной информации и выбранного адреса с выхода блоков 4 и 6 сравнения поступают соответственно на вторые входы элементов И 16 и 17. На первые входы этих элементов поступает сигнал с выхода элемента 15 задеря.ки. В случа правильности проверок четности элементами И 16 и 17 выдается сигнал, поступающий на второй вход триггеров 13 и 14 соответственно..В результате триггеры 13 и 14 изменяют свое состояние. Измененное состояние триггеров 12-14 фиксируются на втором, третьем и четвертом входах четверTofo §лемента И 19. Опрос элемента И 19 производится сигналом, выработанным элементом 15 и задержанным на элементе 18 задержки. С выхода элемента 19 считывается сигнал, который, пройдя элемент ИЛИ 23, изменяет состояние триггера.11, в результате чего устройством автоматически формируется обобщенное состояние исправности.

в случае неисправности какого-либо блока устройства хотя бы один из триггеров 12-14 не изменит состояния соответствующего..неисправности. Совпадения сигналов исправности на блоке И 19 не происходит. В результате сигнал опроса, необходимый для сбрасывания триггера 11 блоком 19, не вырабатывается . i,

Состояние сигнального выхода триггера 11 подтверждает неисправность устройства, а цепьего опроса блокирована.

В этом случае определение неисправного места устройства с точностью до основного его узла может быть произведено считыванием состояния триггеров. 12-14 с помощью элементов и 20-22, управляемых этими триггерами, путем подачи на второй вход элементов И 20-22 сигнала извне. В устройстве предусмотрена возможность повторного обращения к нему в случае обнаружения неисправности. Для этого формируют сигнал, поступающий на первый вход элемента ИЛИ 23. Этот сигнал, пройдя элемент 23, опрокидывает триггер 11, в результате чего блокировка сигнала опроса, выработанная триггером 11 на входе элемента И 10 снимается и становится возможным новый опрос устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1987 |

|

SU1439685A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU972598A1 |

| Запоминающее устройство | 1984 |

|

SU1236560A1 |

| Устройство для контроля дешифратора | 1987 |

|

SU1495801A1 |

| Устройство для сопряжения магистралей | 1986 |

|

SU1365088A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Устройство для контроля цифровых систем | 1980 |

|

SU955073A1 |

| Запоминающее устройство с резервированием | 1980 |

|

SU963088A1 |

| Запоминающее устройство | 1984 |

|

SU1203602A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С . АВТОНОМНЫМ КОНТРОЛЕМ, содержащее регистр адреса, выход которого соединен с первым входом дешифратора и с . входом первого блока свертки по мо-,. дулю два, выход которого подключен к первому входу первого блока сравнения , накопитель, входы которого соединены с Выходами дешифратора, а выходы - с входами первого элемента ИЛИ и с входами регистра адреса, информационные выходы которого являются информационными выходами устройства и подключены к входам второго блока свертки по модулю два, выход которого соединен с первым входом второго блока сравнения, первый элемент И, выход которого подключен к второму входу дешифратора и к первому входу первого триггера, второй вход которого соединен с выходом второго элемента ИЛИ, выход первого триггера подключен к первому входу первого элемента И и является индикаторным выходом устройства, второй вход пер- . вого элемента И является входом опроса устройства, установочным входом которого является первый вход второго элемента ИЛИ, контрольные выходы регистра адреса подключены соответственно к вторым входам первого и второго блоков сравнения, отличающеес я тем, что, с целью повышения бы--, стродействия контроля, оно содержит элементы задержки, элементы И, второй, третий и четвертый триггеры, первые входы которых соединены с вторым входом дешифратора и подключены к входу первого элемента задержки, выход которого соединен с первыми входами второго и третьего элементов И и с входом второго элемента задержки, выход которого соединен с первым входом(Четвертого элемента И, выход s последнего соединен с вторым входом (Л второго элемента ИЛИ, второй вход второго элемента И соединен с выходом первого блока сравкёния,второй вход третьего элемента И соединен с выходом второго блока сравнения, выход первого элемента ИЛИ подключен к второму входу второго триггера, вы ходы BTOpoiro и третьего элементов И подключены к вторьм входам третьего и четвертого триггеров, выходы второго, третьего и четвертого триггеров ю подключены соответственно к второму третьему и четвертому входам четвертого элемента И и соединены с первыми входами пятого, шестого и седьto мого элементов И, вторые входы которых являются управляющим входом устройств а, выходы пятого,шестогои седьмого элементов И являются контрольными выходами устройства, .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-02-07—Публикация

1982-10-25—Подача