Изобретение относится к вычислив тельной технике, а именно к специализированным вычислительным устройствам защиты от ошибок внешней памяти ЦВМ (накопителей на магнитных лентах, дисковой и оптической памяти) ,

Целью изобретения является повышение надежности устройства за счет защиты от ложных срабатываний синхросигналов.

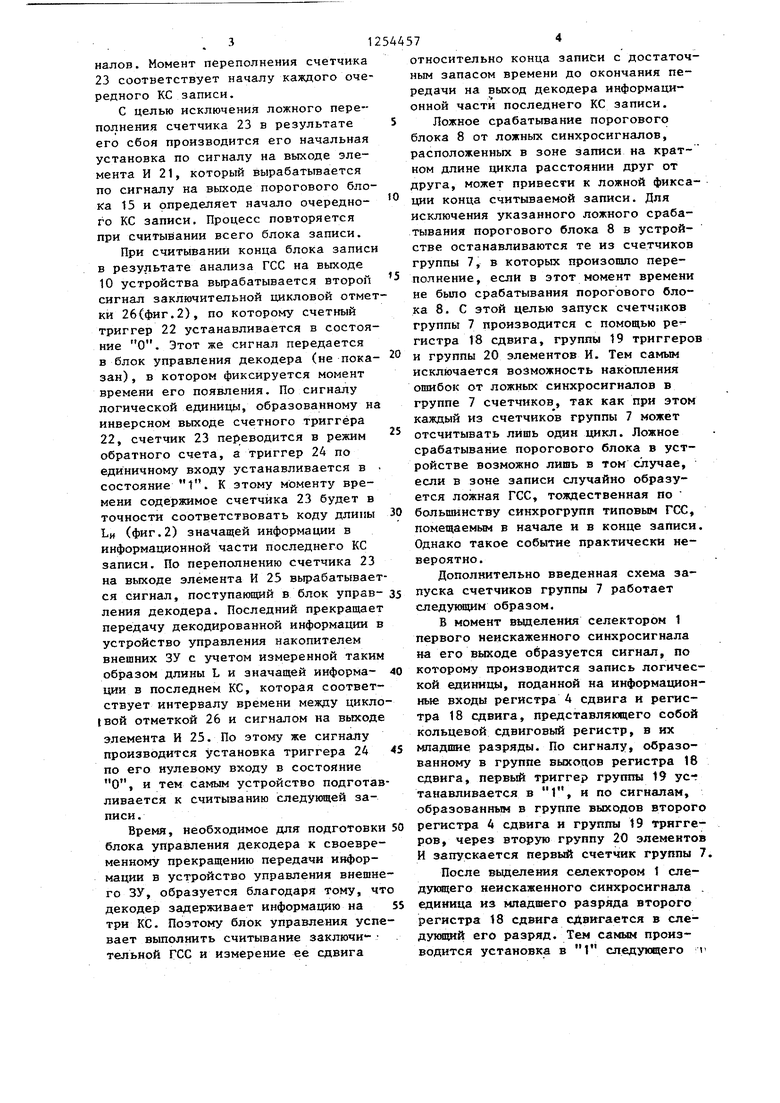

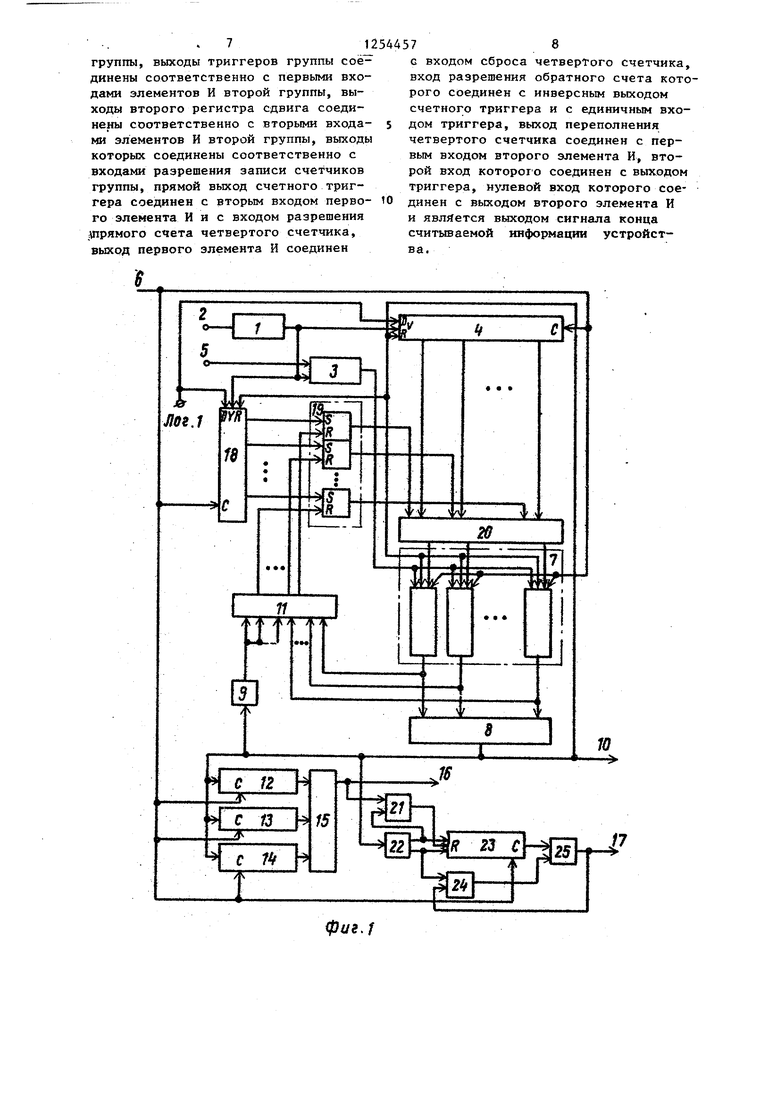

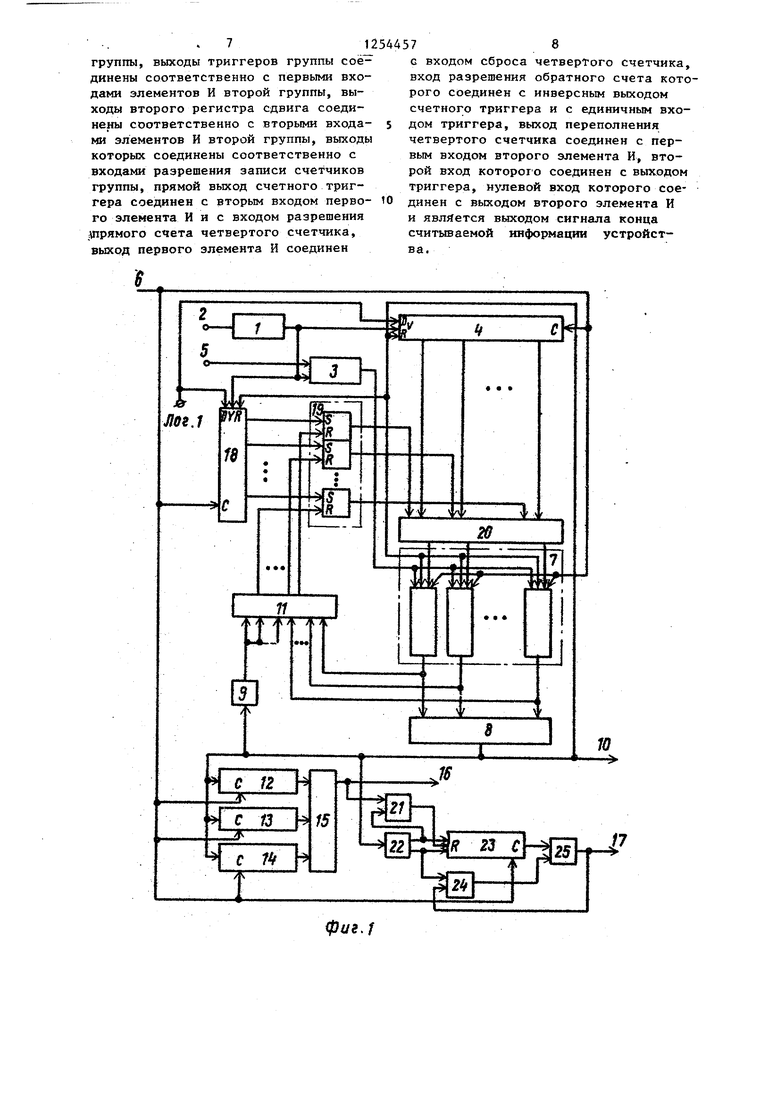

На фиг.1 приведена функциональная блок-схема устройства; на фиг.2 - формат конца записи на дорожке носителя информации, поясняющий работу устройства.

Устройство содержит селектор 1 модулированного сигнала, вход 2 модулированной информационной последовательности, регистры 3 и А сдвига, вход 5 демодулированной информационной последовательности, тактовый вход 6, группу 7 счетчиков, пороговый блок 8, элемент НЕ 9, выход 10 сигнала цикловой отметки, группу 11 элементов И, счетчики 12-14, порого- вый блок 15, выход 16 сигнала начала очередного кодового слова, выход 17 сигнала конца считываемой информации регистр 18 сдвига, группу 19 триггеров, группу 20 элементов И, элемент И 21, счетный триггер 22, счетчик 23, триггер 24, элемент И 25

На входы 2 и 5 устройства поступают сигналы, считанные с дорожки носителя информации.

Все блоки устройства реализуются по известным схемам и на типовых элементах средней степени интеграции расширенной серии интегральных схем (ЙС) типа К 155, Регистр 18 сдвига - это кольцевой сдвиговый регистр.

Устройство работает следующим образом,

В соответствии с логикой работы при кодировании записей блоковыми корректирукищ ми кодами с фиксированной длиной L блоков КС (кодовые елона) с высокой достоверностью необходимо определять конец зоны записи. Формирование конца считанной и восстановленной записи осуществляется при передаче в устройство управления внешнего запоминающего устройства значащей информации из информационной части последнего кодового слова записи. Следовательно, необходимо

фиксировать ее длину в последнем кодовом слове.

На фиг,2 приняты следующие обозначения: КС , и КС - предпоследнее и последнее кодовые слова (КС) записи соответственно; ГСС - группа синхросигналов; L - длина КС в битах; длина значащей информации в информационной части КС в битах; 26 - заключительная цикловая отметка,

В общем случае длина записи может быть не кратна длине блока КС, и, следовательно, информационная часть последнего КС будет не полностью заполнена значащей информацией. Обычно остальная часть заполняется нулями. Поэтому в процессе записи во внешнее ЗУ необходимо запоминать длину полез-- ной информации в информащюнной части последнего КС, а затем при. чтении с высокой надежностью считывать код этой длины.

в устройстве указанная длина значащей информации (Ц) последнего КС запоминается во внешнем ЗУ с помощью дополнительной заключительной группы синхросигналов, по формату тождественной для входа в цикловый синхронизм и записываемой в конце записи в пробел между соседними записями длиной в три КС, который образуется из-за начальной задержки декодера, равной времени передачи трех КС при исправлении ошибок кодом Рида-Соломо- 5 на. Задержка обусловлена конвейер- ньм принципом построения декодера и необходимостью первоначальной загрузки памяти блоков декодера в конвейерном вычислителе. Указанная

0

40

длина L запоминается путем соответ-.

ствуищего сдвига ГСС относительно последнего кодового слова КС, на величину L (см.фиг,2), а соответствующий пропуск заполняется нулями,

Фиксация конца считываемой записи осуществляется схемой, содержащей счетный триггер 22, триггер 24, счетчик 23, элементы И 21 и 25. Но первому сигналу цикловой отметки, образованному на выходе 10 устройства, счетный триггер 22, предварительно установленный в нулевое состояние, устанавливается в состояние 1. По сигналу логической единицы, образованной на первом выходе триггера 22, счетчик 23 (емкостью L) включается в режим непре- рьгоного прямого счета тактовых сиг

налов. Момент переполнения счетчика 23 соответствует началу каждого очередного КС записи.

С целью исключения ложного переполнения счетчика 23 в результате его сбоя производится его начальная установка по сигналу на выходе элемента И 21, который вырабатьгеается по сигналу на выходе порогового блока 15 и определяет начало очередного КС записи. Процесс повторяется при считывании всего блока записи.

При считывании конца блока записи в результате анализа ГСС на выходе 10 устройства вьфабатывается второй сигнал заключительной цикловой отметки 26{фиг.2), по которому счетный триггер 22 устанавливается в состояние О. Этот же сигнал передается в блок управления декодера (не показан) , в котором фиксируется момент времени его появления. По сигналу логической единицы, образованному на инверсном выходе счетного триггера 22, счетчик 23 переводится в режим обратного счета, а триггер 24 по единичному входу устанавливается в состояние t. К этому моменту времени содержимое счетчика 23 будет в точности соответствовать коду длины LK (фиг.2) значащей информации в информационной части последнего КС записи. По переполнению счетчика 23 на выходе элемента И 25 вырабатывается сигнал, поступакяций в блок управ- ления декодера. Последний прекращает передачу декодированной информации в устройство управления накопителем внешних ЗУ с учетом измеренной таким образом длины L и значащей информа- ции в последнем КС, которая соответствует интервалу времени между цикло |вой отметкой 26 и сигналом на выходе элемемта И 25. По этому же сигналу производится установка триггера 24 по его нулевому входу в состояние О, и тем самым устройство подготавливается к считыванию следующей записи.

Время, необходимое для подготовки блока управления декодера к своевременному прекращению передачи информации в устройство управления внешнего ЗУ, образуется благодаря; тому, чт декодер задерживает информацию на три КС. Поэтому блок управления успевает выполнить считывание заключи- тельной ГСС и измерение ее сдвига

5

0

5

относительно конца записи с достаточным запасом времени до окончания передачи на выход декодера информационной части последнего КС записи.

Ложное срабатывание порогового блока 8 от ложных синхросигналов, расположенных в зоне записи на крат- ном длине цикла расстоянии друг от друга, может привести к ложной фиксации конца считываемой записи. Для исключения указанного ложного срабатывания порогового блока 8 в устройстве останавливаются те из счетчиков группы 7, в которых произошло переполнение, если в этот момент времени не было срабатывания порогового блока 8. С этой целью запуск счетчиков группы 7 производится с помощью ре - гистра 18 сдвига, группы 19 триггеров и группы 20 элементов И. Тем самым исключается возможность накопления ошибок от ложных синхросигналов в группе 7 счетчиков, так как при этом каждый из счетчиков группы 7 может отсчитывать лишь один цикл. Ложное срабатывание порогового блока в устройстве возможно лишь в том случае, если в зоне записи случайно образуется ложная ГСС, тождественная по большинству синхрогрупп типовым ГСС, помещаемым в начале и в конце записи. Однако такое событие практически невероятно.

Дополнительно введенная схема запуска счетчиков группы 7 работает следукмцим образом.

В момент выделения селектором 1 первого неискаженного синхросигнала на его выходе образуется сигнал, по которому производится запись логической единицы, поданной на информационные входы регистра 4 сдвига и регистра 18 сдвига, представляющего собой кольцевой сдвиговый регистр, в их младшие разряды. По сигналу, образованному в группе выходов регистра 18 сдвига, первый триггер группы 19 устанавливается в 1, и по сигналам, образованным в группе выходов второго регистра 4 сдвига н группы 19 триггеров, через вторую группу 20 элемеитов И запускается первый счетчик группы 7.

После выделения селектором 1 сле- дукщего неискаженного синхросигнала единица из младшего разряда второго регистра 18 сдвига сдвигается в сле- дукяцнй его разряд. Тем самым производится установка в 1 следующего г

5

триггера группы 19. Во втором регистре 4 сдвига также происходит сдвиг единицы в следующий разряд, и по синалам, образованным в группе выходо второго регистра 4 и группе 19 триггеров, через вторую группу 20 эле- менто И запускается второй счетчик группы 7.

Процесс запуска повторяется аналогично после выделения селектором 1 каждого очередного синхросигнала. В результате могут быть запущены вс счетчики группы 7.

После появления на выходе порогового блока 8 первого сигнала цикловой отметки производится установка в ноль по входам сброса регистра 4 сдвига, регистра 18 сдвига и счетчиков группы 7. Тем самым устройство приготавливается к приему и обработке заключительной ГСС, записанной в конце записи.

Если в зоне записи появятся ложные синхросигналы, по которым будут запущены отдельные счетчики группы 7, и произойдет их переполнение без срабатьшания порогового блока 8, через первую группу 11 элементов И производится установка в О по нулевым входам соответствугацих триггеров группы 19. Тем самым осуществляется остановка тех счетчиков группы 7, в которых произопшо ложное переполнение, и ложное срабатьшание порогового блока 8 от ложных синхросигналов, расположенных в зоне записи на кратном длине цикла расстояни друг от друга, становится невозможным.

Запуск счетчиков группы 7 при выходе на заключительную ГСС (фиг.2) осуществляется аналогичным образом.

Формула изобретения

Устройство для синхронизации внешних блоков памяти, содержащее селектор модулированного сигнала, первый и второй регистры сдвига, группу счетчиков, первый и второй пороговые блоки, элемент НЕ, первую группу элементов И, первый, второй, третий и четвертый счетчики, первый и второй элементы И, триггер и счетный триггер, причем информационный выход модулированного сигнала внешнего блока памяти соединен с входом селектора модулированного сигнала.

0

5

0

5

0

5

0

5

5

выход которого соединен с входами разрешения записи первого и второго регистров сдвига, информационный выход демодулированного сигнала внешнего блока памяти соединен с информационным входом первого регистра сдвига, синхровход которого соединен с синхровходом второго регистра сдвига, с синхровходами счетчиков группы, с синхровходами первого, второго, третьего и четвертого счетчиков и является тактовым входом устройства, информационный вход второго регистра сдвига соединен с шиной единичного потенциала устройства выход последнего разряда первого регистра сдвига соединен с информационными входами счетчиков группы, выходы которых соединены с входами первого порогового блока и соответственно с первыми входами элементов И первой группы, вторые входы которых соединены с выходом элемента НЕ, выход первого порогового блока соединен с входами разрешения счета первого, второго и третьего счетчиков-и является выходом сигнала цикловой отметки устройства, выходы переполнения первого, второго и третьего счетчиков соединены с входами второго порогового блока, выход которого соединен с первым входом первого элемента И и является выходом сигнала начала очередного кодового слова устройства, отличающееся тем, что, с целью повьпиения надежности за счет защиты от ложных срабатываний синхросигналов устройства, в него введены третий регистр сдвига, группа триггеров, вторая группа элементов И, причем синхровход третьего регистра сдвига соединен с тактовым входом устройства, информационный вход третьего регистра сдвига соединен с шиной единичного потенциала устройства, вход разрешения записи третьего регистра сдвига соединен с выходом селектора модулированного сигнала, вход сброса третьего регистра сдвига соединен с входами сброса счетчиков группы, с входом сброса второго регистра сдвига, со счетным входом счетного триггера и с выходом первого порогового блока, вьпсоды третьего регистра сдвига соединены соответственно с единичными г входами триггеров группы, нулевые входы которых соединены соответственно с выходами элементов И первой

группы, выходы триггеров группы соединены соответственно с первыми входами элементов И второй группы, выходы второго регистра сдвига соединены соответственно с вторыми входами элементов И второй группы, выходы которых соединены соответственно с входами разрешения записи счетчиков группы, прямой выход счетного триггера соединен с вторым входом первого элемента И и с входом разрешения yipHMoro счета четвертого счетчика, выход первого элемента И соединен

с входом сброса четвертого счетчика, вход разрепюния обратного счета которого соединен с инверсным выходом счетного триггера и с единичным входом триггера, выход переполнения четвертого счетчика соединен с первым входом второго элемента И, второй вход которого соединен с выходом триггера, нулевой вход которого соединен с выходом второго элемента И и явлйется выходом сигнала конца считываемой информации устройства.

фиг.}

Фиг. 2

Редактор Н.Слободяник

Составитель Е.Тооопов

Техред И.Попович Корректор Е.Сирохман

Заказ 471 /51Тираж 671Подписное

ВНИИПИ Государственйого ко в1тета СССР

по делам изобретений и открытий 113033, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| ПРИЕМНИК ДИСКРЕТНОЙ ИНФОРМАЦИИ С АВТОМАТИЧЕСКИМ СОГЛАСОВАНИЕМ СКОРОСТЕЙ ПЕРЕДАЧИ И ПРИЕМА | 2003 |

|

RU2249919C2 |

| Устройство цикловой синхронизации воспроизведения цифровой информации с носителя магнитной записи | 1989 |

|

SU1599895A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к вычислительной технике, а именно к специализированным вьгаислительным устройствам защиты от опосбок внешней памяти ЦВМ (накопителей на магнитных лентах, дисках и оптической памяти) . Отличительной особенностью устройства является достаточно точное и надежное измерение длины значащей информа1даи в информационной части последнего блока кодового слова записи, оно с высокой степенью надежности позволяет исключить ложные срабатывания порогового блока и фиксировать конец считанный с носителя информации записи. Поставленная цель достигается за счет введения третьего регистра сдвига, группы триггеров, второй группы элементов И. 2 ил. ю СП 4i 1 сд

| Устройство для цикловой синхронизации | 1978 |

|

SU758551A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-30—Публикация

1985-02-01—Подача