1

Изобретение относится к связи и может использоваться в системах с импульсно-кодовой модуляцией, а также в системах передачи информации с временным разделением каналов, для синхронизации блоков сообщений.

Известно устройство для цикловой синхронизации, содержащее регистры сдвига, между выходами и входами которых включен преобразователь кода, к управляющему входу которого подключен выход дешифратора через решающий блок, а также формирователь импульсов 1,

Однако такое устройство имеет срав1штельно большое время вхождения в синхронизм и сравнительно высокую вероятность ложной синхронизации.

Цель изобретения - сокращение времени вхождения в синхронизм и снижение вероятности ложной синхронизации.

Это достигается тем, что в устройство для цикловой синхронизации, содержащее регистры сдвига, между В1;1ходами и входами которых включен преобразователь кода, к управляющему входу которого подключен выход дешифра2

тора через решающий блок, а также формирователь импульсов, введены последовательно соединенные блок памяти и блок сравнения, при этом к другим входам блока сравнения подключены соответственно выходы регистров сдвига и решающего блока, другой вход которого объединен с управляющим входом блока памяти и подключен к одному нз выходов блока сравнения, другой выход которого через формирователь импульсов подключен к управля10ющему входу преобразователя кода, выходы которого подключены к соответствующим входам блока памяти.

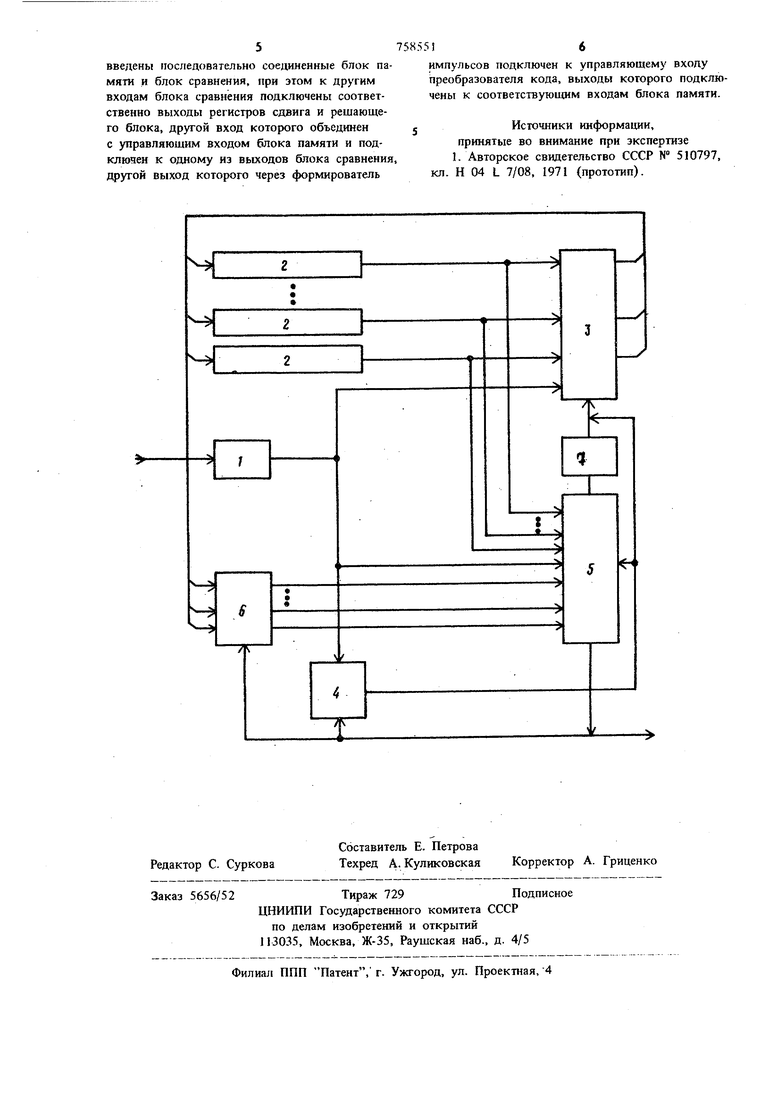

На чертеже приведена структурная электрическая схема предлагаемого устройства.

15

Устройство для цикловой синхронизации содержит дешифратор 1, регистры 2 сдвига, преобразователь 3 кода, решающий блок 4, блок 5 сравнения, блок 6 памяти и формирователь 7.

20

Устройство работает следующим образом.

Допустим, что в начальный момент времени все разряды регистров 2 и блока 6 установлены в нулевое состояние. На вход дешифратора 1 поступает сигнал, в котором присутствует фазируюшая комбинадая, следующая с частотой циклов. На выходе дешифратора 1 в моменты времени, соответствующие последней позиции синхрокомбинадии, формируются импульсы - отклики. На остальных позициях цикла формируются импульсы случайным образом с вероятностью ложного выделения синхрокомбинации из входного потока случайных символов 1Шформацки. Импульсы с выхода дешифратора 1 поступают на вход преобразователя 3, который представляет собой сумматор п-разрядных двоичных чисел, где п - число регистров 2. Первым слагаемым является п-разрядное двоичное число, снимаемое в параллельном коде с выходов регистрс в 2, а вторьгм слагаемым - единица с выхода дешифратора 1. С выхода преобразователя 3 п-разрядное читсло переписывается в параллельном виде в первые разряды регистров 2, и продвигается по регистрам 2 под действием тактовых импульсов, следующих с частотой передачи символов Ш1формации. Число разрядов каждого регистра 2 выбирается равным числу позиций сигнала в цикле, поэтому суммирование откли. ков дешифратора 1 в каждой позиции цикла производится независимо от других позиций цикла.

Таким образом, двоичное число на выходе преобразователя 3 в любой момент времени характеризует количество откликов дешифратора I в соответствующей позиции сигнала за все предшествующие циклы от начала наблюдения. С большой вероятностью число откликов в последней позиции синхрокомбинации становится наибольшим по сравнению с остальными позициями цикла, причем вероятность такого события увеличивается по мере наблюдения. Илздикация позиции, имеющей максимальное число откликов, осуществляется с помощью блока 5 и блока 6 следующим образом. Блок суммирует число на выходе регистров 2 с единицей дешифратора 1 и сравнивает полученную сумму с содержимым блока 6, и если эта сумма превосходит или равна числу, содержащемуся -в блоке 6, то соответствующий сигнал с выхода блока 5 подается на управляющий вход блока бив блок 6 переписывается значение этой суммы с выхода преобразователя 3. Таким образом, в блоке 6 содержится наибольшее из чисел, записанних в ячейках регистров за предыдущий илкл, а сигнал на выходе блока 5 появляется в той позиции цикла, где количество откликов дешифратора 1 максимально

Для того, чтобы исключить переполнение разрядной сетки двоишых чисел при дальнейшем накоплении откликов де1иифратора 1, используется второй выход блока 5, на котором формируется импульс переполнения, если сумiH

ма чисел на входах блока 5 равна 2. Импульс переполнения поступает на формирователь 7, на выходе которого образуется единичный скачок напряжения длительностью в один 1Ц1кл. Этот сигнал воздействует па преобразователь 3 таким образом, что из полученной суммы, образованной входными числами, вычитается единица в течение всего последующего цикла за исключением тех случаев, когда сумма равна нулю. В дальнейшем, значение максимального числа фиксируется на уровне 2 - 1, а числа остальных позиций цикла уменьшаются со скоростью, определяемой соотношением вероятностей правильного обнаружения и ложного

вьщеления синхрокомбинации. Наступает стационарный режим, при котором число, соответствующее последней позиции синхросигнала, равно 2 - 1, а число остальных позиций флуктуируют около некоторого значения вблизи нуля. В случае, если число одной го остальных позиций цикла достигает уровня 2-1, вероятность такой ситуации уменьшается с помощью соответствующего увеличения числа регистров 2, т.е. увеличением разрядности чисел.

Решающий блок 4 анализирует сигналы, поступающие с выходов блока 5 и дешифратора 1. В случае значительного уменьшения вероятности правильного обнаружения синхрокомбинации (например, при замираниях в канале связи)

решающий блок 4 воздействует на преобразователь 3 и- блок 5, при этом производится последовательное (один раз в несколько циклов) уменьшение чисел, записываемых в регистры 2 с одновременным обновлением содержащегося

в блоке 6 максимального числа. Скорость уменьшения чисел выбирается исходя из конкретных условий работы. Так, если после перерыва связи новый сеанс связи начинается с новой фазы цикловой разметки, то желательно, чтобы к началу сеанса связи регистры .2 были в нулевом состоянии. При этом время определения фазы новой цикловой разметки минимально.

Предлагаемое устройство обеспечивает высокую вероятность правильного фазирования

при значительном сокращении времени установления синхронизма.

Ф о р мула изобретения

Устройство для цикловой синхронизации, содержащее регистры сдвига, между выходами и входами которых- включен преобразователь кода, к управляющему входу которого подключен выход дешифратора через ре1нающий блок, а также формирователь импульсов, о тличающееся тем, что, с целью сокращения времени вхождения в синхронизм и снижения вероятности ложной синхрк1низации 5 введены последовательно соединенные блок памяти и блок сравнения, при этом к другим входам блока сравнения подключены соответственно выходы регистров сдвига и решающего блока, другой вход которого объединен с )шравляющим входом блока памяти и подключен к одному из выходов блока сравнения другой выход которого через формирователь ) импульсов подключен к управляющему входу преобразователя кода, выходы которого подключены к соответствующим входам блока памяти. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 510797, кл. Н 04 L 7/08, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Устройство для синхронизации по циклам | 1983 |

|

SU1172052A1 |

S

s

Авторы

Даты

1980-08-23—Публикация

1978-04-03—Подача