блоков, на которое задерживается символ с данным номером, плюс ячейка для считывания. После каждого очередного цикла записи-считывания, равного периоду блока, освободившиеИзобретение относится к приборостроению, а именно к устройствам для задержки и преобразования инфорнации.

Цель Изобретения - повышение надежности работы за счет уменьшения объема памяти оперативного запоминающего устройства.

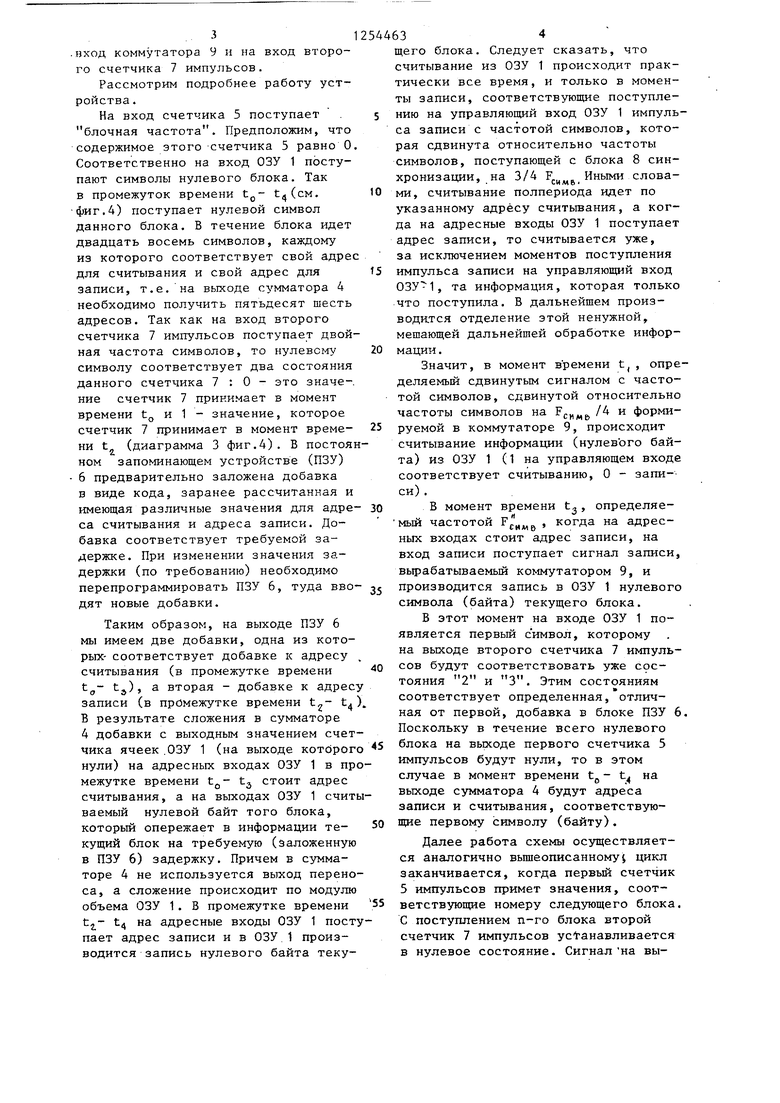

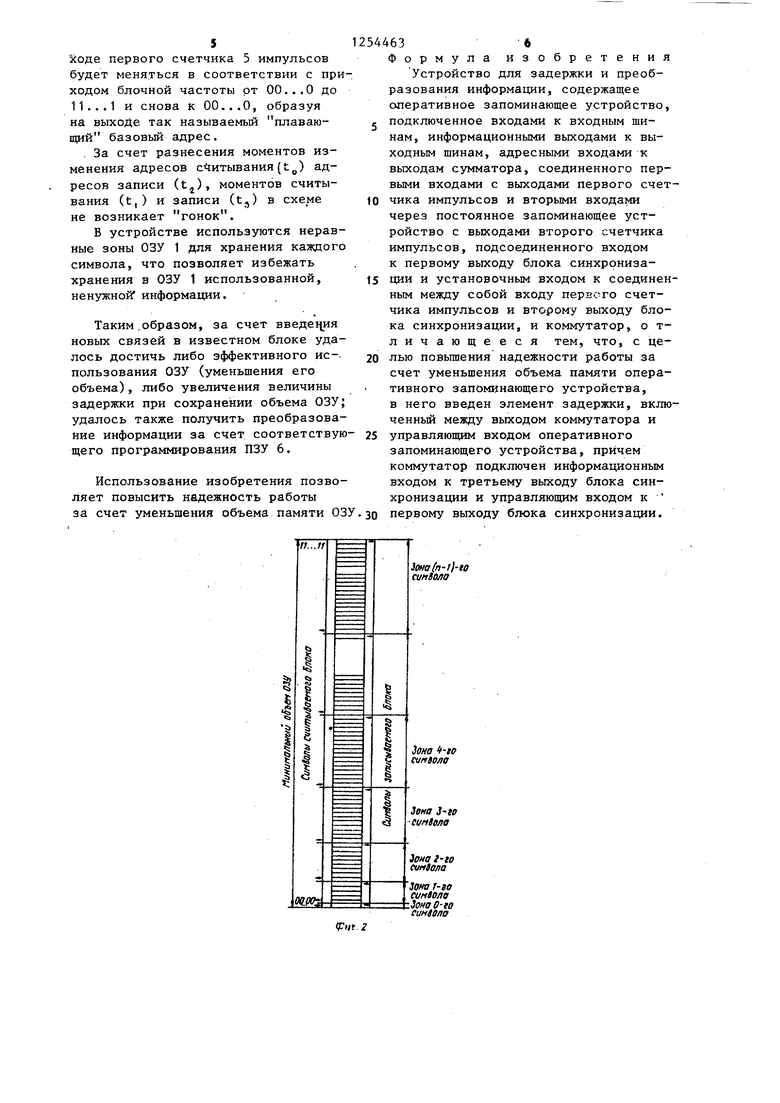

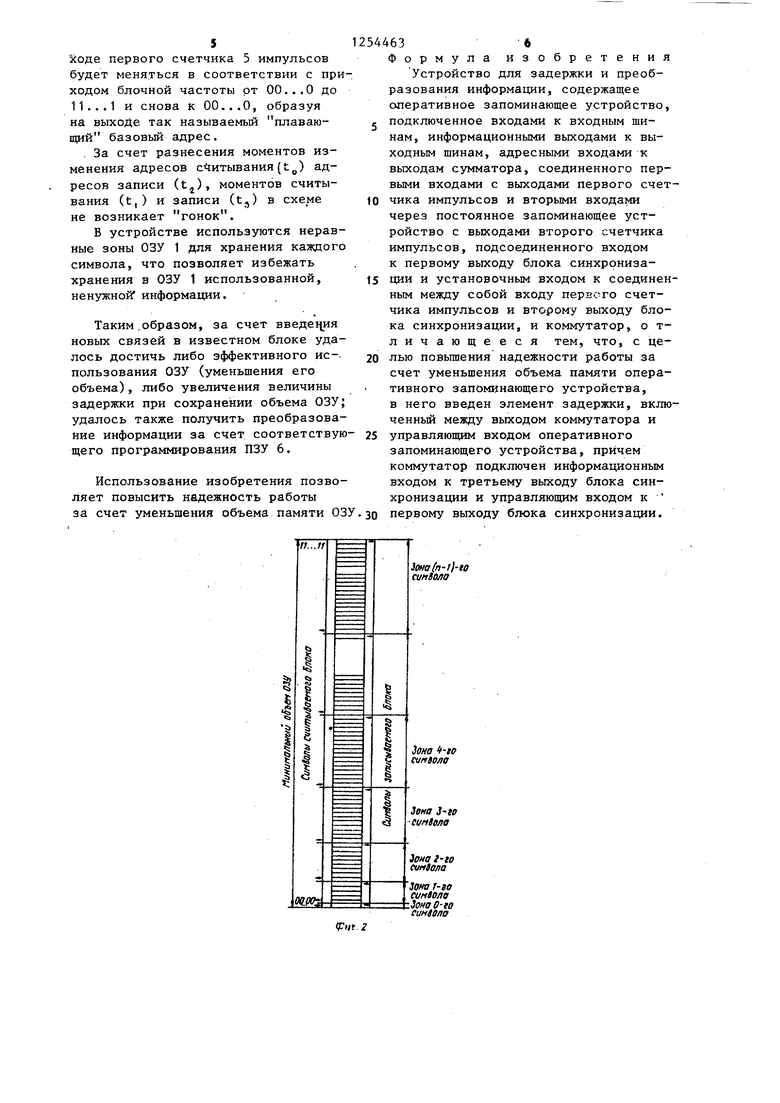

На фиг.1 приведена функциональная схема устройства; на фиг.2 - распределение ячеек оперативного запоминающего устройства (ОЗУ) в устройстве; на фиг.З - распределение зон символов блока данных в ОЗУ на фиг.4 - временные диаграммы работы устройства.

Устройство для задержки и преобразования информации содержит оперативное запоминающее устройство 1, подключенное входами к входным щи- нам 2, информационными выходами к выходным шинам 3, адресными входами к выходам сумматора 4, соединенного первыми входами с выходами первого счетчика 5 импульсов и вторыми входами через постоянное запоминающее устройство 6 с выходами второго счетчика 7 импульсов, подсоединенного входом к первому выходу блока 8 синхронизации и установочным вхо;Е1ом к соединенным между собой входу первого счетчика 5 импульсов и второму выходу блока 8 синхронизации, и коммутатор 9. Кроме того, устройство для задержки и преобразования информации содержит элемент 10 задержки, включенный между выходом коммутатора 9 и управляющим входом ОЗУ 1, причем коммутатор 9 подключен инфор ацион- ным входом к третьему выходу блока 8 синхронизации и управляющим входом к первому выходу блока 8 синхронизации.

Устройство работает следующим образом.

ся ячейки переходят из начала одной зоны в конец другой, происходит смещение по всему объему ОЗУ 1 со скоростью одна ячейка за период блока. 4 ил.

Обрабатываемая информация поступает с входных шин 2 на оперативное запоминающее устройство 1. С его выхода информация поступает на вы5 ходные шины 3.

Распределение ячеек ОЗУ 1 для устройства представлено на фиг.2. Здесь для каждого номера символа в блоке выделена динамическая зона

o с количеством ячеек, равным числу блоков, на которое задерживается символ с данным номером, плюс ячейка для считывания. В течение периода блока ячейки в начале каждой зоны

5 освобождаются, так как символы, записанные в них, считываются из ОЗУ 1. Запись же символов поступающего блока осуществляется в последние ячейки соответствующих зон.

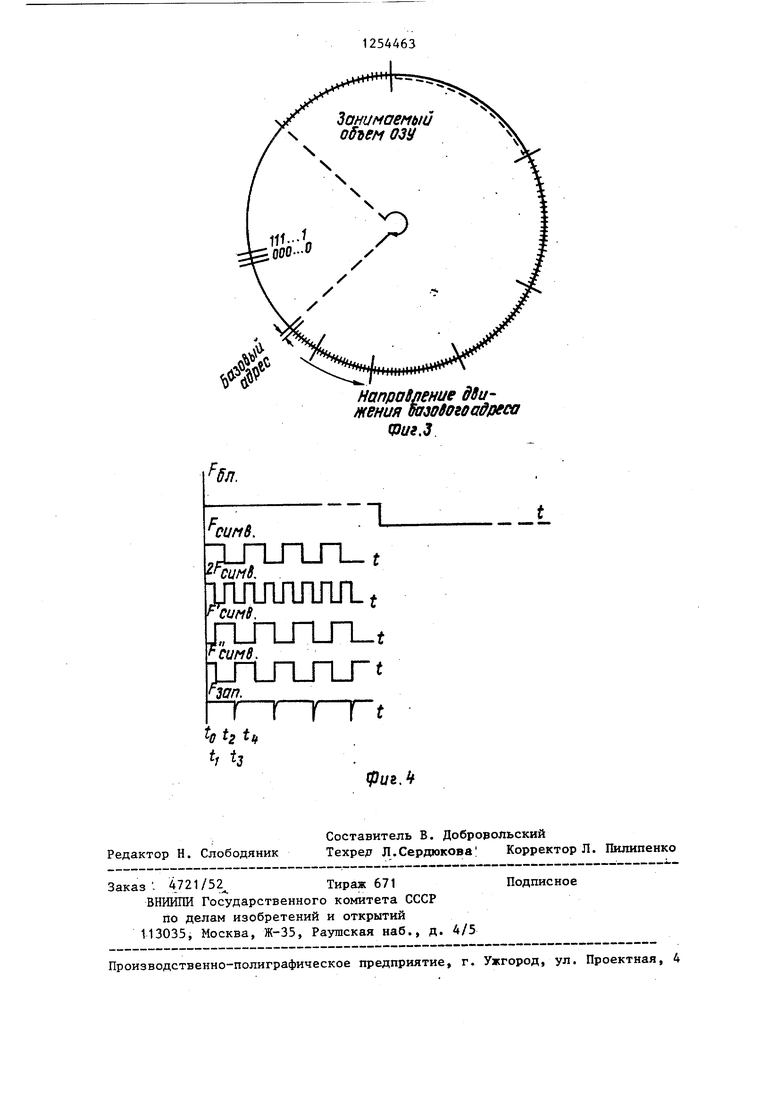

0 Таким образом, после каждого очередного цикла записи-считывания, равного периоду блока, освободившиеся ячейки переходят из начала одной зоны в конец другой, т.е. карти5 на, представленная на фиг.2, будет динамической, будет смещаться по всему объему ОЗУ 1 со скоростью одна ячейка за период блока (характер смещения показан на фиг.З).

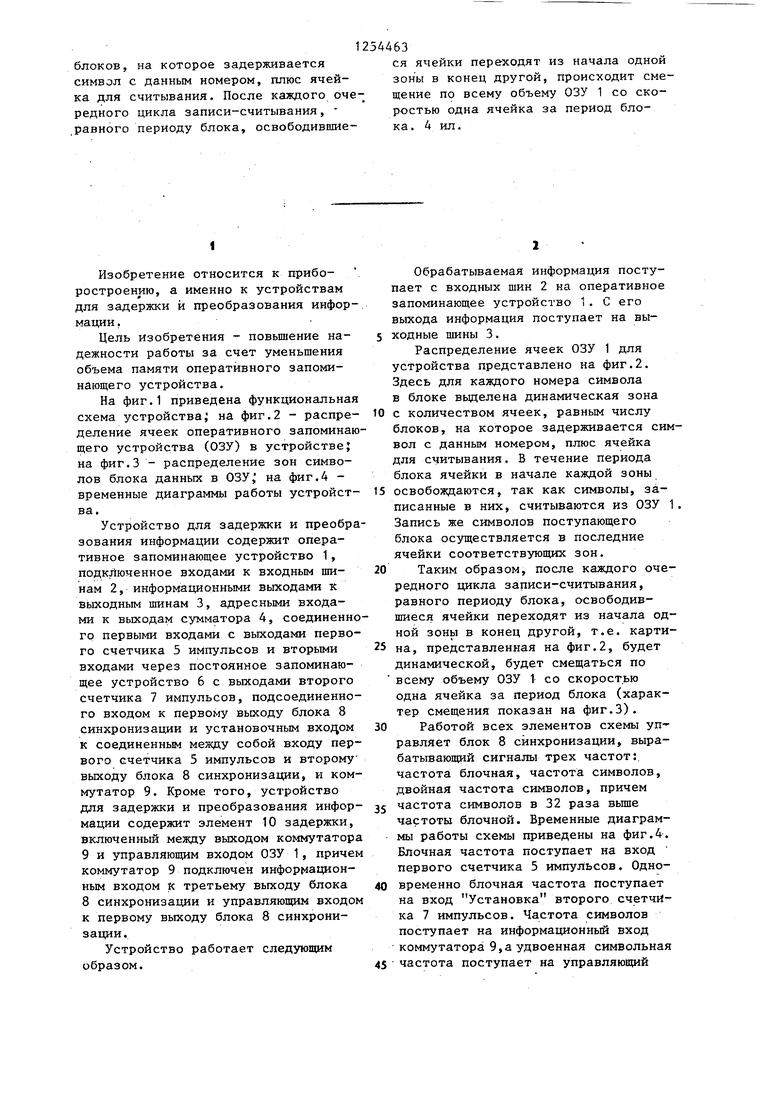

0 Работой всех элементов схемы уп равляет блок 8 синхронизации, выра- батьгаающий сигналы трех частот:, частота блочная, частота символов, двойная частота символов, причем

5 частота символов в 32 раза вьш1е

частоты блочной. Временные диаграм мы работы схемы приведены на фиг.4.

Блочная частота поступает на вход

первого счетчика 5 импульсов. Одно0 временно блочная частота поступает на вход Установка второго счетчика 7 импульсов. Частота символов поступает на информационный вход коммутатора 9,а удвоенная символьная

5 частота поступает на управляющий

.вход коммутатора 9 н на вход второго счетчика 7 импульсов.

Рассмотрим подробнее работу устройства .

На вход счетчика 5 поступает . блочная частота. Предположим, что содержимое этого счетчика 5 равно 0. Соответственно на вход ОЗУ 1 поступают символы нулевого блока. Так в промежуток времени .

фиг.4) поступает нулевой символ данного блока, В течение блока идет двадцать восемь символов, каждому из которого соответствует свой адрес для считывания и свой адрес для записи, т.е. на выходе сумматора 4 необходимо получить пятьдесят шесть адресов. Так как на вход второго счетчика 7 импульсов поступает двойная частота символов, то нулевому символу соответствует два состояния данного счетчика 7:0- это значе-. ние счетчик 7 принимает в момент времени t и 1 - значение, которое счетчик 7 принимает в момент време- ни t (диаграмма 3 фиг.4). В постоянном запоминающем устройстве (ПЗУ) 6 предварительно заложена добавка в виде кода, заранее рассчитанная и имеющая различные значения для адре- са считывания и адреса записи. Добавка соответствует требуемой задержке. При изменении значения задержки (по требованию) необходимо перепрограммировать ПЗУ 6, туда вво- дят новые добавки.

Таким образом, на выходе ПЗУ 6 мы имеем две добавки, одна из которых- соответствует добавке к адресу считывания (в промежутке времени tg- tj), а вторая - добавке к адресу записи (в промежутке времени ty- t В результате сложения в сумматоре 4 добавки с выходным значением счетчика ячеек .ОЗУ 1 (на выходе которого нули) на адресных входах ОЗУ 1 в промежутке времени t стоит адрес считывания, а на выходах ОЗУ 1 считываемый нулевой байт того блока, который опережает в информации те- кущий блок на требуемую (заложенную в ПЗУ 6) задержку. Причем в сумматоре 4 не используется выход переноса, а сложение происходит по модулю объема ОЗУ 1. В промежутке времени t на адресные входы ОЗУ 1 поступает адрес записи и в ОЗУ 1 производится запись нулевого байта текущего блока. Следует сказать, что считывание из ОЗУ 1 происходит практически все время, и только в моменты записи, соответствующие поступлению на управляющий вход ОЗУ 1 импульса записи с частотой символов, которая сдвинута относительно частоты символов, поступающей с блока 8 синхронизации, на 3/4 .„..„ Иными словаLH Mb

ми, считывание полпериода идет по указанному адресу считьшания, а когда на адресные входы ОЗУ 1 поступает адрес записи, то считывается уже, за исключением моментов поступления импульса записи на управляющий вход ОЗУ 1, та информация, которая только что поступила. В дальнейшем произ- водатся отделение зтой ненужной, мешающей дальнейшей обработке информации .

Значит, в момент времени t , определяемый сдвинутым сигналом с частотой символов, сдвинутой относительно частоты символов на и формируемой в коммутаторе 9, происходит считывание информации (нулевого байта) из ОЗУ 1 (1 на управляющем входе соответствует считыванию, О - записи) .

В момент времени t, определяе- мьй частотой F , когда на адресных входах стоит адрес записи, на вход записи поступает сигнал записи, вырабатываемый коммутатором 9, и производится запись в ОЗУ 1 нулевого символа (байта) текущего блока.

В этот момент на входе ОЗУ 1 появляется первый с имвол, которому на выходе второго счетчика 7 импульсов будут соответствовать уже состояния 2 и 3. Этим состояниям соответствует определенная, отличная от первой, добавка в блоке ПЗУ 6 Поскольку в течение всего нулевого блока на выходе первого счетчика 5 импульсов будут нули, то в этом случае в момент времени t на выходе сумматора 4 будут адреса записи и считывания, соответствующие первому символу (байту).

Далее работа схемы осуществляется аналогично вьшеописанному цикл заканчивается, когда первый счетчик 5 импульсов примет значения, соответствующие номеру следующего блока. С поступлением п-го блока второй счетчик 7 импульсов yctaнaвливaeтcя в нулевое состояние. Сигнал на выходе первого счетчика 5 импульсов будет меняться в соответствии с приходом блочной частоты от 00...О до 11... 1 и снова к 00...О, образуя на выходе так называемый плавающий базовый адрес.

. За счет разнесения моментов изменения адресов с 1итывания {t д) адресов записи (tj), моментов считывания (t, ) и записи (t,) в не возникает гонок.

В устройстве используются неравные зоны ОЗУ 1 для хранения каждого символа, что позволяет избежать хранения в ОЗУ 1 использованной, ненужнокГ информации.

Таким .образом, за счет введения новых связей в известном блоке удалось достичь либо эффективного ис-. пользования ОЗУ (уменьшения его объема), либо увеличения величины задержки при сохранении объема ОЗУ; удалось также получить преобразование информации за счет соответствую щего программирования ПЗУ 6.

Использование изобретения позволяет повысить надежность работы за счет уменьшения объема памяти ОЗУ.

.

Формула изобретения

Устройство для задержки и преобразования информации, содержащее оперативное запоминающее устройство, J подключенное входами к входным щи- нам, информационными выходами к выходным шинам, адресными входами к выходам сумматора, соединенного первыми входами с выходами первого счет10 чика импульсов и вторыми входами через постоянное запоминающее устройство с выходами второго счетчика импульсов, подсоединенного входом к первому выходу блока синхррниза15 ции и установочным входом к соединенным между собой входу первого счетчика импульсов и второму выходу блока синхронизации, и коммутатор, о т- личающееся тем, что, с це20 лью повьшения надежности работы за счет уменьшения объема памяти оперативного запоминающего устройства, в него введен элемент задержки, вклю- ченньй между вьпсодом коммутатора и 25 управляющим входом оперативного запоминающего устройства, причем коммутатор подключен информационным входом к третьему выходу блока синхронизации и управляющим входом к

30 первому выходу блока синхронизации.

Напрабление дди- /нения оазоВого адреса

Фи1,3

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Цифровое устройство доплеровской фильтрации | 1990 |

|

SU1830496A1 |

| СИСТЕМА СВЯЗИ | 1996 |

|

RU2116001C1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1985 |

|

SU1840079A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

Изобретение относится к приборостроению и позволяет повысить надежность работы за счет уменьшения объема памяти оперативного запоминающего устройства (ОЗУ). Устройство содержит ОЗУ 1, сумматор 4, с-четчи- ки 5 и 7 импульсов, постоянное запоминающее устройстЁо 6, блок 8 синхронизации, коммутатор 9 и элемент 10 задержки. Введением новых элементе и образованием новых связей между элементами устройства удалось достичь того, что для каждого номера символа в ОЗУ 1 выделена динамическая зона с количеством ячеек, равным числу с s (Л оиеыбаемые самболы Запись считывом/ rWOTW&WWf COfttOffU 3 sanueu fMaSKucvuffi пния чтныц Ar. дауг./

CUflB.

. Щ1Г1ПШШ.(

(

f CUMB.

гчпп

г г г I t

t tlf

1 3.

иг,

Редактор Н. Слободяник

Составитель В, Добровольский

Техред Л.Сердюкова Корректор Л. Пилипенко

Заказ 4721/52 Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий V13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Подписное

| Устройство для задержки сигналов | 1978 |

|

SU824191A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ефимов В.И | |||

| и др | |||

| Цифровое кодирование при записи и воспроизведении звука | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1986-08-30—Публикация

1985-01-04—Подача