ел

СП

1

со

Изобретение относится к вычислительной технике и может быть использовано для суммирования последовательных кодов золотой пропорции или последовательных кодов Фибоначчи,начиная со старших разрядов, а также для преобразования последовательных .кодов золотой пропорции в последовательный код Фибоначчи,

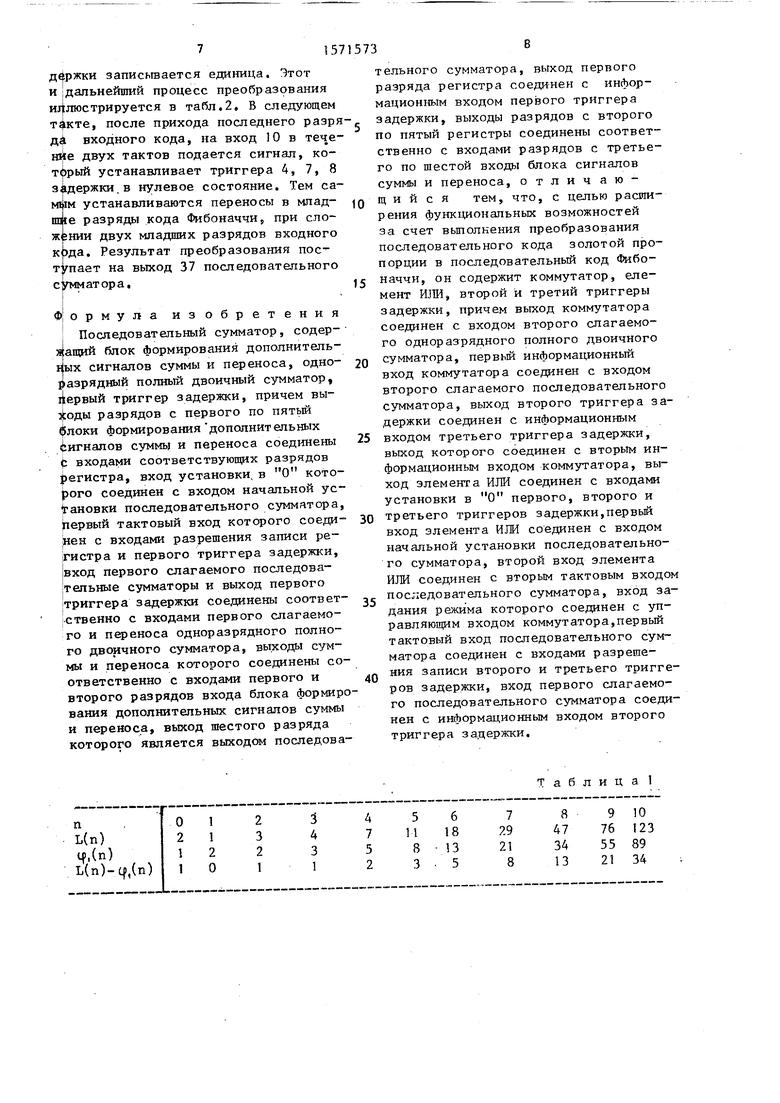

Цель изобретения - расширение функциональных возможностей за счет выполнения преобразования последовательности кода золотой пропорции в последовательный код Фибоначчи На чертеже приведена схема послеовательного сумматора.

Последовательный сумматор содержит регистр 1 , блок 2 формирования дополнительных сигналов суммы и пееноса. одноразрядный полный двоичА

яый сумматор 33 первый триггер 4 за- Держки, коммутатор 5, элемент ИЛИ 69 ретий 7 и второй 8 триггеры задержки, вход 9 начальной установки пос- Йедовательного сумматора, второй

Тактовый вход 10 последовательного

О при п

q, (n) I 1 при п

q,(n--l)

сумматора, вход 11 первого слагаемого последовательного сумматора, вход 12 второго слагаемого последовательного сумматора, первый тактовый вход 13 последовательного сумматора, вход 14 задания режима последовательного сумматора, входы 15-20 разрядов с первого по шестой входа блока 2 Формирования дополнительных сигналов суммы и переноса соответственно, выходы 21-26 разрядов с первого по шестой блока 2 формирования дополнительных сигналов суммы и переноса соответственно, входы 27 - 31 и выходы 32 - 36 разрядов с первого по пятый регистра 1 соответственно, выход 37 последовательного сумматора.

Сущность и физическая возможность преобразования последовательного кода золотой пропорции в последовательный код Фибоначчи, начиная со старших разрядов заключается в следующем.

Ряд чисел Фибоначчи образуется согласно выражения

(1)

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| Преобразователь кодов | 1988 |

|

SU1658390A1 |

| Устройство для деления | 1988 |

|

SU1552174A1 |

| Арифметическое устройство | 1985 |

|

SU1305662A2 |

| Последовательное множительное устройство | 1984 |

|

SU1233138A1 |

| Устройство для умножения | 1987 |

|

SU1444751A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| Параллельный сумматор кодов фибоначчи | 1984 |

|

SU1180880A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения специализированных вычислительных устройств. Цель изобретения - расширение функциональных возможностей за счет выполнения преобразования последовательного кода золотой пропорции в последовательный код Фибоначчи. Последовательный сумматор содержит регистр 1, блок 2 формирования дополнительных сигналов суммы и переноса, одноразрядный полный двоичный сумматор 3, первый триггер 4 задержки, коммутатор 5, элемент ИЛИ 6,третий триггер 7 задержки, второй триггер 8 задержки, вход 9 начальной установки, второй тактовый вход 10, вход 11 первого слагаемого, вход 12 второго слагаемого, первый тактовый вход 13, вход 14 задания режима и выход 37 последовательного сумматора. 1 ил., 2 табл.

i/i имеет вид 1, 1, 2, 3, 5, 8 s J3S 2l,..o Существует ряд чисел Люка, в ротором каждое число также равно сум

0при п 0;

2 при п 0;

1при п 1;

L(n-l )+L(n-2) при ,

3 9 4, 7, 11, 18,

связь степеней зочислами Люка для

L(n) Об + - ui - d-n

где mi - основание системы счисления з олот ой про пор ции;

ОС

1,618.,

1 + 5

2

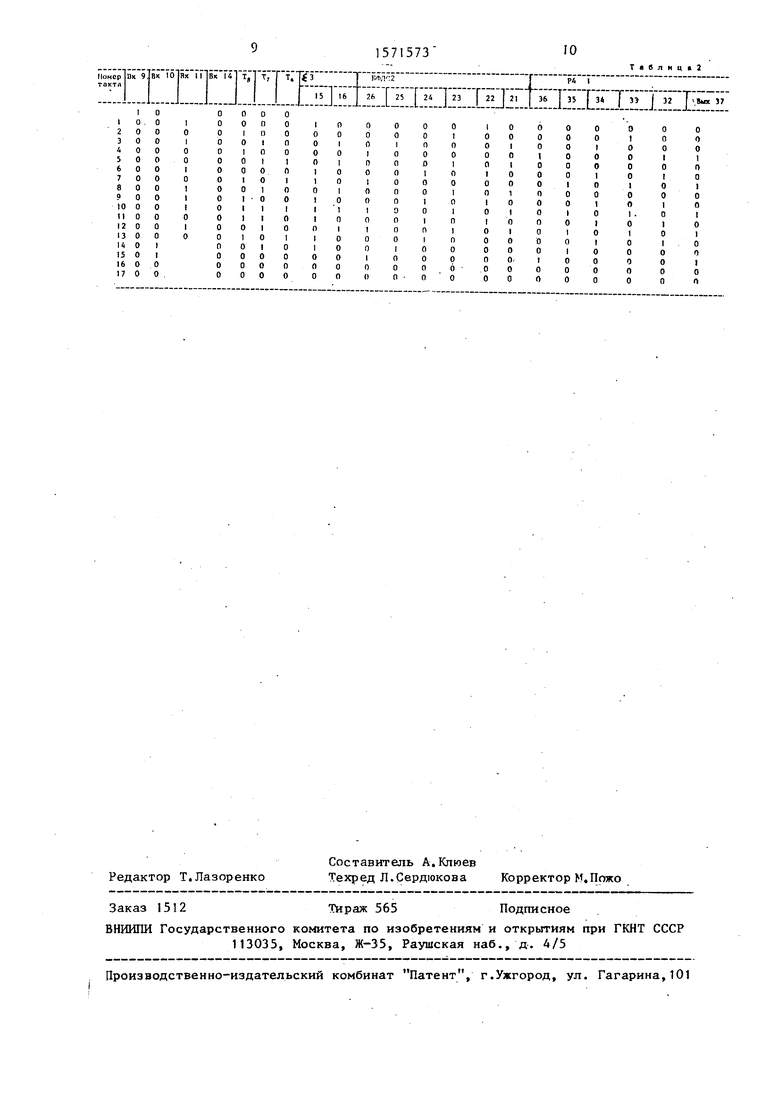

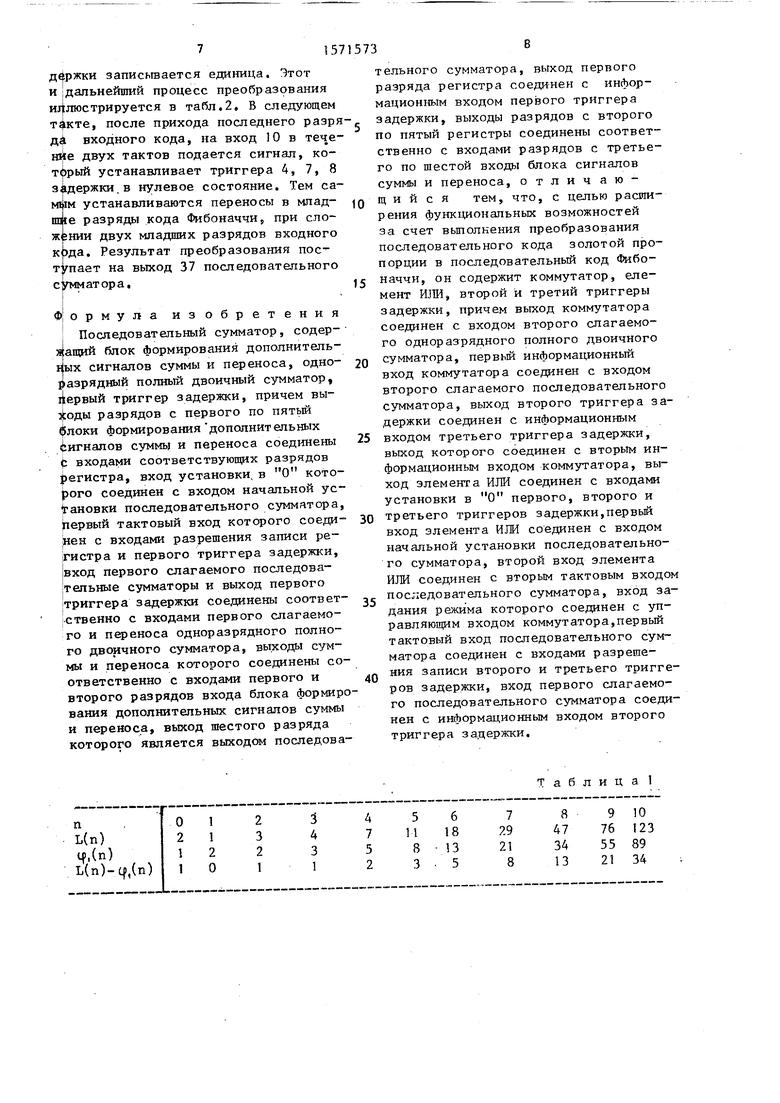

п - номер разряда кода. Произведем вычитание чисел 1чи (f, (n) из чисел Люка L(n). тат представлен в табл,1.

ме двух предыдущих, однако начальное условие ряда есть 2 и 1. Ряд чисел Люка образуется согласно выражения

(2)

положительных п, которая выражается в следующем:

для четных п;

для нечетных п,( 3)

Из табл,1 видно, что начиная с п 2 результат вычитания является рядом чисел Фибоначчи,

Таким образом, при преобразовании кода золотой пропорции в 1-код Фибоначчи необходимо сложить два кода, первый код является кодом Фибоначчи, содержащим единицы в тех же разрядах,

51

что и исходный код золотой пропорции второй код является тем же кодом, сдвинутым на два разряда в сторону младших ра рядов.

При этом, учитывая, что разряды с четными номерами кода расположены через один разряд друг от друга, а разряды с нечетными номерами расположены через один разряд друг от друга, общие суммы для четных n, a также для нечетных n не превышают единицы. Это следует из того свойства кодов золотой пропорции, что при минимальной форме кода вес 1-го разряда больше любого кода, записанного в младших разрядах. Учитывая,что в коде золотой пропорции могут встречаться единицы как в четных,так и нечетных номерах разрядов, общая погрешность преобразования кода золотой пропорции с положительными значениями n будет равна разности суммы Х для нечетных номеров разрядов и суммы четных номеров разрядов. Для преобразования последовательных кодов золотой пропорции в последовательный код Фибоначчи необходимо сложить, начиная со старших разрядов, последовательный код золотой пропорции с этим же кодом, задержанным на два разряда по правилам сложения кодов Фибоначчи, а сумма единиц с весами разрядов ч.-п будет меньше единицы и в преобразовании может не участвовать.

Рассмотрим работу последовательного сумматора.

При выполнении операции сложения на вход 14 последовательного сумматора подается единичный потенциал, который подключает вход 12 второго слагаемого последовательного сумматора к входу второго слагаемого одноразрядного сумматора 3. Последовательный сумматор производит сложение кодов Фибоначчи (золотой пропорции) в соответствии с алгоритмом, изложенным в прототипе, I

При выполнении операции преобразования последовательного кода золотой пропорции в последовательный код Фибоначчи на вход 14 последовательного сумматора поступает нулевой сигнал, который подключает выход триггера 7 задержки к входу второго слагаемого одноразрядного сумматора 3. На вход 9 начальной установки поступает импульс, который устанав71573

ливает регистр 1 и триггеры 4, 7, 8

задержки в нулевое состояние. Затем на вход 1 поступает последователь ный код золотой пропорции, начиная со старших разрядов.

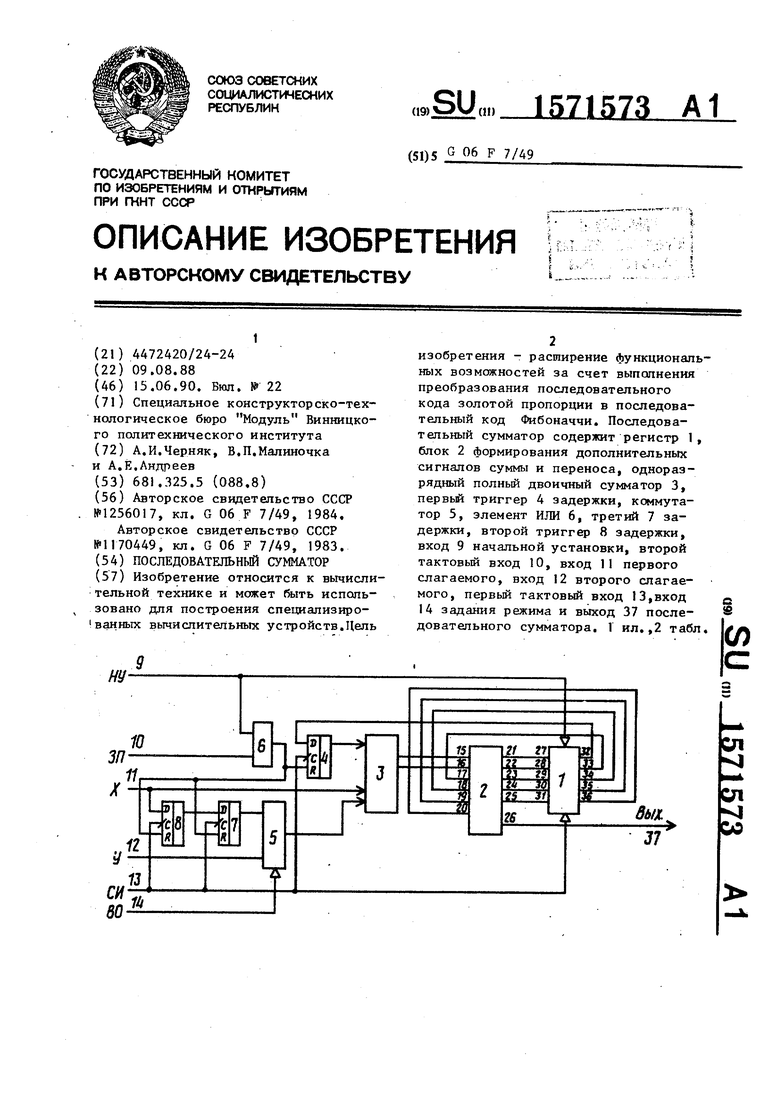

Рассмотрим работу последовательного сумматора при преобразовании кода числа 497, 821, представленно Q го в коде золотой пропорции (см. т аблицу 2).

В первый момент времени на вход 11 поступает значение старшего разряда, в данном случае единица.Одно 5 разрядный сумматор 3 производит сложение единицы, присутствующей на его первом входе, с нулями, присутствующими на втором входе и входе переноса. На выходе суммы одноразрядного сумматора 3 получается единичный сигнал, а на выходе переноса - нулевой. На выходах 26-21 блока 2 формирования дополнительных сигналов суммы и переноса формируется код 000010, По переднему фронту синхроимпульса в регистр 1 записывается код 00010, в триггер 4 задержки записывается нуль, а в триггер 8 задержки записывается единица. На вход 11 пос20

25

30

тупает нулевое значение следующего

разряда входного кода. Одноразрядный сумматор 3 производит сложение нулей, присутствующих на всех его входах и на выходах получаются нулевые сигналы. На выходах блока 2 Формируется код 00010. По переднему фронту синхроимпульса в регистр 1 записывается код 00100, в триггер 4 задержки записывается нуль, в триггер 7 задержки записывается единица, в триггер 8 записывается нуль. На вход 11 поступает значение третьего разряда кода, в данном случае единица„ Через коммутатор 5 на второй вход одноразрядного сумматора 3 поступает единица с выхода триггера 7 задержки. Одно-разрядный сумматор 3 производит сложение единиц, присутствующих на первом и втором входах, с нулем на входе переноса. На выходе суммы одноразрядного сумматора Аормируется нулевой сигнал, на выходе переноса формируется единичный сигнал. На выходах блока 2 формируется код 010001. С приходом переднего фронта синхроимпульса в регистр 1 записывается код 10001, в триггер 4 задержки записывается код нуль, в триггер 7 задержки записывается нуль, в триггер 8 задёржки записывается единица. Этот и дальнейший процесс преобразования иллюстрируется в табл.2. В следующем , после прихода последнего раэря дА входного кода, на вход 10 в тече- Hijie двух тактов подается сигнал, ко- устанавливает триггера 4, 7, 8 задержки.в нулевое состояние. Тем самим устанавливаются переносы в млад- шне разряды кода Фибоначчи, при сложении двух младших разрядов входного кода. Результат преобразования поступает на выход 37 последовательного сумматора,

Ф, о р м у л а изобретения Последовательный сумматор, содержащий блок формирования дополнительных сигналов суммы и переноса, одно- разрядный полный двоичный сумматор, ервый триггер задержки, причем выходы разрядов с первого по пятый флоки формирования дополнительных Сигналов суммы и переноса соединены Ј входами соответствующих разрядов регистра, вход установки, в О которого соединен с входом начальной установки последовательного сумматора, Первый тактовый вход которого соеди- нен с входами разрешения записи регистра и первого триггера задержки, вход первого слагаемого последовательные сумматоры и выход первого триггера задержки соединены соответ- ственно с входами первого слагаемого и переноса одноразрядного полного двоичного сумматора, выходы суммы и переноса которого соединены соответственно с входами первого и второго разрядов входа блока формирования дополнительных сигналов суммы и переноса, выход шестого разряда которого является выходом последовательного сумматора, выход первого разряда регистра соединен с информационным входом первого триггера задержки, выходы разрядов с второго по пятый регистры соединены соответственно с входами разрядов с третьего по шестой входы блока сигналов суммы и переноса, отличающийся тем, что, с целью расширения функциональных возможностей за счет выполнения преобразования последовательного кода золотой пропорции в последовательный код Фибоначчи, он содержит коммутатор, еле- мент ИЛИ, второй и третий триггеры задержки, причем выход коммутатора соединен с входом второго слагаемого одноразрядного полного двоичного сумматора, первый информационный вход коммутатора соединен с входом второго слагаемого последовательного сумматора, выход второго триггера задержки соединен с информационным входом третьего триггера задержки, выход которого соединен с вторым информационным входом коммутатора, выход элемента ИЛИ соединен с входами установки в О первого, второго и третьего триггеров задержки,первьй вход элемента ИЛИ соединен с входом начальной установки последовательного сумматора, второй вход элемента ИЛИ соединен с вторым тактовым входо последовательного сумматора, вход задания режима которого соединен с управляющим входом коммутатора,первый тактовый вход последовательного сумматора соединен с входами разрешения записи второго и третьего триггеров задержки, вход первого слагаемого последовательного сумматора соединен с информационным входом второго триггера задержки.

т а б л и ц а 1

| Устройство для сложения в избыточной системе счисления | 1984 |

|

SU1256017A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1983 |

|

SU1170449A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-15—Публикация

1988-08-09—Подача