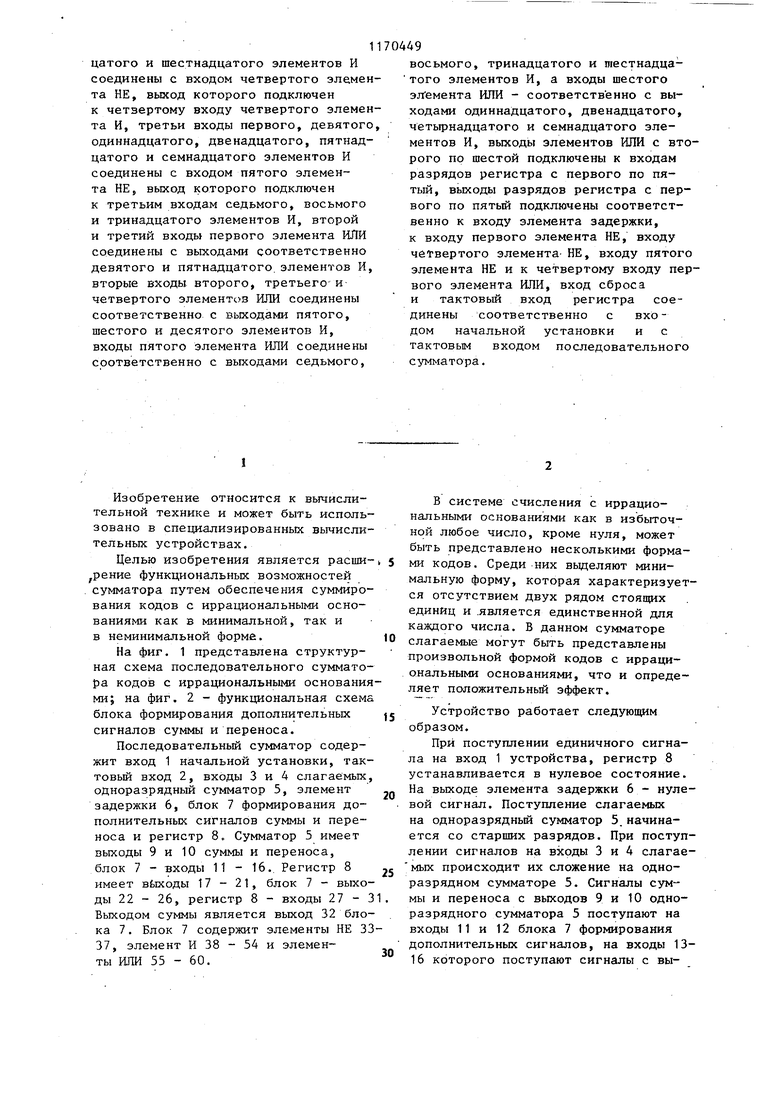

цатого и шестнадцатого элементов И соединены с входом четвертого элемента НЕ, выход которого подключен к четвертому входу четвертого элемента И, третьи входы первого, девятого одиннадцатого, двенадцатого, пятнадцатого и семнадцатого элементов И соединены с входом пятого элемента НЕ, выход которого подключен к третьим входам седьмого, восьмого и тринадцатого элементов И, второй и третий входы первого элемента ИЛИ соединены с выходами соответственно девятого и пятнадцатого, элементов И, вторые входы второго, третьего и четвертого элементов ИЛИ соединены соответственно с выходами пятого, шестого и десятого элементов И, входы пятого элемента ИЛИ соединены соответственно с выходами седьмого,

0449

восьмого, тринадцатого и шестнадцатого элементов И, а входы шестого элемента ИЛИ - соответственно с выходами одиннадцатого, двенадцатого, четырнадцатого и семнадцатого элементов И, выходы элементов ИЛИ с второго по шестой подключены к входам разрядов регистра с первого по пятый, выходы разрядов регистра с первого по пятый подключены соответственно к входу элемента задержки, к входу первого элемента НЕ, входу четвертого элемента- НЕ, входу пятого элемента НЕ и к четвертому входу первого элемента ИЛИ, вход сброса и тактовый вход регистра соединены соответственно с входом начальной установки и с тактовым входом последовательного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР | 1991 |

|

RU2006914C1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Сумматор кодов с иррациональным основанием | 1982 |

|

SU1083182A1 |

| Последовательный сумматор | 1988 |

|

SU1571573A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Трехвходовой параллельный сумматор | 1983 |

|

SU1136150A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

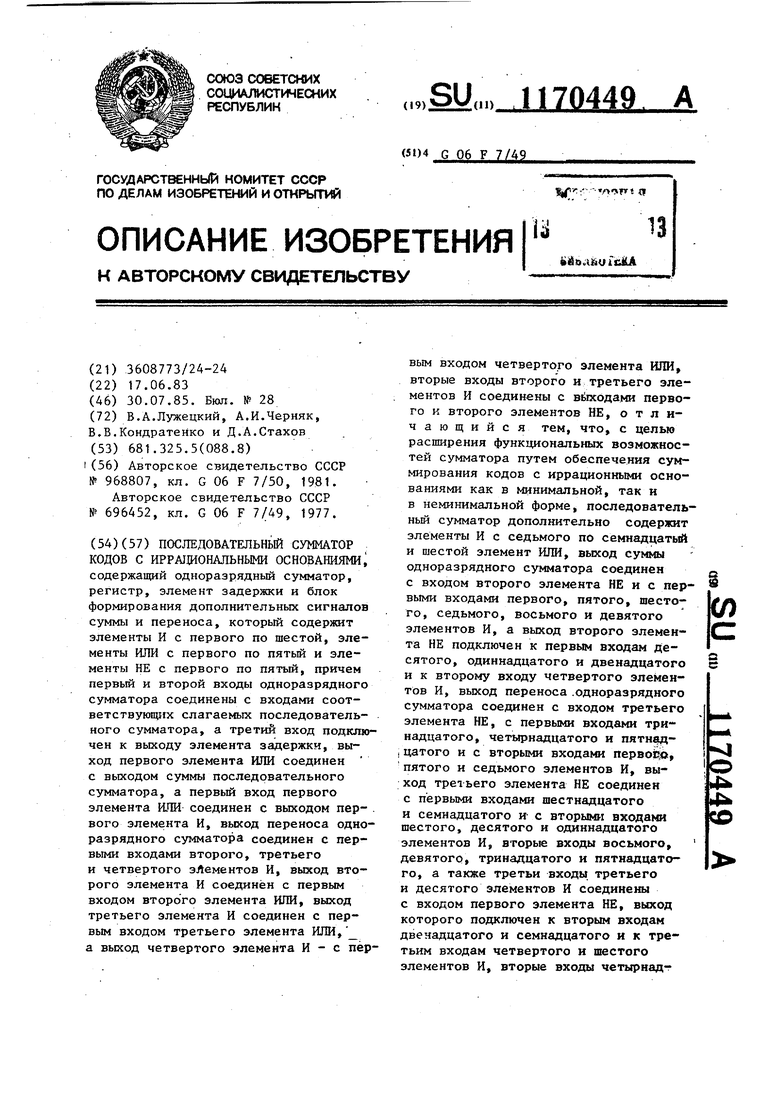

ПОСЛЕДОВАТЕЛЬНЬЙ СУММАТОР КОДОВ С ИРРАЦИОНАЛЬНЫМИ ОСНОВАНИЯМИ содержащий одноразрядный сумматор, регистр, элемент задержки и блок формирования дополнительных сигналов суммы и переноса, который содержит элементы И с первого по шестой, элементы ИЛИ с первого по пятьй и элементы НЕ с первого по пятый, причем первый и второй входы одноразрядного сумматора соединены с входами соответствующих слагаемых последовательного сумматора, а третий вход подключен к выходу элемента задержки, выход первого элемента ИЛИ соединен с выходом суммы последовательного сумматора, а первый вход первого элемента ИЛИ соединен с выходом пер- . вого элемента И, выход переноса одноразрядного сумматора соединен с первыми входами второго, третьего и четвертого элементов И, выход второго элемента И соединён с первым входом второго элемента ИЛИ, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, а выход четвертого элемента И - с первым входом четвертого элемента ИЛИ, вторые входы второго и третьего элементов И соединены с вйгеодами первого и второго элементов НЕ, отличающийся тем, что, с целью расширения функциональных возможностей сумматора путем обеспечения суммирования кодов с иррационными основаниями как в минимальной, так и в неминимальной форме, последовательный сумматор дополнительно содерзкит элементы И с седьмого по семнадцатый и шестой элемент ИЛИ, выход суммы одноразрядного сумматора соединен с входом второго элемента НЕ и с первыми входами первого, пятого, шестого, седьмого, восьмого и девятого элементов И, а выход второго элемента НЕ подключен к первым входам десятого, одиннадцатого и двенадцатого и к второму входу четвертого элементов И, выход переноса .одноразрядного сумматора соединен с входом третьего элемента НЕ, с первыми входами тринадцатого, четырнадцатого и пятнедi цатого и с вторыми входами nepaoi o, пятого и седьмого элементов И, выj: 4i ход третьего элемента НЕ соединен с первыми входами шестнадцатого и семнадцатого и с вторыми входами шестого, десятого и одиннадцатого элементов И, вторые входы восьмого, девятого, тринадцатого и пятнадцатого, а также третьи входы третьего и десятого элементов И соединены с входом первого элемента НЕ, выход которого подключен к вторым входам двенадцатого и семнадцатого и к третьим входам четвертого и шестого элементов И, вторые входы четырнад

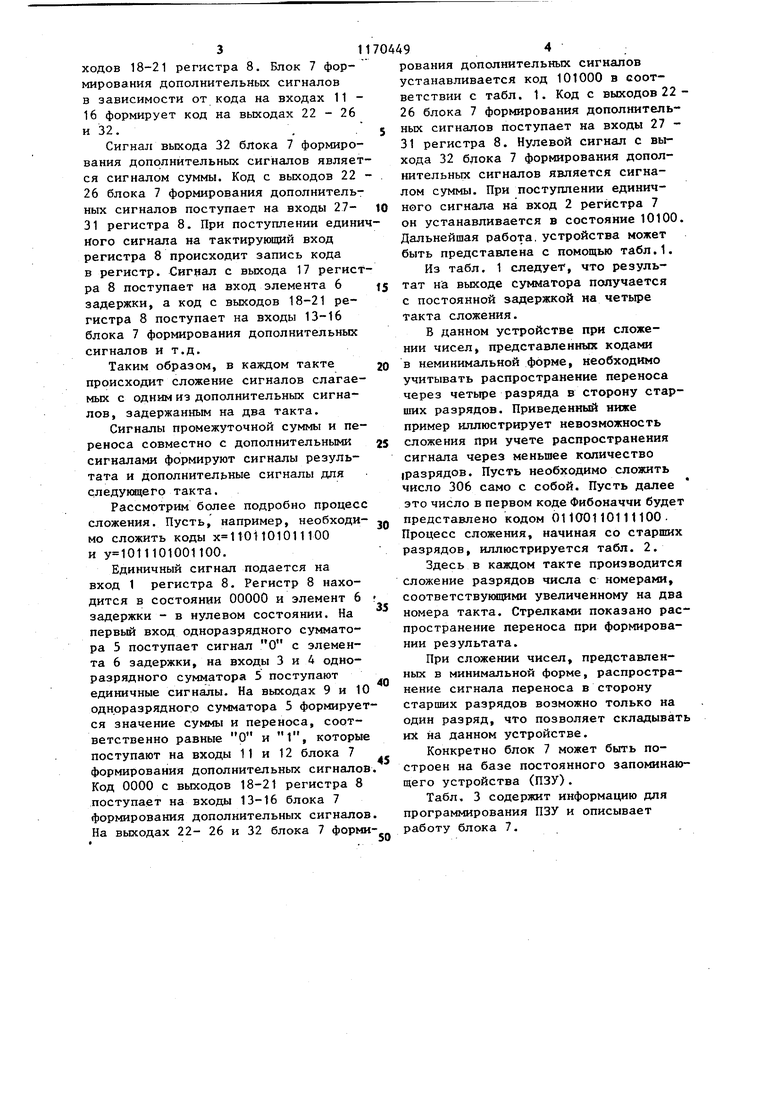

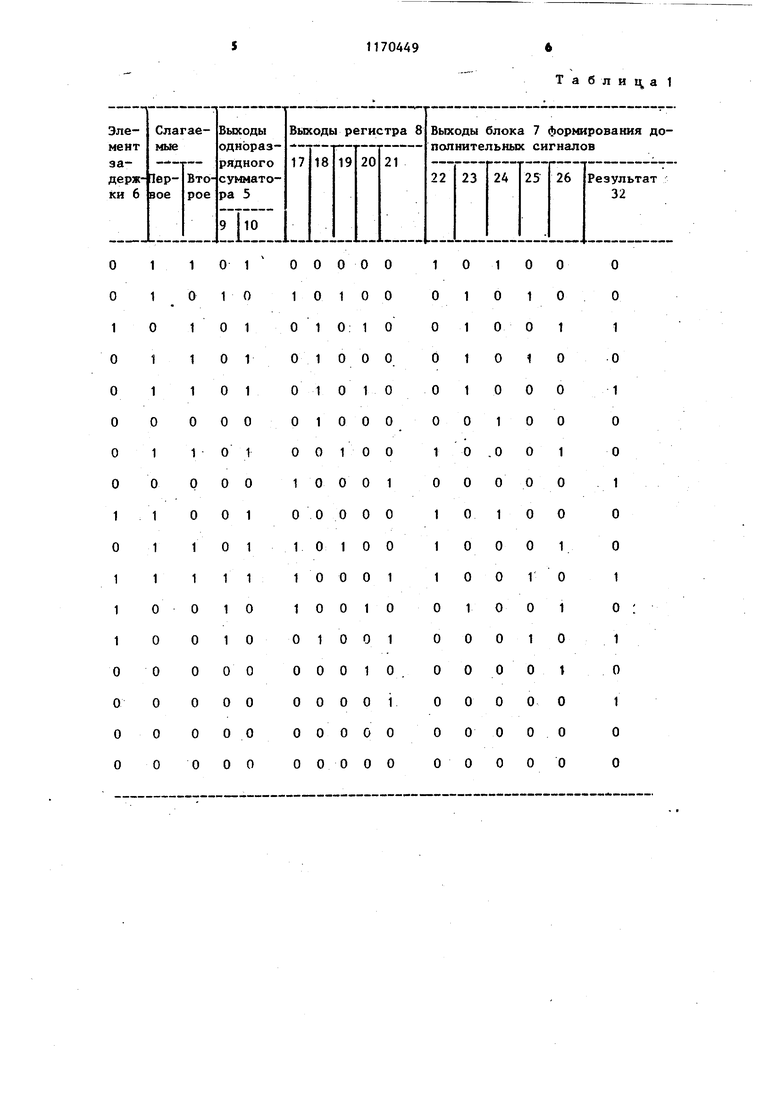

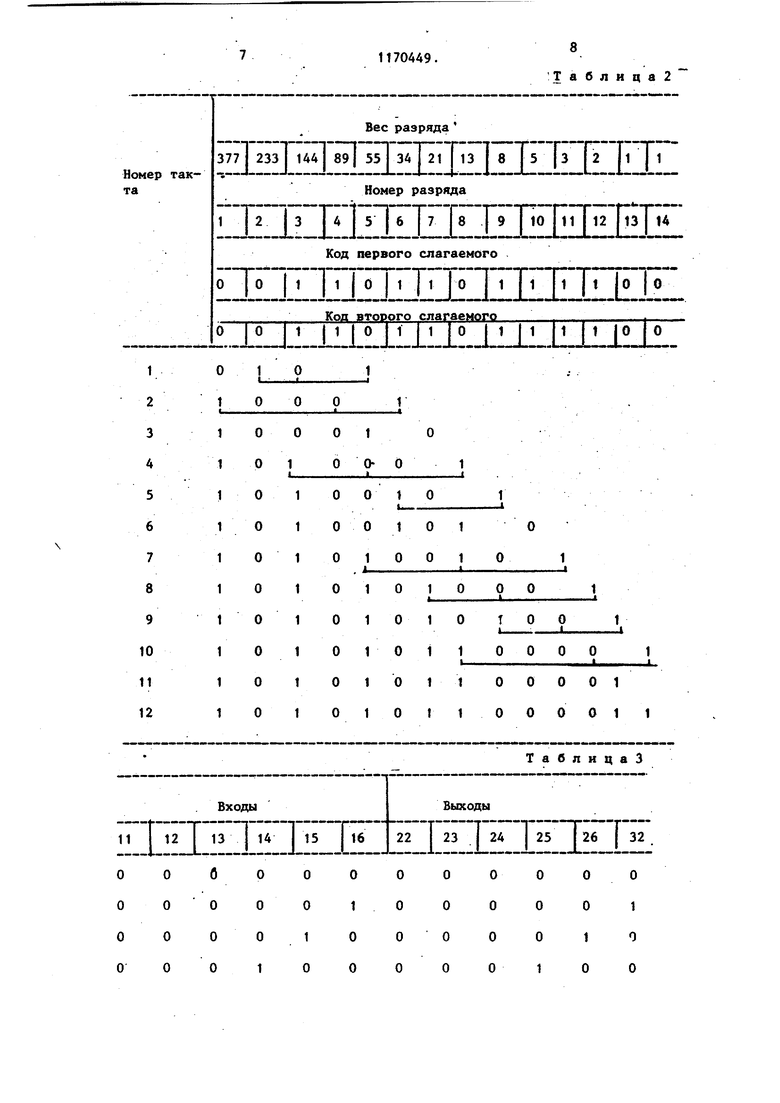

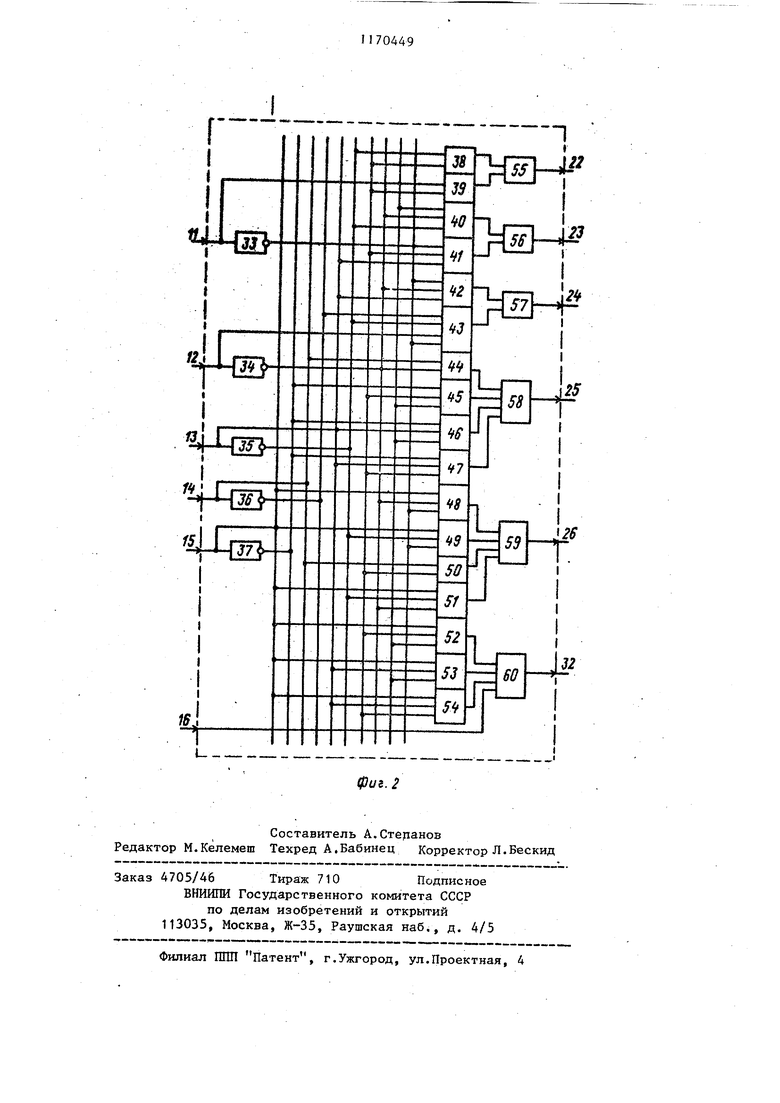

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах. Целью изобретения является расти,рение функциональных возможностей сумматора путем обеспечения суммирования кодов с иррациональными основаниями как в минимальной, так и в неминимальной форме. На фиг. 1 представлена структурная схема последовательного сумматора кодов с иррациональными основания ми; на фиг. 2 - функциональная схема блока формирования дополнительных сигналов суммы и переноса. Последовательньй сумматор содержит вход 1 начальной установки, тактовый вход 2, входы 3 и 4 слагаемых, одноразрядный сумматор 5, элемент задержки 6, блок 7 формирования дополнительных сигналов суммы и переноса и регистр 8 о Сумматор 5 имеет выходы 9 и 10 суммы и переноса, блок 7 - входы 11 - 16. Регистр 8 имеет вЬкоды 17 - 21, блок 7 - выходы 22 - 26, регистр 8 - входы 27-3 Выходом суммы является выход 32 блока 7. Блок 7 содержит элементы НЕ 33 37, элемент И 38 - 54 и элементы ИПИ 55-60. в системе счисления с иррациональными основаниями как в избыточной любое число, кроме нуля, может быть представлено несколькими формами кодов. Среди них вьщеляют минимальную форму, которая характеризуется отсутствием двух рядом стоящих единиц и .является единственной для каждого числа. В данном сумматоре слагаемые могут быть представлены произвольной формой кодов с иррациональными основаниями, что и определяет положительный эффект. Устройство работает следующим образом. При поступлении единичного сигнала на вход 1 устройства, регистр 8 устанавливается в нулевое состояние. На выходе элемента задержки 6 - нулевой сигнал. Поступление слагаемых на одноразрядный сумматор 5.начинается со старших разрядов. При поступлении сигналов на входы 3 и 4 слагаемых происходит их сложение на одноразрядном сумматоре 5. Сигналы суммы и переноса с выходов 9 и 10 одноразрядного сумматора 5 поступают на входы 11 и 12 блока 7 формирования дополнительных сигналов, на входы 1316 которого поступают сигналы с выходов 18-21 регистра 8. Блок 7 формирования дополнительных сигналов в зависимости от кода на входах 11 16 формирует код на выходах 22 - 26 и 32.. / Сигнал выхода 32 блока 7 формирования дополнительных сигналов являет ся сигналом суммы. Код с выходов 22 26 блока 7 формирования дополнительных сигналов поступает на входы 2731 регистра 8. При поступлении едини иого сигнала на тактирующий вход регистра 8 происходит запись кода в регистр. Сигнал с выхода 17 регист ра В поступает на вход элемента 6 задержки, а код с выходов 18-21 регистра 8 поступает на входы 13-16 блока 7 формирования дополнительных сигналов и т.д. Таким образом, в каждом такте происходит сложение сигналов слагаемых с одним из дополнительных сигналов, задержанным на два такта. Сигналы промежуточной суммы и переноса совместно с дополнительными сигналами формируют сигналы результата и дополнительные сигналы для следуницего такта. Рассмотрим более подробно процесс сложения. Пусть, например, необходиМО сложить коды х 1101101011100 и у 1011101001100. Единичный сигнал подается на вход 1 регистра 8. Регистр 8 находится в состоянии 00000 и элемент 6 задержки - в нулевом состоянии. На первый вход одноразрядного сумматора 5 поступает сигнал О с элемента 6 задержки, на входы 3 и 4 одноразрядного сумматора 5 поступают единичные сигналы. На выходах 9 и 10 одноразрядного сумматора 5 формирует ся значение суммы и переноса, соответственно равные О и 1, которые поступают на входы 11 и 12 блока 7 формирования дополнительных сигналов Код 0000 с выходов 18-21 регистра 8 поступает на входы 13-16 блока 7 формирования дополнительных сигналов На выходах 22- 26 и 32 блока 7 Форми рования дополнительных сигналов устанавливается код 101000 в соответствии с табл. 1. Код с выходов 2226 блока 7 формирования дополнительных сигналов поступает на входы 27 31 регистра 8. Нулевой сигнал с выхода 32 блока 7 формирования дополнительных сигналов является сигналом суммы. При поступлении единичного сигнала на вход 2 регистра 7 он устанавливается в состояние 10100. Дальнейшая работа, устройства может быть представлена с помощью табл.1. Из табл. 1 следует, что результат на выходе сумматора получается с постоянной задержкой на четыре такта сложения. В данном устройстве при сложении чисел, представленных кодами в неминимальной форме, необходимо учитывать распространение переноса через четыре разряда в сторону старших разрядов. Приведенный ниже пример иллюстрирует невозможность сложения при учете распространения сигнала через меньшее количество 1разрядов, Пусть необходимо сложить число 306 само с собой. Пусть далее это число в первом коде Фибоначчи будет представлено кодом 01100110111100. Процесс сложения, начиная со старших разрядов, иллюстрируется табл. 2. Здесь в каждом такте производится сложение разрядов числа с номерами, соответствующими увеличенному на два номера такта. Стрелками показано распространение переноса при формировании результата. При сложении чисел, представленных в минимальной форме, распространение сигнала переноса в сторону старших разрядов возможно только на один разряд, что позволяет складывать х на данном устройстве. Конкретно блок 7 может быть потроен на базе постоянного запоминаюего устройства (ПЗУ). Табл, 3 содержит информацию для рограммирования ПЗУ и описывает аботу блока 7.

0000 0100 1 01 О 1 О О О 1 010 1000 О 10 О 000 1 о 000 01 00 0 о о 1 0010 1001 0010

о о о i

0000 00 о о

Т а б л и t а 1

0100

о о 1 о 1 о о 1 о о 1

101

1 00 1

о

о 1

1

о

0100

о .0 о

1 000

о

0100 0001 о о 10

1

о о 1 о

о 1 о 1 о о

001

t

о

о о

0 о о Номер такта

1 12 I 3 р 5 J 6 17 8 I 9 10 11 12 МзТй

Код первого слагаемого

ч

Код ВТОРОГО слагаемо }

О I О 1 I 1 I О 11 I 1 I о I 1

1

2

3

4

5

6

7

8

9

10

11

12

Входы 1.1.., 11 12 13 I 14 15 16 ян 4

:Таблица2

Вес разряда

li-lil

Т

1 1

1 1

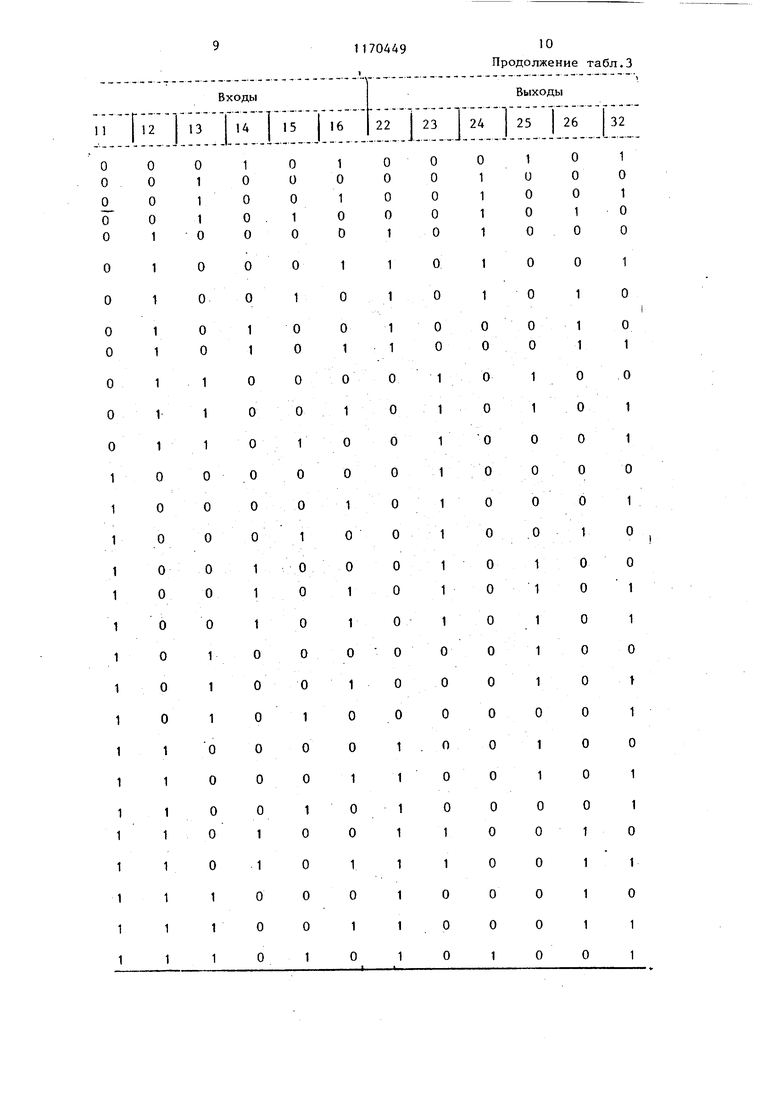

ТаблицаЗ

Выходы 22 I 23 ОО ОО ОО ОО 377 I 2331 144 89| 55 34T2lTl3 8 5 13 2 |Г Номер разряда 24 I 25 26 32 Оо 01 1о оо

Ч

р1/г,г

25

-f

| Последовательное устройство для сложения в избыточной двоичной системе счисления | 1980 |

|

SU968807A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-30—Публикация

1983-06-17—Подача