последовательного сумматора, второй вход одноразрядного сумматора соединен с входом второго слагаемого последовательного сумматора, второй

вход первого элемента И через второй элемент НЕ подключен к шине окончания суммирования последовательного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования последовательных кодов | 1984 |

|

SU1254472A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Последовательное множительное устройство | 1984 |

|

SU1233138A1 |

| Арифметическое устройство | 1985 |

|

SU1305662A2 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

ПОСЛЕДОВАТЕЛЬНЫЙ СУШАТОР, содержащий одноразрядный сзгмматор, два элемента И, элемент ИЛИ и регистр сдвига, содержащий в каждом разряде триггер, тактовый вход которого соединен с тактовой шиной последовательного сумматора, прямой выход триггера регистра сдвига, где п- разрядность суммируемых чисел, соединен с первьм входом первого элемента И, отличающийся тем, что, с целью повьшения быстродействия при суммировании чисел, поступающих старшими разрядами вперед, и сокращения объема оборудования, он содержит третий элемент И и два элемента НЕ, а каждый разряд регистра сдвига, начиная с второго, содержит три элемента И, элемент ИЛИ и элемент НЕ, причем первый вход одноразрядного сумматора соединен с выходом первого элемента И, выход суммы соединен с первмм входом второго элемента И и с выходом сумья 1 последовательного сумматора, выход второго элемента И соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого соединен с входом первого слагаемого последовательного сумматора, а второй вход соединен с шиной разрешения приема первого слагаемого последовательного сумматора и через первый элемент НЕ - с вторым входом второго элемента И, выход элемента ИЛИ подключен к D-входу триггера первого разряда регистра сдвига, в каждом разряде регистра сдвига, начиная с второго, первый вход первого элемента И регистра сдвига соединен с первым входом второго элемента И регистра сдвига и через элемент НЕ регистра сдвига - с первым входом третьего элемента И регистра сдвига, вторые входы второго и третьего элементов И регистра сдвига соединены соответственно с инверсньм и аряыьы выходами триггера предыдущего разряда регистра сдвига, выход первого СО элемента И регистра сдвига соединен ю с первым входом первого элемента И регистра сдвиса следующего разряда, а второй вход первого элемента И регистра сдвига - с вторьм входом третьего элемента И реиэдстра сдвига, выходы второго я третьего элементов И регистра сдвига соедсшеш с соответствуиярши входами элемента ИЛИ регистра сдвига, выход которого соединен с D-входом триггера того же разряда регистра сдвига первый вход первого элемента И второго разряда регистра сдвига соединен с выходом переноса одноразрядного сумматора и с выходом переноса

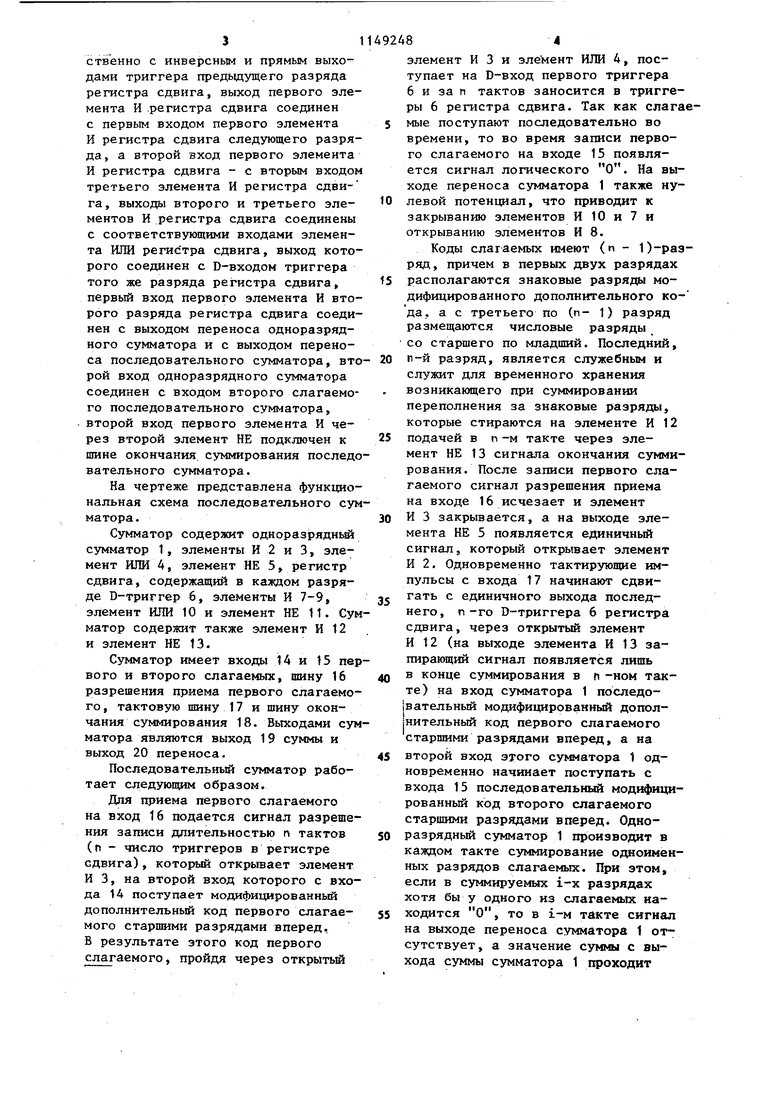

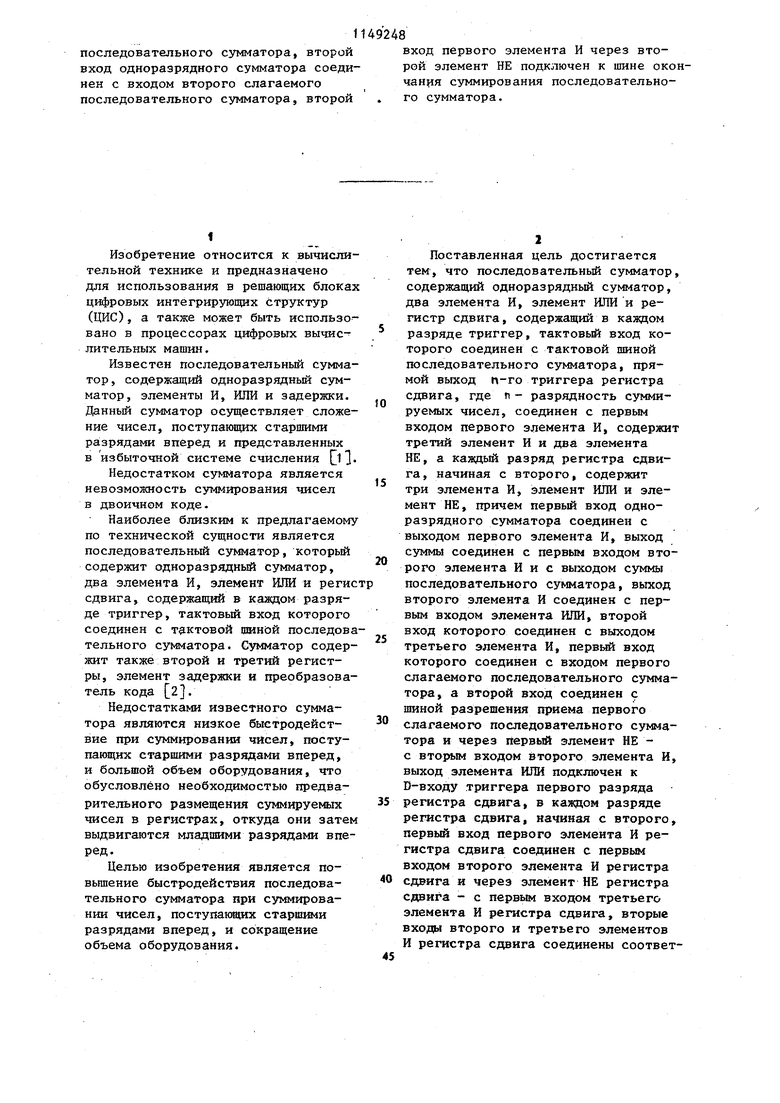

Изобретение относится к вычисли тельной технике и предназначено для использования в решающих блока цифровых интегрирующих структур (ЦИС), а также может быть использо вано в процессорах цифровых вычислительных машин. Известен последовательньй сумма тор, содержащий одноразрядный сумматор, элементы И, ИЛИ и задержки. Данный сумматор осуществляет сложе ние чисел, поступающих старшими ра зрядами вперед и представленных в избыточной системе счисления Недостатком сумматора является невозможность суммирования чисел в двоичном коде. Наиболее близким к предлагаемом по технической сущности является последовательный сумматор, который содержит одноразрядный сумматор, два элемента И, элемент ИЛИ и реги сдвига, содержащий в каждом разряде триггер, тактовый вход которого соединен с тактовой шинйй последов тельного сумматора. Сумматор содер жит также второй и третий регистры, элемент задержки и преобразова тель кода 2. Недостатками известного сумматора являются низкое быстродействие при суммировании чисел, поступающих старшими разрядами вперед, и большой объем оборудования, что обусловлено необходимостью предварительного размещения суммируемых чисел в регистрах, откуда они зате выдвигаются младшими разрядами впе ред. Целью изобретения является повышение быстродействия последовательного сумматора при сут мировании чисел, поступающих старнавли разрядами вперед, и сокращение объема оборудования. Поставленная цель достигается тем, что последовательный сумматор, содержащий одноразрядный сумматор, два элемента И, элемент ИЛИ и регистр сдвига, содержащий в каждом разряде триггер, тактовьй вход которого соединен с тактовой шиной последовательного сумматора, прямой выход h-ro триггера регистра сдвига, где п- разрядность суммируемых чисел, соединен с первым входом первого элемента И, содержит третий элемент И и два элемента НЕ, а каждый разряд регистра сдвига, начиная с второго, содержит три элемента И, элемент ИЛИ и элемент НЕ, причем первый вход одноразрядного сумматора соединен с выходом первого элемента И, выход суммы соединен с первым входом второго элемента И и с выходом суммы последовательного сумматора, выход второго элемента И соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого соединен с входом первого слагаемого последовательного сумматора, а второй вход соединен с шиной разрешения приема первого слагаемого последовательного сумматора и через первый элемент НЕ с вторым входом второго элемента И, выход элемента ИЛИ подключен к D-входу триггера первого разряда регистра сдвига, в каждом разряде регистра сдвига, начиная с второго, перв1Й вход первого элемента И регистра сдвига соединен с первьм входом второго элемента И регистра сдвига и через элемент НЕ регистра сдвига - с первым входом третьего элемента И регистра сдвига, вторые входы второго и третьего элементов И регистра сдвига соединены соответ3ственно с инверсным и прямым выходами триггера предыдущего разряда регистра сдвига, выход первого элемента И .регистра сдвига соединен с первым входом первого элемента И регистра сдвига следующего разря да, а второй вход первого элемента И регистра сдвига - с вторым входом третьего элемента И регистра сдвига, выходы второго и третьего элементов И регистра сдвига соединены с соответствующими входами элемента ИЛИ регистра сдвига, выход кото рого соединен с D-входом триггера того же разряда регистра сдвига, первый вход первого элемента И вто рого разряда регистра сдвига соеди нен с выходом переноса одноразрядного сумматора и с выходом переноса последовательного сумматора, вт рой вход одноразрядного сумматора соединен с входом второго слагаемо го последовательного сумматора, второй вход первого элемента И через второй элемент НЕ подключен к шине окончания суммирования послед вательного сумматора. На чертеже представлена функцио нальная схема последовательного су матора. Сумматор содержит однораз рядный сумматор 1, элементы И 2 и 3, элемент ИЛИ 4, элемент НЕ 5, регистр сдвига, содержащий в каждом разряде D-триггер 6, элементы И 7-9, элемент ИЛИ 10 и элемент НЕ 11. Су матор содержит также элемент И 12 и элемент НЕ 13. Сумматор имеет входы 14 и 15 пе вого и второго слагаемых, шину 16 разрешения приема первого слагаемо го , тактовую шину 17 и шину окончания суммирования 18. Выходами су матора являются выход 19 суммы и выход 20 переноса. Последовательный сумматор работает следующим образом. Для приема первого слагаемого на вход 16 подается сигнал разреше ния записи длительностью п тактов (п - число триггеров в регистре сдвига), кото1Я)1Й открывает элемент И 3, на второй вход которого с вхо да 14 поступает модифицированный дополнительный код первого слагаемого старшими разрядами вперед, В результате этого код первого слагаемого, пройдя через открытый 84 элемент И 3 и элемент ИЛИ 4, поступает на D-вход первого триггера 6 и за п тактов заносится в триггеры 6 регистра сдвига. Так как слагаемые поступают последовательно во времени, то во время записи первого слагаемого на входе 15 появляется сигнал логического О. На выходе переноса сумматора 1 также нулевой потенциал, что приводит к закрыванию элементов И 10 и 7 и открыванию элементов И 8. Коды слагаемых имеют (и - О-разряд, причем в первых двух разрядах располагаются знаковые разряды модифицированного дополнительного кода. а с третьего по (п- 1) разряд размещаются числовые разряды со старшего по младший. Последний, п-й разряд, является служебным и служит для временного хранения возникакидего при суммировании переполнения за знаковые разряды, которые стираются на элементе И 12 подачей в п-м такте через элемент НЕ 13 сигнала окончания суммирования. После записи первого слагаемого сигнал разрешения приема на входе 16 исчезает и элемент И 3 закрывается, а на выходе элемента НЕ 5 появляется единичный сигнал, который открывает элемент И 2. Одновременно тактирующие импульсы с входа 17 наминают сдвигать с единичного выхода последнего, п-го D-триггера 6 регистра сдвига, через открытый элемент И 12 (на выходе элемента И 13 запираинций сигнал появляется лишь в конце суммирования в п -ном такте) на вход сумматора 1 последо1вательный модифицированный допол нительный код первого слагаемого старшими разрядами вперед, а на второй вход этого сумматора 1 одновременно начинает поступать с входа 15 последовательный модифицированный код второго слагаемого старшими разрядами вперед. Одноразрядный сумматор 1 производит в каждом такте суммирование одноименных разрядов слагаемых. При этом, если в суммируемых i-x разрядах хотя бы у одного из слагаемых находится О, то в i-м такте сигнал на выходе переноса сумматора 1 отсутствует , а значение суммы с выхода суммы сумматора 1 проходит S через открытьй элемент И 2 и через элемент ИЛИ 4 и записывается в пер вый D- триггер 6 регистра сдвига и с помощью тактирующих импульсов, поступающих на вход 17, сдвигается в i-й разряд. Если в i-x разрядах обоих слагаемых имеется 1, то на вьЬсоде переноса cy №laтopa 1 в i-м такте появляется единичный сигнал, который поступает на вход элемента И 9 второго разряда регистра сдвига, а также на вход элемента И 7 и на- вход элемента НЕ 11, закрыв тем самым элемент И 8 второго разряда регистра сдвига и открью элементы И 9 и 7, а результат суммы с выхода суммы сумматора 1 поступа ет на информационный вход D-тригтера 6 первого разряда регистра

tmairm РТ g|g

Zmaiemf

y-r (

Зтакт

РТ

итккт

o

SmaMOf

II j t .

t wp (Лв в

MfifanKftpm

В приведенном примере использова- 5чение одноразрядного сумматоны следующие обозначения: Пд/ц - зна-ра 1 в i-м такте, Р-Т - результат

чение переноса одноразрядного сум-суммирования в i-м такте, Dt-8 матора 1 в i-M такте, Сдд - зна-единичные выходы с первого по восьО В, t в 1 в 1 О О, в О t to

JM/

в

sm

S8J7tS ISS t3mi

sw

ntHt

0

ffltlff

Olff Ciffl

0

Csm

№И1Ь11Ф

fttfifan ffprn 8 сдвига. При этом, если результат суммирования в (i-l)-M такте равен нулю, то в i-M такте на единичном выходе первого D-триггера 6 нулевой сигнал и элемент И 9 второго разряда регистра сдвига закрыт, а на нулевом выходе этого триггера единичный сигнал, который проходит элемент И 7 и элемент ИЛИ 10 и поступает на информационный вход второго D-триггера 6. В результате в i-M такте при суммировании двух единиц в первьй D-триггер 6 записывается результат суммы в i-м такте. т.е. О, а во второй D-триггер 6 иэмененньй с учетом возникшего в i-M такте переноса результат суммирования (i-l)-ro такта, т.е. вместо О записывается 1. Например:

мой D-триггеров регистра сдвига; Р1 - Р8 - с первого по восьмой разряды результата. Последний, П-и такт (в приведенном примере 8-й такт), используется для устранения возникающего в некоторых случаях переноса за знаковые разряды (в приведенном примере такой перенос оотсутствует).

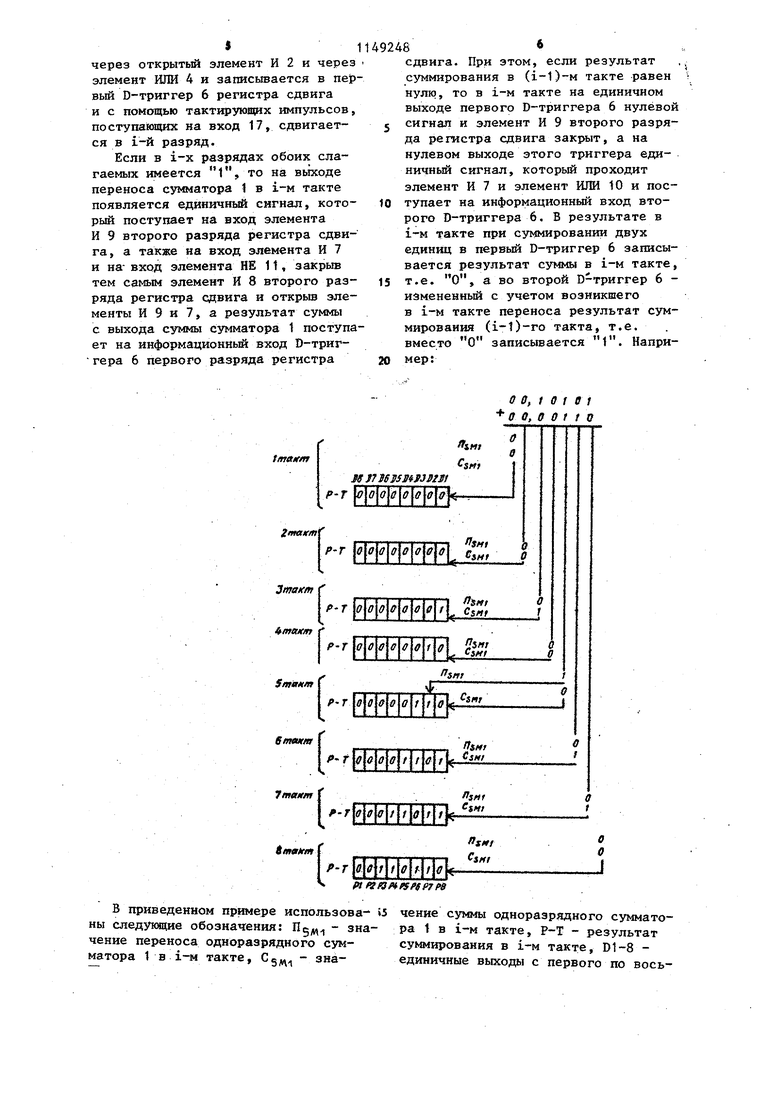

При суммировании отрицательных чисел или отрицательных с положительтят возникает перенос за знаковые разряды, который фиксируется в дополнительнстиг служебном разряде, стоящем после числовых разрядов перед знаковыми, т.е. если считать.

lataum

/}rIf / 0 i

f-T

Я-г|г{/| { J

л P2 P3 P fS P7 fS

су рования в зависи-рядного комбинационного сумматора

мости от дальнейшего использования1, либо снимается паралле колибо снимается с выхода последнего 55дом с единичных выход опре ен h-ro D-триггера регистра сдвига .ного числа D-триггеров 6 регистоа

через злемент И 12, либо снижаетсясдвига, начиная с первого D-триггес выходов суммы и переноса однораз-.ра 6. В последних двух случаях вычто знаковые разряды находятся в первом и втором разрядах, то служебным является п-и разряд. Обнуление служебного разряда производится в конце каждого цикла суммирования подачей сигнала окончания суммирования, совпадакицего с п-м тактом, через вход 18 на вход элемента НЕ 13, на выходе которого появляется в п-м такте нулевой сигнал, запрещающий прохождение информации в п-м такте на информационный вход первого D-триггера 6 регистра сдвига,

В качестве примера представим суммирование двух отрицательных чисел:.- f f, t f f t О t I, } O.ff t f

ff

r

J

деление прирадений задолго до оканчания суммирования вследствие обработки старшими разрядами вперед позволяет производить обмен приращениями меяяу решающими блоками ЦИС параллельно вычислениям, что значительно сокращает длительность шага интегрирования.

По сравнению с известньм предлагаемый сумматор кроме того, что , позволяет ввделять приращение до

окончания суммирования, не требует дополнительных циклов для перехода от старших разрядов к младшим. Это позволяет повысить быстродействие сумматора не менее чем в два раза при последовательном (поочередном) поступлении входных слагаемых. Кроме того, в предлагаемом сумматоре используется только один регистр сдвига, тогда как в известном принципиально необходимы два регистра сдвига.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для суммирования | 1976 |

|

SU674018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Соловьев Г.Н | |||

| Арифметические устройства ЭВМ | |||

| М., Энергия, 1978, с | |||

| Способ приготовления строительного изолирующего материала | 1923 |

|

SU137A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-04-07—Публикация

1983-10-19—Подача