Изобретение относится к радиотех- нике и может быть использовано для фильтрации сигналов, задаваемых цифровым кодом.

Цель изобретения - расширение функциональных возможностей путем реализации передаточной функции четного порядка.

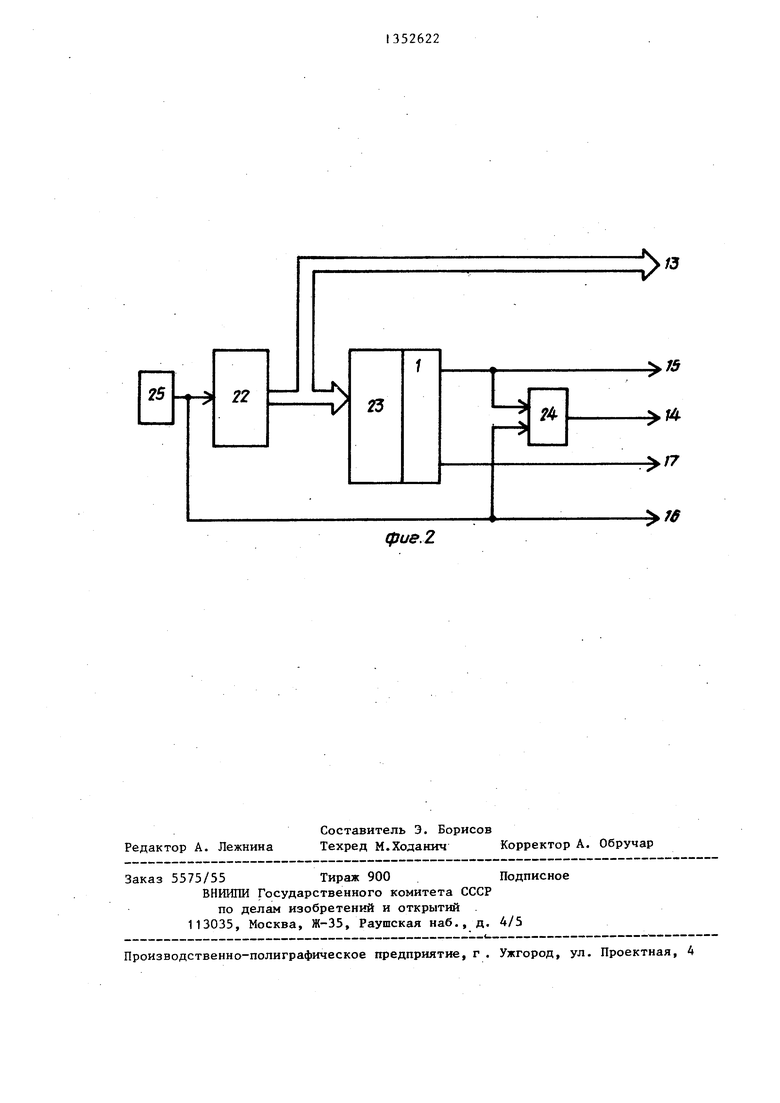

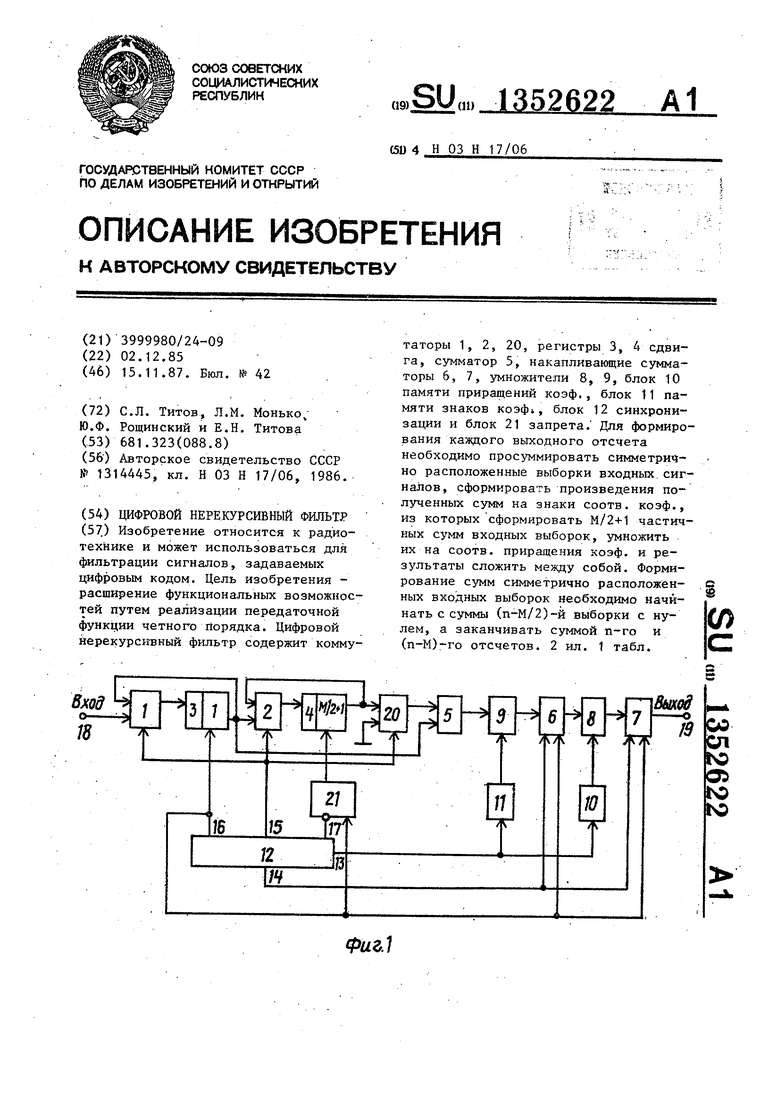

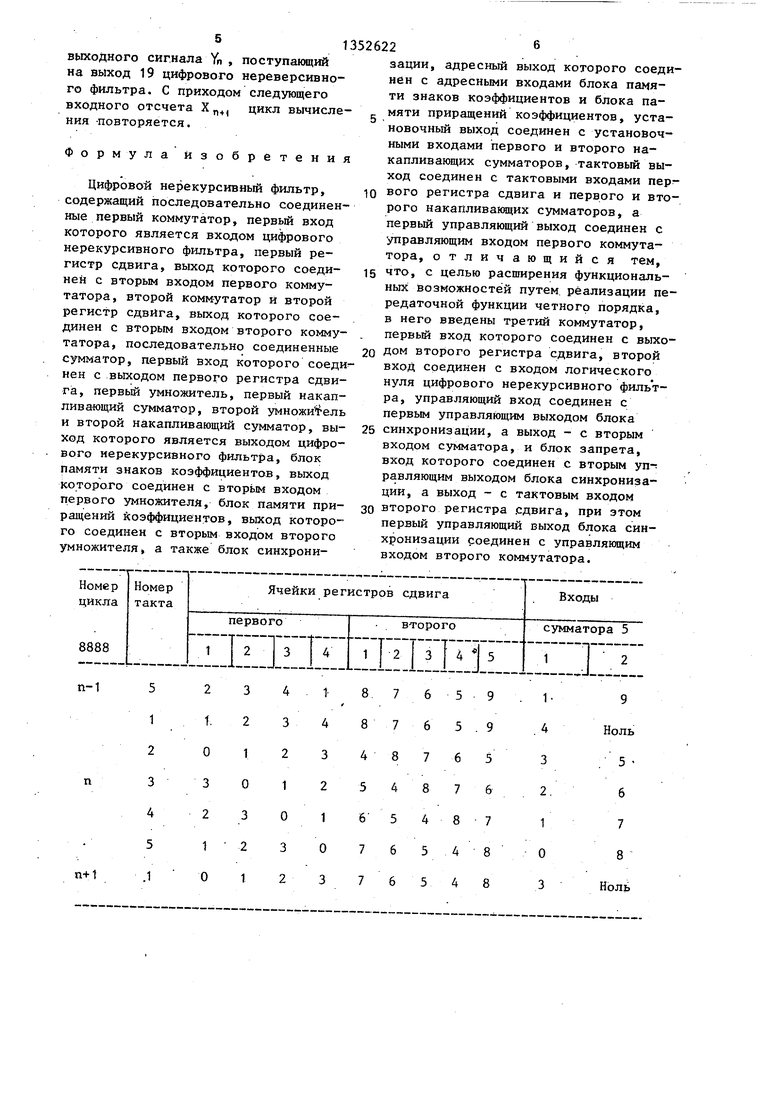

На фиг, 1 представлена электрическая структурная схема цифрового нерекурсивного фильтра; на фиг. 2 - схема блока синхронизации.

Цифровой нерекурсивньш фильтр (фиг. 1) содержит первый и второй коммутаторы 1 и 2, первый и второй регистры 3 и 4 сдвига, сумматор 5, первый и второй накапливающие сумматоры 6 и 7, второй и первый умножители 8 и 9, блок 10 памяти приращений коэффициентов, блок 11 памяти знаков коэффициента, блок 12 синхронизации, адресный выход 13 блока

а; их приращениями йа;-а;-а;., и их знаками sign (я;)

М/1-1

м1г-1

, signCO; )(Х.; Х„.,;)

Г-° 1

10

15

20

М/2

+ sign(a,)X, Щда;. (3)

i 0

Из выражения (3) следует, что для формирования каждого выходного отсчета, необходимо просуммировать сим метрично расположенные выборки входных сигналов (при этом n-M/2-я выборка суммируется е нулем), сформировать произведения полученных сумм на знаки соответствующих коэффициентов, из которых затем сформировать М/2+1 частичных сумм входных выборок умножить их на соответствующие приращения коэффициентов и результаты сложить между собой. При этоМ формирование сумм симметрично расположеннать с суммы n-M/2-й выборки с нулем, а заканчивать суммой rv-ro и п-М-го отсчетов.

синхронизации, установочный выход 14

блока синхронизации, первьй управляю- 25 «bix входных выбо рок необходимо начи- щий выход 15 блока синхронизации, второй управляющий выход 16 блока 15 синхронизации, тактовый выход 17 блока синхронизации, вход 18 цифрового нерекурсивного фильтра, выход 19 цифрового нерекурсивного фильтра, третий коммутатор 20 и блок 21 запрета.

Блок 12 синхронизации (фиг. 2) содержит счетчик 22 по модулю М/2+1, дешифратор 23, элемент И 24 и гене30

35

Первый и второй регистры 3 и 4 сдвига осуществляют хранение и через первый и второй коммутаторы 1, и 2. циклический сдвиг данных,хранящихся в них. Через коммутаторы 1 и 2 в регистры 3 и 4 сдвига производится также запись новых данных соответственно с входа 18 и первого регистра 3 сдвига. Сумматор 5 производит суммирование симметрично расположенных входных выборок, которые с номерами от п до п-М/2 содержатся в первом регистре 3 сдвига, а с номерами с п-М/2 до п-М - во втором регистре 4 сдвига. Первый умножитель 9 на +1 производит умножение сумм, посту- 4g пающих с выхода сумматора 5, на знаки соответствующих коэффициентов, которые хранятся в блоке 11 памяти знаков коэффициентов. Полученные произведения накапливаются в Первом накапливающем сумматоре 6 в виде частичных сумм, которые затем умножаются во втором умножителе 8 на малоразрядные приращения коэффициентов, хранящихся в блоке 10 памяти приращений коэффициентов, а полученные произведения накапливаются во втором накапливающем сумматоре 7.

ратор 25 тактовых импульсов.

Цифровой нерекурсивный фильтр работает следующим образом.

Для определения алгоритма работы предлагаемого фильтра исходным является алгоритм свертки

М

.; .

(1)

Учитывая, что коэффициенты фильтрации нерекурсивных фильтров, как правило, симметричны, выражение (1) для фильтра четного порядка можно представить в виде Н(1г

,.Vi n-M.i ). (2)

Выражение (2) можно преобразовать путем замены весовых коэффициентов

а; их приращениями йа;-а;-а;., и их знаками sign (я;)

М/1-1

м1г-1

, signCO; )(Х.; Х„.,;)НГ-° 1

М/2

+ sign(a,)X, Щда;. (3)

i 0

Из выражения (3) следует, что для формирования каждого выходного отсчета, необходимо просуммировать симметрично расположенные выборки входных сигналов (при этом n-M/2-я выборка суммируется е нулем), сформировать произведения полученных сумм на знаки соответствующих коэффициентов, из которых затем сформировать М/2+1 частичных сумм входных выборок, умножить их на соответствующие приращения коэффициентов и результаты сложить между собой. При этоМ формирование сумм симметрично расположеннать с суммы n-M/2-й выборки с нулем, а заканчивать суммой rv-ro и п-М-го отсчетов.

«bix входных выбо рок необходимо начи

«bix входных выбо рок необходимо начи-

Первый и второй регистры 3 и 4 сдвига осуществляют хранение и через первый и второй коммутаторы 1, и 2. циклический сдвиг данных,хранящихся в них. Через коммутаторы 1 и 2 в регистры 3 и 4 сдвига производится также запись новых данных соответственно с входа 18 и первого регистра 3 сдвига. Сумматор 5 производит суммирование симметрично расположенных входных выборок, которые с номерами от п до п-М/2 содержатся в первом регистре 3 сдвига, а с номерами с п-М/2 до п-М - во втором регистре 4 сдвига. Первый умножитель 9 на +1 производит умножение сумм, посту- пающих с выхода сумматора 5, на знаки соответствующих коэффициентов, которые хранятся в блоке 11 памяти знаков коэффициентов. Полученные произведения накапливаются в Первом накапливающем сумматоре 6 в виде частичных сумм, которые затем умножаются во втором умножителе 8 на малоразрядные приращения коэффициентов, хранящихся в блоке 10 памяти приращений коэффициентов, а полученные произведения накапливаются во втором накапливающем сумматоре 7.

В начале каждого цикла вычисления сигнал, поступающий с установоч

ного выхода 14 блока 12 синхронизации производит обнуление первого и второго накапливающих сумматоров 6 и 7. Запись в регистры 3 и 4 сдвига организована таким образом, что в начале каждого цикла вычисления в правой (выходной) ячейке памяти первого регистра 3 сдвига -хранится значение П-М/2-ГО входного отсчета, а в каждой ячейке левее - значение от- счетрв с номерами на единицу меньше. В то же время в правой ячейке памяти второго регистра 4 сдвига записано значение п-М+1-го входного отсчета, в следукхцей ячейке левее - п-М/2-го отсчета и в каждой следующей ячейке левее - отсчеты с номерами на единицу больше. В первом такте каждого цикла вычисления сигнал, поступающий с первого управляющего выхода 15 блока 12 синхронизации, переводит первый, второй и третий коммутаторы 1, 2 и 20 в режим коммутации сигналов соответственно с входа 18, выхода первого регистра 3 сдвига и входа логического нуля цифрового нерекурсивного фильтра. В конце первого такта вычисления в первую ячейку памяти первого регистра 3 сдвига записывается значение текущего входного отсчета, а из последней ячейки выводится значение п-М/2-го отсчета, которое записывается в первую ячейку второго регистра 4 сдвига, из последней ячейки которого выводится значение п-М+1-го отсчета. В течение же первого такта на входы сумматора 5 поступают значения п-М/2-го отсчета с выхода первого регистра 3 сдвига и значение нуля с выхода третьего коммутатора 20. Поэтому в конце первого такта вычисления в регистр первого накапливающего сумматора 6 запишется произведение значения п-М/2-г отсчета на знак М/2 коэффициента. Одновременно данное произведение умножится во втором умножителе 8 на значение приращения коэффициента

u о M/i и полученное произведение за- пишется во второй накапливающий сумматор 7.

Начиная с начала второго такта вычисления и до конца последнего такта вычисления сигнал, поступающий с первого управляющего выхода 15 блока 12 синхронизации на управляющие .входы первого, второго и третьего коммутаторов 1, 2, 20, переключает

0

0

5

первый коммутатор 1 в режим, коммутации сигнала с выхода пербого регистра 3 сдвига, а второй и третий коммутаторы 2 и 20 - в режим коммутации сигнала с выхода второго регистра 4 сдвига. В течение М/2-1-го такта вычисления под действием тактовых сигналов, поступающих с тактового выхода 16 блока 12 синхронизации и выхода блока 21 запрета на тактовые входы соответственно первого и второго регистров 3 и 4 сдвига, в них происходит циклическая пере- 5 запись информации. Во время последнего И/2+1-го такта вычисления тактовый сигнал поступает только на тактовый вход первого регистра 3 сдвига, а.во втором регистре 4 сдвига информация остается неизменной.

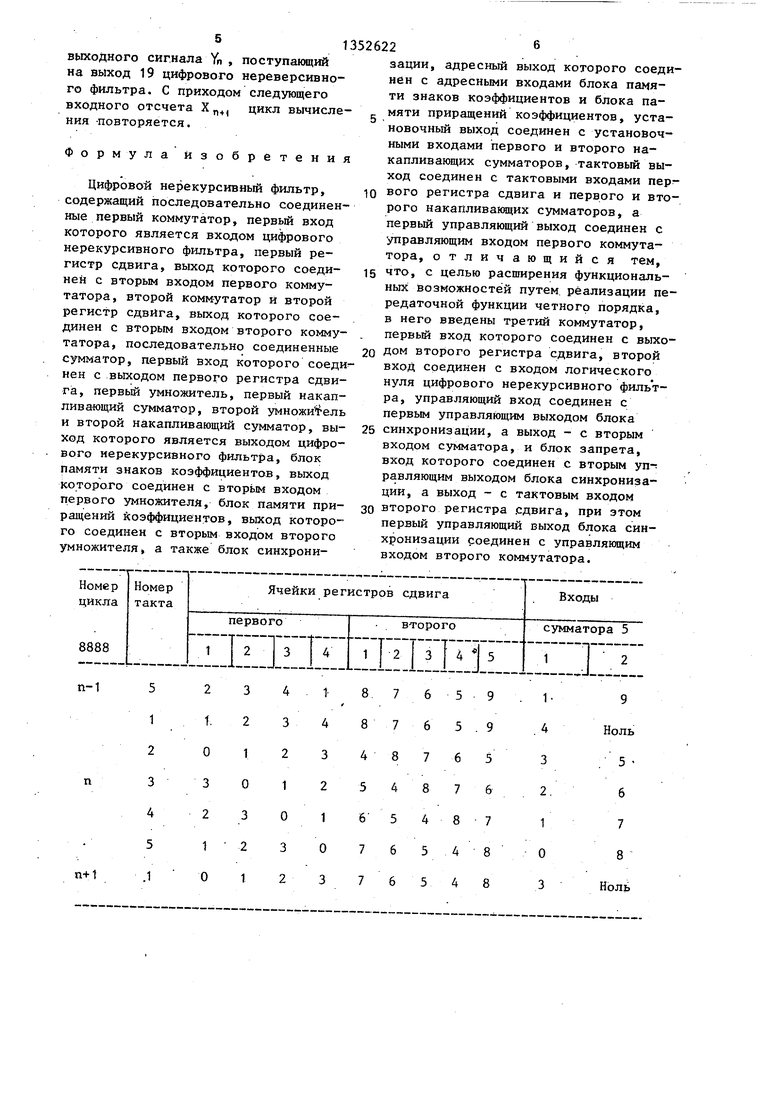

В таблице приведено расположение входных n-i-x отсчетов (указано значение i) в каждом из тактов п-го цикла вычисления в регистрах 3 и 4 сдвига для фильтра восьмого порядка,, а также номера отсчетов, по- . ступающих на вход сумматора 5.

В течение М/2+1 тактов каждого цикла вычисления на выходе первого накапливающего сумматора 6 последовательно формируются частичные суммы:

5

0

sign(a, )Х signCa,., )Х„,

(X.-i

. M/4-1

signC О; )«

+ X

n-AA -1

мг

sign(a«,)X., +2signCa; )«

(х„., +x

n-Wfi

),

45

go

которые во втором умножителе 8 умножаются на малоразрядные приращения

коэффициентов: « M/a-t icio. , поступающие из блока 10 памяти приращений коэффициентов синхронно с частичными суммами с выхода первого накапливающего сумматора 6. Вычисляемые произведения в течение 55 М/2+1 тактов вычисления суммиру ются вх) втором накапливающем сумматоре 7, где в конце последнего М/2+1-г о такта каждого цикла вычисления формируется очередной отсчет

выходного сигнала Уп , поступанмций на выход 19 цифрового нереверсивного фильтра. С приходом следующего

входного отсчета ния -повторяется.

X

„+, цикл вычислеФормула Изо

р е т е и и я

Цифровой нерекурсивный фильтр, содержащий последовательно соединенные первый коммутатор, первый вход которого является входом цифрового нерекурсивного фильтра, первый регистр сдвига, выход которого соединен с вторым входом первого коммутатора, второй коммутатор И второй регистр сдвИга, выход которого соединен с вторым входом второго коммутатора, последовательно соединенные сумматор, первый вход которого соеди нен с выходом первого регистра сдвига, первый умножитель, первый накап- ливатощий сумматор, второй умножитель и второй накапливающий сумматор, выход которого является выходом цифрового нерекурсивного фильтра, блок памяти знаков коэффициентов, выход KOTopo.ro соединен с вторьм входом первого умножители, блок памяти приращений Коэффициентов, выход которого соединен с вторым входом второго умножителя, а также блок синхрони10

1352622 .

зации, адресный выход которого соединен с адресными входами блока памяти знаков коэффициентов и блока памяти приращений коэффициентов, установочный выход соединен с установочными входами первого и второго накапливающих сумматоров, тактовый выход соединен с тактовыми входами перг вого регистра сдвига и первого и второго накапливаинцих сумматоров, а первый управляющий выход соединен с управляющим входом первого коммутатора, отличающийся тем, что, с целью расширения функциональных возможностей путем реализации передаточной функции четного порядка, в него введены третий коммутатор, первый вход которого соединен с выходом второго регистра сдвига, второй вход соединен с входом логического нуля цифрового нерекурсивного фильтра, управляющий вход соединен с первым управляющим выходом блока синхронизации, а выход - с вторым входом сумматора, и блок запрета, вход которого соединен с вторым уп- равляющим выходом блока синхрониза15

20

25

ции, а выход - с тактовым входом 30 второго регистра сдвига, при этом первый управляющий выход блока синхронизации соединен с управлянлцим входом второго коммутатора.

ции, а выход - с тактовым входом 30 второго регистра сдвига, при этом первый управляющий выход блока синхронизации соединен с управлянлцим входом второго коммутатора.

25

22

Редактор А. Лежнина

Составитель Э. Борисов

Техред М.Ходанич Корректор А. Обручар

Заказ 5575/55Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г . Ужгород, ул. Проектная, А

23

f4

15

фие.2

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой нерекурсивный фильтр нечетного порядка | 1985 |

|

SU1314445A1 |

| Цифровой нерекурсивный фильтр | 1987 |

|

SU1483608A1 |

| Цифровой нерекурсивный фильтр | 1983 |

|

SU1124430A1 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1332519A1 |

| Цифровой нерекурсивный фильтр | 1980 |

|

SU942247A1 |

| Устройство для контроля цифровых нерекурсивных фильтров | 1986 |

|

SU1406731A1 |

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Нерекурсивный цифровой фильтр-дециматор | 1986 |

|

SU1354394A1 |

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

) Изобретение относится к радиотехнике и может использоваться для фильтрации сигналов, задаваемых цифровым кодом. Цель изобретения - расширение функциональных возможностей путем реализации передаточной функции четного йорядка. Цифровой йерекурс1шный фильтр содержит коммутаторы 1, 2, 20, регистры 3, 4 сдвига, сумматор 5, накапливакнцие сумматоры 6, 7, умножители 8, 9, блок 10 памяти приращений коэф., блок 11 памяти знаков коэф, блок 12 синхронизации и блок 21 запрета. Для формирования каждого выходного отсчета необходимо просуммировать симметрично расположенные выборки входных, сигналов , сформировать произведения полученных сумм на знаки соотв. коэф., из которых сформировать М/2+1 частичных сумм входных выборок, умножить их на соотв. приращения коэф. и результаты сложить между собой. Формирование сумм симметрично расположенных входных выборок необходимо начинать с суммы (п-М/2)-й выборки с нулем, а заканчивать суммой п-го и (п-М)-го отсчетов. 2 ил. 1 табл. i (Л С ФигЛ

| Цифровой нерекурсивный фильтр нечетного порядка | 1985 |

|

SU1314445A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-11-15—Публикация

1985-12-02—Подача