1.1

1.Н

г

CS

I.C

ю

с1

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401471A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1647573A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля импульсных последовательностей в автоматизированных системах управления. Цель изобретения - расширение области применения устройства за счет контроля последовательности импульсных сигналов с произвольной, изменяемой очередностью поступления,- достигается введением элемента 5 задержки, регистра 9 и блока памяти 7. Предварительное программирование блока памяти 7 обеспечивает задание требуемой очередности чередования контролируемых импульсных сигналов. Устройство содержит входы 1.1...l.k, мультиплексор 2, элемент ИЛИ 3, счетчик 4 импульсов, элемент НЕ 6, элемент И 8, выход 10, 1 ил.§

сг

10

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля импульсных последовательностей в автоматизированных системах управления.

Цель изобретения - распшрение области применения устройства за счет контроля последовательности импульсных сигналов с произвольной, изменяе - мой очередностью поступления.

Поставленная цель достигается за счет введения элемента задержки, блока памяти и регистра, что обеспечивает возможность задания требуемой очередности чередования контролируемых импульсных сигналов путем предварительного пpoгpaм fflpoвaния блока памяти.

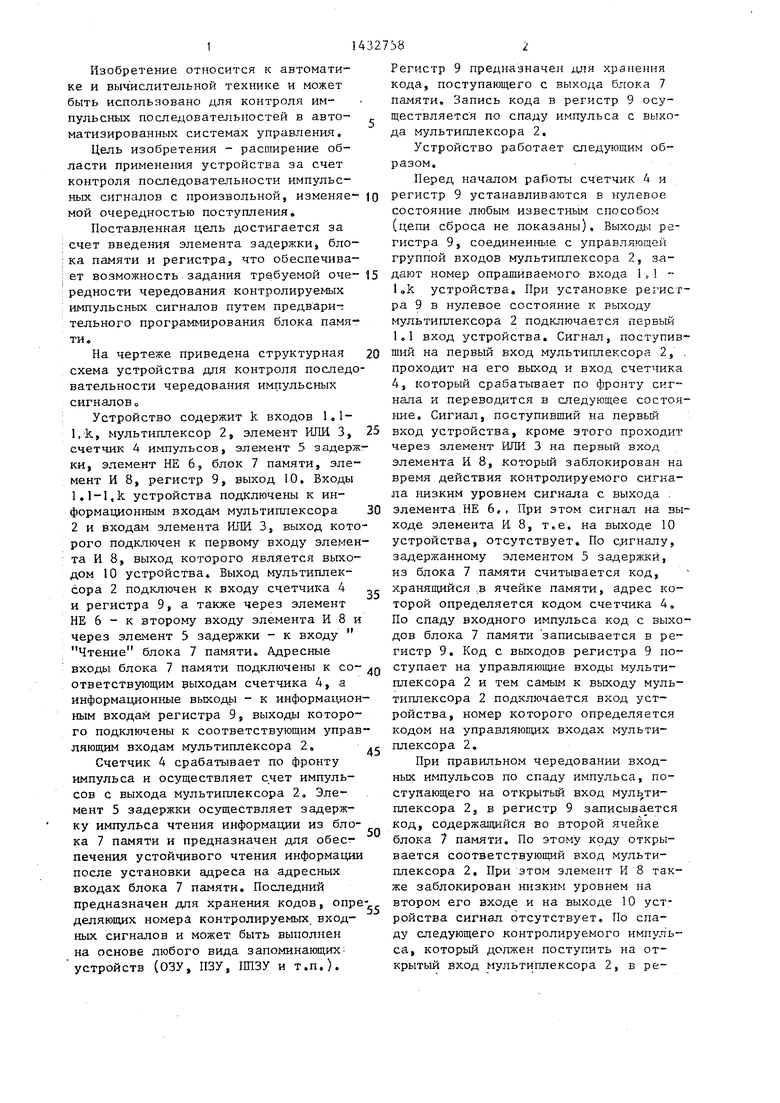

На чертеже приведена структурная схема устройства для контроля последовательности чередования импульсных сигналов о

Устройство содержит k входов 1,1- 1,-k, мультиплексор 2, элемент ИЛИ 3, счетчик 4 импульсов, элемент 5 задержки, элемент НЕ 6, блок 7 памяти, элемент И 8, регистр 9, выход 10. Входы l,l-l,k устройства подключены к информационным входам мультиплексора 2 и входам элемента ИЛИ 3, выход которого подключен к первому входу элемента И 8, выход которого является выходом 10 устройства. Выход мультиплексора 2 подключен к входу счетчика 4 и регистра 9, а также через элемент НЕ 6 - к второму входу элемента И 8 и через элемент 5 задержки - к входу Чтение блока 7 памяти. Адресные входы блока 7 памяти подключены к соответствующим рыходам счетчика 4, а информационные выходы - к информационным входам регистра 9, выходы которого подключены к соответствующим управляющим входам мультиплексора 2,

Счетчик 4 срабатывает по фронту импульса и осуществляет счет импульсов с выхода мультиплексора 2, Эле- мент 5 задержки осуществляет задержку импульса чтения информации из блока 7 памяти и предназначен для обеспечения устойчивого чтения информации после установки адреса на адресных входах блока 7 памяти. Последний предназначен для хранения кодов, опре деляющих номера контролируемых входных сигналов и может быть выполнен на основе любого вида запоминающих; устройств (ОЗУ, ПЗУ, 1ШЗУ и т.п.).

0

5

0

5

0

5

0

5

0

5

Регистр 9 предназначен для хранения кода, поступающего с выхода блока 7 памяти. Запись кода в регистр 9 осуществляется по спаду импульса с выхода мультиплексора 2.

Устройство работает следующим образом.

Перед началом работы счетчик 4 и регистр 9 устанавливаются в нулевое состояние любым известнь1м способом (цепи сброса не показаны). Выход :. регистра 9, соединенные с управляющей группой входов мультиплексора 2, задают номер опрашиваемого входа 1 е 1 - устройства. При установке регистра 9 в нулевое состояние к выходу мультиплексора 2 подключается первый К1 вход устройства. Сигнал, поступивший на первый вход мультиплексора 2, . проходит на его вькод и вход счетчика 4, который срабатывает по фронту сигнала и переводд тся в следующее состояние. Сигнал, поступивший на первьш вход устройства, кроме этого проходит через элемент ИЛИ 3 на первый вход элемента ИВ, который заблокирован на время действия контролируемого сигнала низким уровнем сигнала с выхода : элемента.НЕ 6,, При этом сигнал на выходе элемента И 8, т.е. на выходе 10 устройства, отсутствует. По сигналу, задержанному элементом 5 задержки, из блока 7 памяти считывается код, хранящийся .в ячейке памяти, адрес которой определяется кодом счетчика 4, По спаду входного импульса код с выходов блока 7 памяти записывается в регистр 9. Код с выходов регистра 9 поступает на управляющие входы мультиплексора 2 и тем самым к выходу мультиплексора 2 подключается вход устройства, номер которого определяется кодом на управляющих входах мультиплексора 2.

При правильном чередовании вход- ньк импульсов по спаду импульса, поступающего на открытый вход мультиплексора 2, в регистр 9 записывается код, содержащийся во второй ячейке блока 7 памяти. По этому коду открывается соответствующий вход мультиплексора 2. При этом элемент И 8 также заблокирован низким уровнем на втором его входе и на выходе 10 устройства сигнал отсутствует. По спаду следующего контролируемого импульса, который должен поступить на открытый вход мультиплексора 2, в

гистр 9 записывается из блока 7 памят тн.очередной кпд. Такая работа продолжается до полного заполнения счетчика. 4. Таким образрм, очередность контроля входных сигналов определяется кодом, хранящимся в блоке 7 памяти, причем число контролируемых в одном цикле сигналов определяется количеством разрядов счетчика и, соответственно, емкостью блока памяти.

По последнему в цикле контролируемому сигналу счетчик 4 устанавливается в нулевое состояние и по спаду входного сигнала в регистр 9 записы- вается код, хранящийся в нулевой ячейке блока 7 памяти, тем самым устрой- ство подготавливается к новому lyiKny контроля очередности поступления импульсных сигналов,

При нарушении порядка чередования сигналов на входных шинах l.l-l,k, например, в регистре 9 записан код, открьшающий мультиплексор 2 по третьему входу, а в это время приходит сиг- нал на второй вход устройства. При этом на выход мультиплексора 2 сигнал второго входа не проходит. При отсутствии сигнала на выходе мультиплексора 2 открывается по первому входу элемент И 8 и сигнал с второго входа устройства через элемент ИЛИ 3 проходит через элемент И 8 на выход 10, Наличие сигнала на этом выходе свидетельствует о нарушении порядка чередования входных импульсов.

При поступлении на любой из входов устройства двух импульсов вместо одного, устройство формирует на выходе 10 сигнал нарушения порядка чередования следующим образом.

По фронту входного импульса счетчик 4 устанавливается в следующее состояние, при этом из блока 7 памяти считывается код следующего приходящего

сигнала, С){ги;и;, постуг нлши v-;4i4HO на тот же вход устройства, не поступает на выход мультиплскгора 2 и не :in- крывает по первому входу элемент И 8 но проходит через элемент ШШ 3 на второй вход элемента И 8. Так как элемент И 8 оказывается открытым по двум входам, то на его выходе и выходе 10 устройства появляется сигнал нарушения порядка чередования.

Формула изобретения

Устройство для контроля поелсдова- тельяости чередования импульсных сигналов, содержащее элемент ШШ,элемент И, элемент НЕ, счетчик импульсов, мультиплексор, информационные входы которого являются соответствующими входами устройства и соедине ы с .,.дами элемента ИЛИ, выход которог-о соединен с первым входом элеменч-а И, выход которого является выходом уст ройства, выход мультиплексора соединен с входом счетчика и входом элемента НЕ, выход которого соединен с вторым входом элемента И, о т л и - чающееся тем, что, с целью расширения области применения за счет контроля последовательности им:- пульсных сигналов с произвольной, из меняемой очередностью поступления, в него введены элемент задержки, регистр и блок памяти, выходы которого соединены с соответствующими информационными входами регистра, выходы которого србдинены с соответствующими управляющими входами мультиплексора, выход котрого соединен с упр&вляю щим входом регистра и входом элемента задержки, выход которого соединен с входом чтения блока памяти, адресные входы которого соединены с соответствующими выходами счетчика.

| Устройство для контроля многоканальных импульсных последовательностей | 1985 |

|

SU1252930A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля последовательности чередования импульсных сигналов | 1985 |

|

SU1256184A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-23—Публикация

1987-03-31—Подача