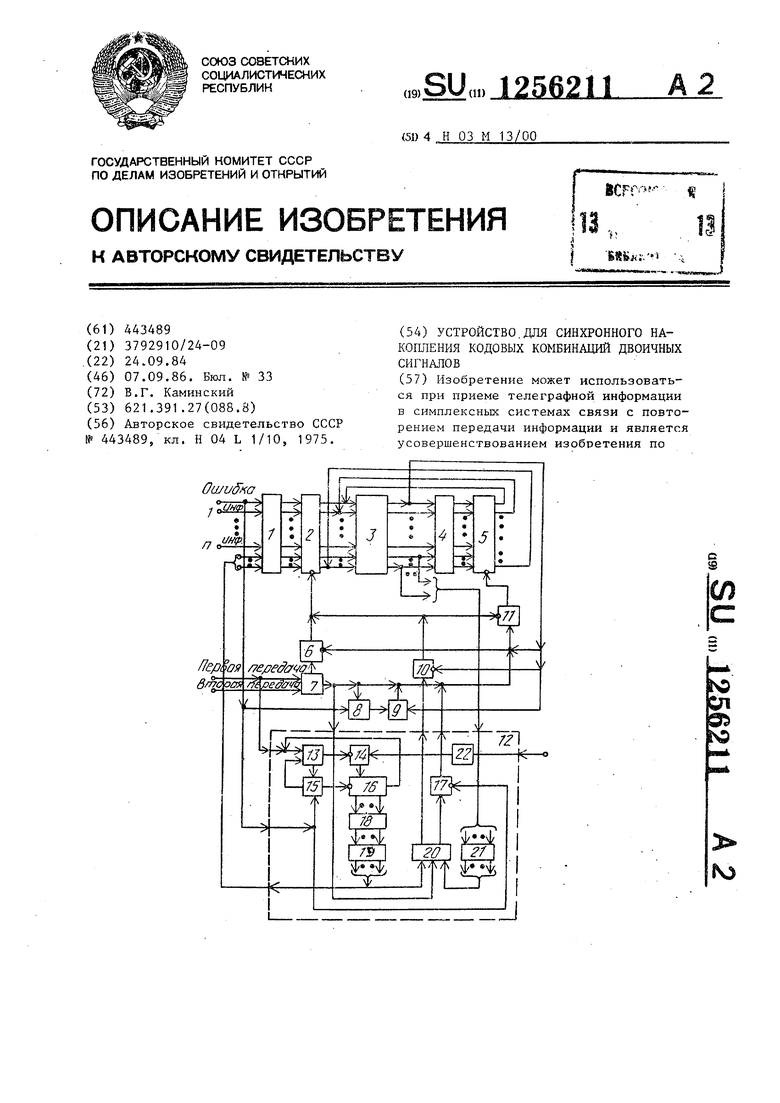

авт.св. W 443489. Повышается помехоустойчивость. Устройство содержит входной и выходной регистры 1 и 4, накопительную матрицу (НМ) 3, клапаны 2,5,6,8, 10 и 11, триггеры 7 и 9 и узел 12 коррекции (УК). УК Т2 включает триггер 13, клапаны 14,15 и 17, двоичный счетчик 16, регистры 18 и 21, блок 19 коммутации, блок 20 сравнения и делитель 22 тактовой частоты. По сигналу Первая передача, поступающему на триггер 7, входной клапан 2 открьшается, а выходной клапан 5 закрьшается. При этом в НМ 3 записывается входная информация, сигналы с декодирующего устройства и сигналы плотйости ошибки, поступающие с УК 12. Значение двоичного счетчика 16 определяет условную прогнозируемую плот1

Изобретение относится к области передачи телеграфной информации и передачи данных, может быть использовано для обеспечения помехоустойчивого приема информации в симплексных системах связи с повторением передачи информации помехоустойчивым кодом и исправлением ошибок методом выбора неискаженной информации из повторяемых передач и является усовершенствованием устройства по авт.св. №4.43489.

Цель изобретения - повышение помехоустойчивости .

На чертеже представлена структурная злектрическая схема устройства для синхронного накопления кодовых комбинаций двоичных сигналов.

Устройство для синхронного накопления кодовых комбинацийдвоичных сигналов содержит входной регистр 1, - входной клапан 2, накопительную матрицу 3, выходной регистр 4, выходной клапан 5, первый клапан 6, первый триггер 7, второй клапан 8, второй триггер 9, третий 10 и четвертый 11 клапаны и узел 12 коррекции, содержащий третий триггер 13, пятый 14 и шестой 15 клапаны, двоичньш счетчик 16j седьмой клапан 17, первьй регистр 18, блок 19 коммутации, блок

ность ошибок. По сигналу Вторая передача входной клапан 2 закрывается j а выходной клапан 5 открывается. При этом НМ 3 устанавливается в режим регенерации информации, который осуществляется до тек пор, пока не появится сигнал Ошибка с НМ 3. В этом случае информация записывается через входной клапан 2. Режим, записи информации из канала осуществляется до поступления с декодирующего устройства сигнала Ошибка, который устанавливает в НМ 3 режим регенерации. Одновременно с помощью блока 20 сравнения производится выбор тех искаженных кодовых комбинаций, прогнозируемая плотность ошибок в которых меньше. Им отдается предпочтение приперезаписи вНМ 3. Поясняется работа УК 12. 1з.п. ф-лы,1 ил.

20 сравнения, второй регистр 21 и де- литель 22 тактовой частоты.

Устройство для синхронного накопления кодовых комбинаций двоичных сигналов работает следующим образом.

Первоначально сигналом Первая передача первый триггер 7 устанавливается в положение, когда входной

клапан 2 открыт, а выходной клапан 5 закрыт. В результате входная информация по 1-п шинам, сигналы с декодирующего устройства и сигналы ошибки записываются в накопительную матрицу 3.

Сигналы плотности ошибки формируются схемой следующим образом.

Третий триггер 13 сигналом Первая передача устанавливается в нулевое положение, открывая шестой клапан 15 и закрывая пятьй клапан. 14. При поступлении первой обнаруженной ошибки сигнал Ошибка через открытый шестой клапан 15 поступает на второй вход двоичного счетчика 16, устанавливая его в исходное положение, а также устанавливает третий триггер 13 в единичное состояние, запрещая прохождение сигналов Ошибка через

шестой клапан 15 и разрешая прохождение сигналов с делителя 22, определяющего начало каждого нового кодового блока, через открытый пятьш клапан 14. В результате для каждого следующего кодового блока значение двоичного счетчика 16 увеличивается на единицу, s

Поскольку каждьш канап связи характеризуется своими закономерностями распределения плотностей ошибок внутри пачек ошибок, то для согласования значения плотности ошибок со значе- О кием двоичного числа, записываемого через входной регистр 1 в накопительную матрицу, устанавливается блок 19, с помощью которого коммутируются его входы с выходами таким образом,чтобы 15 минимальное значение двоичного числа 001 соответственно максимальному значению плотности ошибок, 010 - следующему меньшему значению плотности ошибок и т.д.20

Одновременно с записью блока и сиг нала наличия ошибки производится запись значения двоичного счетчика 16, определяющего условную прогнозируемую плотность ошибок. Когда пачка ошибок 25 кончается, двоичный.счетчик 16 обнуляется, а с его выхода третий триггер 13 устанавливается в нулевое положение, запрещая прохождение сигнала с делителя до тех пор, пока вновь не по- 30 ступит сигнал Ошибка, указывающий на начало новой пачки ошибок. I При поступлении повторной передачи первый триггер 7 устанавливается в единичное состояние, в результате чего 35 входной клапан 2 закрывается, а выходной клапан 5 открывается. В результате накопительная матрица устанавливается в режим регенераций информации. Режим регенерации существу-40 ет до тех пор, пока не появится сигнал Ошибка на первом выходе накопительной матрицы 3, который производит запрет перезаписи информации на выходном клапане 5 и разрешение запи-45 си через входной клапан 2 (путем запрета единиц на первом клапане 6).

Кроме того, произбодится запуск в единичное состояние второго тригге-so ра 9, устанавливая режим записи из канала до тех пор, пока с декодирующего устройства не появится сигнал Ошибка, который, пройдя через открытый второй клапан 8, устанавливает 55 второй триггер 9 в .нулевое состояние, тем самым устанавливает в накопительной матрице 3 режим регенераций.

Одновременно с режимом разнесения записи в накопительную матрицу 3 из неискаженных пачками ошибок участков передач производится выбор тех кодовых комбинаций из подвергшихся искажениям пачек ошибок, прогнозируемая плотность ошибок в которых имеет меншее значение. Эта процедура осуществляется путем сравнения кодовых чисел в блоке 20, сосчитанных из регистра 21, и из первого регистра 18 через блок 19. Из второго регистра 21 производится считьшание кодового числа, определяющего плотность ошибок в кодовом блоке, поступающем из канала связи.

При этом, если плотность ошибок, исказивших . блок в канале связи больше, чем плотность ошибок записанной в накопительной матрице 3 информации то выдается предпочтение информации, записанной в накопительной матрице 3. С этой целью сигнал с второго выхода блока 20, пройдя через третий клапан 10, поступает на управляющий вход входного клапана 2 и на. первый вход четвертого клапана 11, открывая тем самым выходной клапан 5 для перезаписи информации в накопительную матрицу 3, независимо от состо яния второго триггера 9.

В случае, если плотность ошибок в кодовом блоке, поступившем из канала связи, меньше плотности ошибок в кодовом блоке, записанном в накопительной матрице 3, отдается предпочтение кодовому блоку, поступившему из канала связи.

С этой целью сигнал с первого выхода блока 20, пройдя через-седьмой клапан 17, поступает через четвертый клапан 11 на вход выходного клапана 5 и путем запрета на первом клапане 6 разрешает прохождение информации через входной клапан 2.

Операция управления записью со стороны блока 20 сравнения разрешается лишь в случае отсутствия ошибок как в кодовом блоке, поступившем из канала связи, так и записанном в накопительной матрице 3.

При наличии искаженного блока управление записью ведется управляющими сигналами Ошибка, а для исключения влияния управляющих сигналов со стороны блока 20 вводятся третий 10 и седьмой 17 клапаны, на вторые

51

входы которых подаются соответствующие сигналы Ошибка,

Формула изобретения

1. Устройство для синхронного накопления кодовых комбинаций двоичных сигналов по авт.св. № 443489, отличающееся тем, что, с целью по- вьшения помехоустойчивости, в него введены третий и четвертьй клапаны и узел коррекции, при этом первый вход третьего клапана подключен к первому выходу узла коррекции, .второй вход - к объединенным второму входу второгс триггера и соответствующему выходу накопительной матрицы, а выход третьего клaпaнJl соединен с управляющим входом входного клапана и первым входом четвертого клапана, второй выход первого триггера подключен к управляющему входу выходного клапана через четвертый клапан и к второму выходу узла коррекции, первый вход узла коррекции соединен с первым входом входного клапана, второй вход узла коррекции подключен к первому.входу первого триггера, третий вход узла коррекции подключен к второму выходу первого триггера, четвертый вход узла коррекции подключен -к последним выходным разрядам накопительной матрицы, а пятый вход узла коррекции подключен к делителю тактовой частоРедактор И. Шулла

Составитель О. Константинова

Техред И..Попович Корректор 0. Луговая

Заказ 4837/58Тира х 815

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-355 Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

116

ты, третий выход узла коррекции под- ключен к последним разрядам входного регистра.

2, Устройство по п.1,о т л и ч а- ю щ е е с я тем, что узел коррекции содержит пятый клапан, первый регистр, последовательно соединенные второй триггер, шестой клапан, двоичный счетчик, второй регистр, блок коммутации блок сравнения и седьмой клапан, второй вход которого подключен к объединенным первым входам пятого клапана и узла коррекции, второй выход второго

триггера подключен к второму входу пятого клапана, первый выход которого подключен к первому входу второго триггера, а второй выход через двоичный счетчик - к объединенным второму

входу второго триггера и второму входу узла коррекции, выходы блока коммутации подключены к объединенным третьему выходу узла коррекции и первому входу блока сравнения, второй вход

которого является третьим входом узла коррекции, к третьему входу блока сравнения подключены выходы первого регистра, причем второй выход блока сравнения является первым выходом

узла коррекции, второй вход шестого клапана является пятым входом узла коррекции, входы первого регистра подключены к четвертому входу узла коррекции.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронного накопления кодовых комбинаций двоичных сигналов | 1972 |

|

SU443489A1 |

| Устройство для синхронного накопления кодовых комбинаций двоичных сигналов | 1978 |

|

SU675612A2 |

| Устройство для декодирования двоичного кода | 1984 |

|

SU1220128A1 |

| Корректор ошибок | 1989 |

|

SU1810909A1 |

| Устройство для кодирования и декодирования последовательного кода с коррекцией одиночных ошибок | 1976 |

|

SU732877A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

Изобретение может использоваться при приеме телеграфной информации в симплексных системах связи с повторением передачи информации и является усовершенствованием изобретения по сл с: ю

| Устройство для синхронного накопления кодовых комбинаций двоичных сигналов | 1972 |

|

SU443489A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-09-07—Публикация

1984-09-24—Подача