Изобретение относится к электро- связи и может использоваться в системах передачи данных для повышения достоверности декодирования.

Цель изобретения -- повьшдение достоверности декодирования.

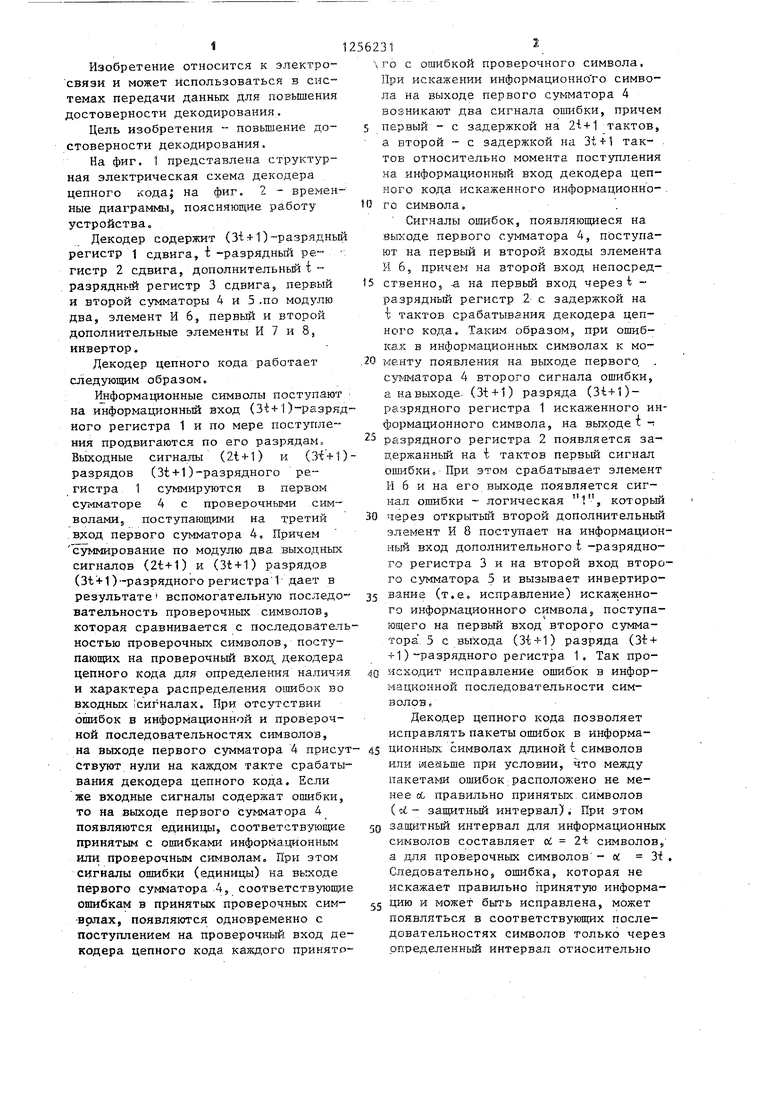

На фиг. t представлена структурная электрическая схема декодера цепного кода} на фиг. 2 - временные диаграммы, поясняющие работу устройства,,

Декодер содержит (3i:i-1)-разрядный регистр t сдвига, t-разрядньш регистр 2 сдвига, дополнительный t- разрядный регистр 3 сдвига, первый и второй сумматоры 4 и 5 ,по модулю два, элемент И 6, первый и второй дополнительные элементы И 7 и 8, инвертор.

Декодер цепного кода работает следующим образом,

: Информахщонные символы поступают на информационный вход (З + О-разряд- ного регистра 1 и по мере поступления продвигаются по его разрядам, Выходные сигналы (2t+1) и (ЗЧ+1)- разрядов (3t+1)-разрядного регистра 1 суммируются в первом сумматоре 4 с проверочными сим- воламИ; поступающими на третий .вход первого сумматора 4, Причем суммирование по модулю два выходных сигналов (2t+1) и (3t+1) разрядов (3t + 1 )-разрядного регистра 1 дает в результате вспомогательную последо вательность проверочных символов, которая сравнивается с последовательностью проверочных символов, поступающих на проверочный вход, декодера цепного кода для определения наличия и характера распределения ошибок во входных сигналах. При отсутствии ошибок в информационной и проверочной последовательностях символов.

го с ошибкой проверочного символа. При искажении информационного симв ла на выходе первого сумматора 4 возникают два сигнала опшбки, прич

5 первый - с задержкой на такто а второй - с задержкой на так тов относительно момента поступлен на информационный вход декодера це ного кода искаженного информационн

to го символа.

Сигналы ошибок, появляющиеся на выходе первого сумматора 4, поступ ют на первый и второй входы элемен И 6, причем на второй вход непосре

tS ственно, -а на первый вход через i разрядный регистр 2 с задержкой на i тактов срабатывания декодера цеп ного кода. Таким образом, при ошиб ках в информационных символах к мо

.20 кенту появления на. выходе первого, сумматора 4 второго сигнала ошибки а на выходе. (3t + 1) разряда (3t-f1)- разрядного регистра 1 искаженного формационного символа, на выходе t

25 разрядного регистра 2 появляется з держанный на i тактов первый сигна ошибки. При этом срабатьшает элеме

И 6 и на его выходе появляется сиг нал оши.бки - логическая 1, котор

30 через открытьй второй дополнительн элемент И 8 постутгает на информаци иьй вход дополнительного t -разрядн го регистра 3 и на второй вход вто го сумматора 5 и вызывает инвертир

35 вание (т.е. исправление) искаженно го информационного символа, поступ ющего на первый вход второго сумма тора. 5 с выхода (3-f; + 1) разряда (3 + 1)-разрядного регистра 1, Так про

4Q исходит исправление ошибок в инфор мацконной последовательности символов

Декодер цепного кода позволяет исправлять пакеты ошибок в информана выходе первого сумматора 4 присут- 45 ционных символах длиной t символов

Ствуют нули на каждом такте срабатывания декодера цепного кода. Если же входные сигналы содержат ошибки, то на выходе первого сумматора 4 появляются единицы, соответствующие принятым с ошибками информационным или проверочным символам. При этом сигналы ошибки (единицы) на вьжоде первого сумматора 4, соответствуюшряе ошибкам в принятых проверочных сим- вопах, появляются одновременно с поступлением на проверочный вход декодера цепного кода каждого принятр562312-,

го с ошибкой проверочного символа. При искажении информационного символа на выходе первого сумматора 4 возникают два сигнала опшбки, причем

5 первый - с задержкой на тактов, а второй - с задержкой на так- . тов относительно момента поступления на информационный вход декодера цепного кода искаженного информационно-,

to го символа.

Сигналы ошибок, появляющиеся на выходе первого сумматора 4, поступают на первый и второй входы элемента И 6, причем на второй вход непосредtS ственно, -а на первый вход через i разрядный регистр 2 с задержкой на i тактов срабатывания декодера цепного кода. Таким образом, при ошибках в информационных символах к мо.20 кенту появления на. выходе первого, сумматора 4 второго сигнала ошибки, а на выходе. (3t + 1) разряда (3t-f1)- разрядного регистра 1 искаженного информационного символа, на выходе t -;

25 разрядного регистра 2 появляется задержанный на i тактов первый сигнал ошибки. При этом срабатьшает элемент

И 6 и на его выходе появляется сигнал оши.бки - логическая 1, который

через открытьй второй дополнительный элемент И 8 постутгает на информацион- иьй вход дополнительного t -разрядного регистра 3 и на второй вход второго сумматора 5 и вызывает инвертирование (т.е. исправление) искаженного информационного символа, поступающего на первый вход второго сумматора. 5 с выхода (3-f; + 1) разряда (3 + + 1)-разрядного регистра 1, Так происходит исправление ошибок в инфор- мацконной последовательности символов

Декодер цепного кода позволяет исправлять пакеты ошибок в информаИ.ЛИ меньше при условии, что между пакетами ошибок;расположено не менее сС правильно принятых, символов ( оС защитный интервал) , При этом

gg защитньй интервал для информационных символов составляет ct 2i символов, а для проверочных символов - К 3i . Следовательно, ошибка, которая не искажает правильно принятую информа 5 цию и может быть исправлена, может появляться в соответствующих последовательностях символов только через определенный интервал относительно

последней ошибки в предыдущем пакете ошибок. Если на информационньш и проверочный входы декодера цепного кода поступают последовательности информационных и проверочных симво- лов, пораженных пакетами ошибок, величины которых не превьшгают исправляющую способность декодера, то ошибки в информационных символах исправляются по алгоритму, описанному, а

ошибки в проверочных символах не устраняются. При этом все сигналы ошибок, возникающие на выходе первого сумматора 4 и вызванные искаженными проверочными-символами, через 2i так тов работы декодера цепного кода поступают в t -разрядный регистр 2 и покидают его, не оказывая влияния на выходную информационную последова- тельность символов.

Пусть на декодер цепного кода поступают такие последовательности информационных и проверочньк символов, НТО информационные символы содержат пакет ошибок длины t (фиг. 2а а проверочные - содержат пакет ошибок длины -t + it (фиг. 2в) . Для упрощения построения; временных диаграмм работы декодера цепного кода (фиг. 2) приняты следующие условия:-по каналу свйзи передается длительный ошибки, возникающие из-за помех в канале связи, приводят к появлению учитывая, что информационные и проверочные символы, передавае- мые по каналу связи, чередуются, величина интервала, занимаемого пакетом ошибок (в канале связи), равна 2i: + it, где U t t . ,

Таким образом, пакет ошибок в информационных символах не превьш1а- ет исправляющей способности декодера цепного кода и может быть исправлен, а пакет ошибок в проверочных символах превьш1ает исправляющую способ- кость декодера цепного кода на ii символов.

Рассматривают работу декодера цепного кода в этом случае. В исходном состоянии, до момента поступления на декодер цепного кода входных сигналов с ошибками ()-paзpядный регистр 1,-t-разрядный регистр 2 и дополнительныйt -разрядный регистр 3 находятся в нулевом состоянии. Сле- довательно, на выходах первого 4 и второго 5 сумматоров, а также на выходах элемента И 6 дополнительных

5

0

5 0

5 0

первого 7 и второго 8 элементов И также присутствуют нули.

При наличии ошибок во входных последовательностях символов на выходе первого сумматора 4 одновременно с поступлением на проверочный вход декодера цепного кода искажен- ньк проверочных символов (фиг. 2в) появляются сигналы ошибок (фиг. 2а) и через i тактов работы декодера цепного кода в t-разрядном регистре 2 записано t сигналов ошибок, а в (3t+ +1)-разрядном регистре 1 находятся i искаженных информационных символов (фиг. 2а) . Далее Hat+1 такте работы декодера цепного кода на выходе дополнительного i -разрядного регистра 3 появитсяt +1 сигнал ошибки (фиг. 2г) и одновременно с ним на выходе i -разрядного регистра 2 появится первый сигнал ошибки (фиг. 2д). Одновременное появление двух сигналов приводит к появлению на выходе элемента И 6 сигнала ошибки (фиг. 2е), который, поступая через открытый второй дополнительный, элемент И 8 на информационный вход t -разрядного регистра 3 и на вход второго сумматора 5 (фиг. 2и), записан вt -разрядный регистр 3 и вызывает инвертирование (т.е. вносит ошибку) информационного символа на выходе второго сумматора 5 (фиг. 2к).

На протяжении at -1 тактов работы декодера цепного кода также вносятся ошибки в выходную информационную последовательность (фип. 2к). При последующих тактах работы декодера цепного кода ошибок в выходной информационной последовательности нет. К этому моменту проходит 2i тактов работы декодера цепного кода и искаженные информационные символы расположены с (t+l) по 2 .разрядах (31+1)-разрядного регистра 1, в i-разрядном регистре 2 и в. дополнительном i -разрядном регистре 3 расположены с (t-At-1) по (t-1) разрядах A t символов ошибок, вызванных искаженными проверочными символами .

Далее на 2t+1 такте работы декодера цепного кода выходе первого суматора 4 появляется первый сигнал ошибки информационных символов (фиг. 2д), задержанньй на 2t+1 тактов (фиг. 2б) относительно момента появления на входе декодера цепного

кода (фиг. 2а). Одновременно с этим сигналом появляются сигналы ошибки и на выходах t -разрядного 2 и дополнительного i- разрядного 3 регистров (фиг, 2д, ж). Однако при этом срабатывают первый дополнительный элемент И 7 и инв ертор 9, который своим выходным сигналом (фиг. 2и) закрывает второй дополнительный элемент И .8, исключив тем самым прохождение сигнала ошибки с выхода элемента И 6 (фиг, 2е) на вход второго сумматора 5 и на вход дополнительного i - разрядного регистра 3 (фиг. 2и), В этом .случае инвертирования информационного символа на выходе сумматора 5 (фиг, 2к) не происходит, т.е. не внесена ошибка в правильно принятые информационные символы.

На протяжении ui -1 тактов работы декодера цепного кода блокирование сигналов ошибок, появляюгцихся на выходе элемента И 6, производится аналогично,. По прошествии 2i+ ui тактов работы декодера цепного кода t-разрядный регистр 2 находится в нулевом состоянии (фиг. 2ж), с второго дополнительного элемента И 8 снимается сигнал блокировки (фиг. 2з). После 3t такта работы декодера цепного кода в t-разрядном регистре 2 записано t сигналов ошибок, вызванных искаженными информационными символами, Далее с 3t+1 по 4t такты работы декодера цепного кода производится , исправление информационных символов, содержащих пакет ошибок длиной t символов, аналогично описанному.

Пусть в интервале между 4t+1 и 5t . тактами работы декодера цепного кода поступают проверочные символы, содержащие ошибки (фиг, 2в)о Эти искаженные проверочные символы вызывают появление на выходе первого сумматора 4 сигнала ошибки (фиг, 2г), Одновре- менно п. этим на выходе i -разрядного регистра 2 появляются сигналы ошибок информационных символов, задержанные относительно момента появления на

выходе первого сумматора 4 (фиг. 2г) на t тактов (фиг, 2д). Эти -два сигнала вызывают появление на выходе элемента И 6 сигнала ошибок (фиг. 2е), с Однако этот сигнал ошибки не вызывает инвертирование выходного сигнала второго сумматора 5 и тем самым не вносит ошибок в информацию, так как заблокирован сигналом с выхода ин- Q вертора 9 (фиг, 2з),

Формула изобретения

Декодер цепного кода, содержащий 5 последовательно соединенные (3i; + 1)- разрядный регистр сдвига, первый сумматор по модулю два,t -разрядный регистр сдвига и элемент И, а также второй сумматор по модулю два, пер0 вый вход которого подключен к выходу (3i-f-1)-ro разряда, (3i + l )-ра.зрядного регистра сдвига, выход (2t+1)-ro разряда которого подсоединен к второму входу первого сумматора по модулю ,

5 два, второй вход элемента И подключен к выходу первого сумматора по модулю два, причем-информационный вход (3t + 1)-разрядного регистра и третий вход первого су 1матора по

0 модулю два являются соответственно информационным и проверочным входами декодера, а выход второго сумматора по модулю два является выходом декодера, отличающий, ся тем,

что, с целью повьшхения достоверности декодирования, в него введены последовательно соединенные дополнительный -t -разрядный регистр сдвига, первый дополнительньй элемент И, инвер-

0 тор и второй доплнительный элемент И, при этом выход второго дополнительного элемента И подсоединен к второму входу второго сумматора по модулю два и информационному входу дополни 5 тельного t-разрядного регистра сдвига, а выход элемента И подсоединен к вторым входам первого и второго дополнительных элементов И.

2t

5t

Редактор М. Бланар

Составитель В. Орлов Техред М.Ходанич

Заказ 4838/59

Тираж 624

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

4t

5t

6t

7t i

Фиг. 2

Корректор И.Муска

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Устройство для декодирования с коррекцией ошибок | 1988 |

|

SU1584108A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Устройство для декодирования циклических кодов | 1987 |

|

SU1429325A1 |

| Декодер укороченного кода Хэмминга | 1983 |

|

SU1109924A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1837385A1 |

Изобретение относится к электросвязи. Повьшается достоверность декодирования . Декодер содержит (3t +1)- разрядный регистр сдвига (РС) 1, два .i-разрядных PC 2 и 3, два сумматора по модулю два (С) 4 и 5, три элемента И 6, 7 и 8 и инвертор 9. При ошибках в информац. последовательности символов срабатывает элемент И 6 и на его выходе появляется сигнал ошибки - логическая 1, который через открытый элемент И 8 поступает на информац. вход PC 3 и на один вход С 5. Это вызовет инвертирование искаженного информац. символа, поступающего на другой вход С 5 с выхода PC 1. Т. об., происходит исправление ошибок в информац. последовательности символов. При поступлении проверочных символов, содержащих ошибки, сигнал ошибок на выходе элемента И 6 не вызовет инвертирования выходного сигнала С 5 и тем самым не внесёт ошибок в информацию, так как будет заблокирован сигналом с выхода инвертора 9. Цель достигается введением PC 3, элементов И 7 и 8 и инвертора 9. 2 ил. (Л д :л 9д д DO

| Устройство для декодирования сверточного кода | 1973 |

|

SU510803A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Шляпоберский В.И | |||

| Основы техники передачи дискретных сообщений.-М.: Связь, 1973, с | |||

| Электромагнитный счетчик электрических замыканий | 1921 |

|

SU372A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1985-04-05—Подача