1

13341

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки дискретных данных.

Цель изобретения - устранение возможности перегрузки при ограниченных линейных зонах блоков,

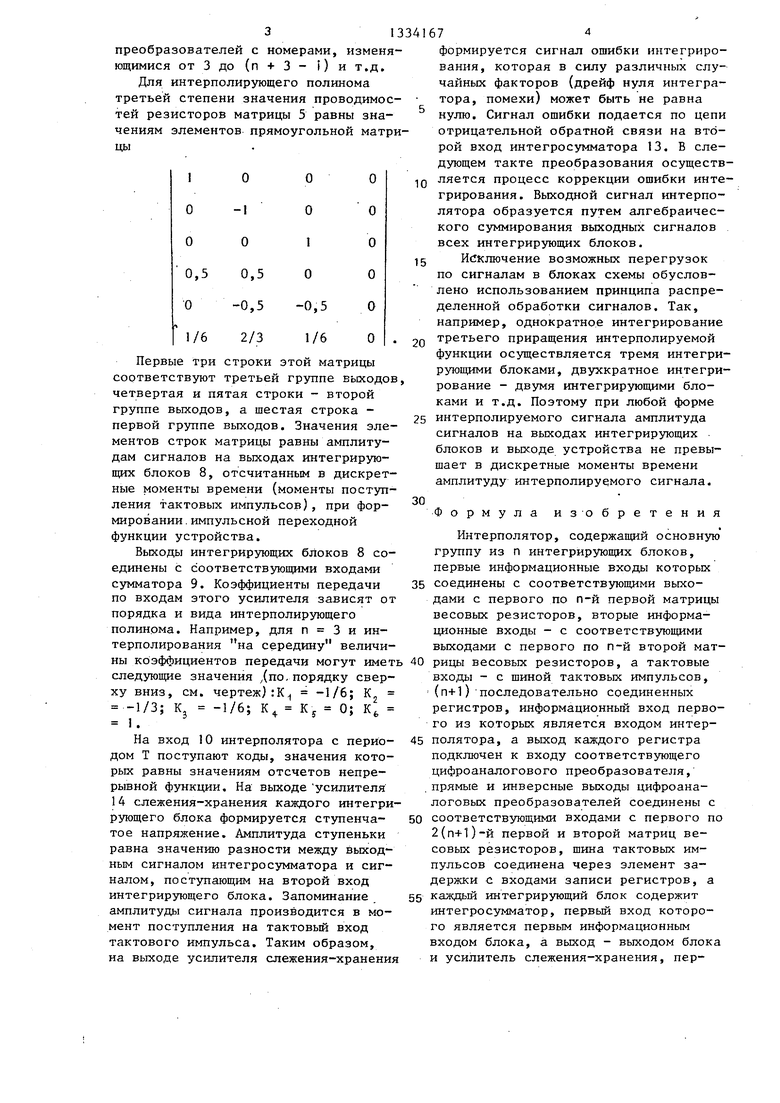

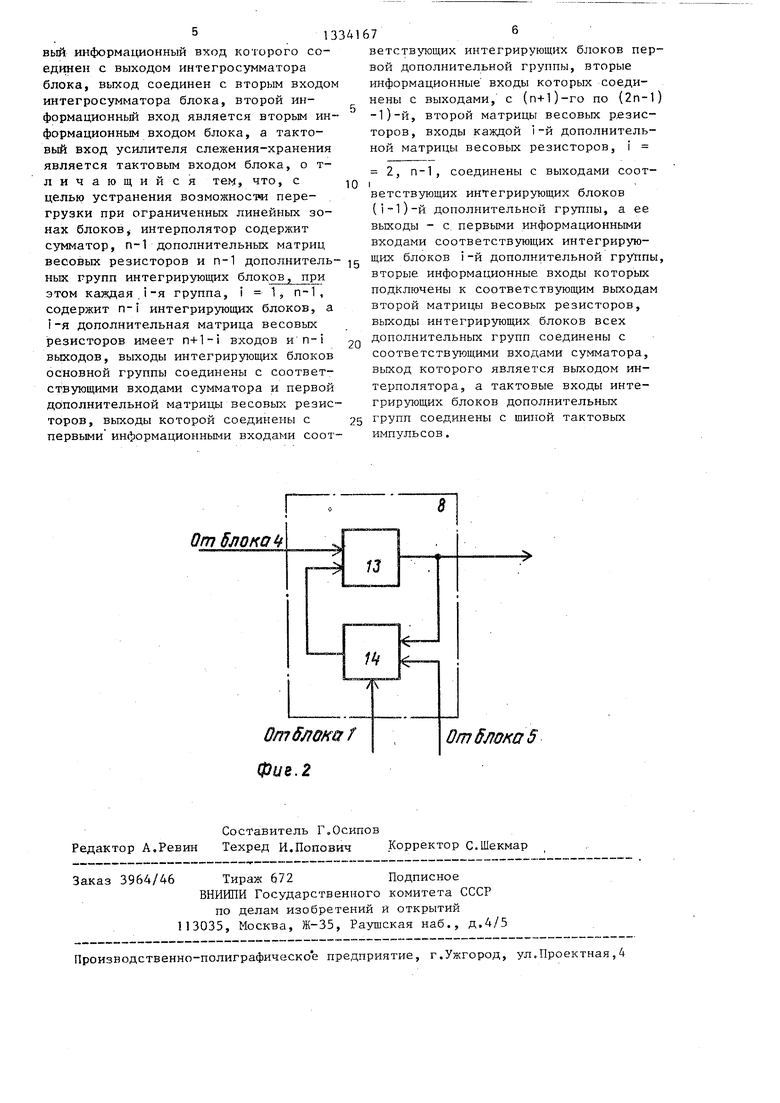

На фиг.1 изображена схема предлагаемого интерполятора; на фиг,2 - схема интегрирующего блока.

Интерполятор содержит элемент 1 задержки, регистры 2, 4 цифроана логовые преобразователи 3 первую 4 и вторую 5 матрицы весовых резисторов, дополнительные матрицы 6 и 7 весовых резисторов, интегрирующие блоки 8, сумматор 9, вход 10, выход 11 и шину 12 тактовых импульсов.

Интегрирующий блок содержит инте- Гросумматор 13 и усилитель 14 слежения-хранения .

Интерполятор работает следующим образом.

Регистры совместно с цифроаналого йыми преобразователями 3 образуют цифроаналоговый -сдвигающий регистр,- на парафазных выходах которого формируются сигналы с амплитудами, пропор циональпыми узловым значениям интерполируемой функции. Вькоды цифроаналоговых преобразователей связаны с первыми входами интегрирующих блоко через матрицу 4, которая выполнена так$ что первая выходная шина матрицы соединена через первый резистор с прямьм выходом первого цифроаналого- вого преобразователя и через второй резистор - с инверсным выходом второго цифроаналогового преобразователя, второй выход матрицы соединен через третий резистор с инверсным выходом второго цифроаналогового преобразователя и через четв.ертый ре зистор - с прямьп- выходом третьего цифроаналогового преобразователя и т.д. Сопротивления всех резисторов матрицы 4 одинаковы. Такш- образом, матрица 4 описьгоается ленточной диагональной матрицей, имеющей (п+1) столбцов и п строк. Например, для интерполирующего полинома третьей степени она имеет следующий вид: 00 -1

О

-1

5

672

Дополнительные матрицы весовых резисторов, соединяющие выходы и первые входы интегрирующих блоков двух соседних групп выполнены следующим образом. Первая выходная шина матрицы с номером i(1 i п-1) соединена через два резистора с выходами первого и второго интегрирующих блоков (1-1)-й группы интегрирующих блоков, вторая выходная шина этой матрицы соединена с выходами второго и третьего интегрир тощих блоков (|-1)-й группы интегрирующих блоков и т.д. Для интерполирующего полинома третьей степени ленточная диагональная матрица, соответствующая матрице 6, имеет три столбца и две строки, т.е. .

20

О

1

25

110, а матрица, соответствующая матрице 7, имеет два столбца и одну строку:

1

о

5

0

0

5

Вторые входы всех интегрирующих блоков 8 соединены через матрицу 5 с соответствующими выходами цифроана- логовых преобразователей. С помощью матрицы 5 формируются сигналы, амплитуды которых должны быть равны значениям сигналов на выходах интегрирующих блоков, взятых в дискретные моменты времени, при отсутствии погрешностей интегрирования. Выходы матрицы 5 делятся на п групп выходов, причем I-я группа объединяет i выходов. Способ соединения входных и выходных шин матрицы 5 с помощью весовых резисторов и выбор величины сопротивления этих резисторов зависят от величины задержки тактовых импульсов в элементе 1 задержки. Рассмотрим .организацию матрицы 5 для случая, когДа влиянием времени задержки тактовых импульсов можно пренебречь.

Первая выходная шина i-и (1 i - п) группы выходов подключена через резисторы к прямым выходам цифроана- логовых преобразователей, номера которых изменяются от 1 до (п + 1 - - 1). Вторая выходная шина подключена через резисторы к инверсным выходам цифроаналоговых преобразователей, номера которьк изменяются от 2 до (п 2 - 1)„ Третьяь выходная ши- на - к прямым выходам цифроаналоговых

3133А1

преобразователей с номерами, изменяющимися от 3 до (п + 3 - i) и т.д.

Для интерполирующего полинома третьей степени значения проводимое- тей резисторов матрицы 5 равны значениям элементов прямоугольной матрицы

Первые три строки этой матрицы соответствуют третьей группе выходов четвертая и пятая строки - второй группе выходов, а шестая строка - первой группе выходов. Значения элементов строк матрицы равны амплитудам сигналов на выходах интегрирующих блоков 8, отсчитанным в дискретные моменты времени (моменты поступления тактовых импульсов), при формировании .импульсной переходной функции устройства.

Выходы интегрирующих блоков 8 соединены с соответствующими входами сумматора 9. Коэффициенты передачи по входам этого усилителя зависят от порядка и вида интерполирующего полинома. Например, для п 3 и интерполирования на середину величины коэффициентов передачи могут имет следующие значения ,(по. порядку сверху вниз, см. чертеж):К -1/6; К -1/3; Kj -1/6; К Kj 0; К

1

На вход 10 интерполятора с периодом Т поступают коды, значения которых равны значениям отсчетов непрерывной функции. На выходе усилителя 14 слежения-хранения каждого интегрирующего блока формируется ступенчатое напряжение. Амплитуда ступеньки равна значению разности между выходным сигналом интегросумматора и сигналом, поступающим на второй вход интегрирующего блока. Запоминание амплитуды сигнала производится в момент поступления на тактовый вход тактового импульса. Таким образом, на выходе усилителя слежения-хранени

33А1

- и

10

15

20

25

30

35

в, ь 40

я

45

50

55

674

формируется сигнал ошибки интегрирования, которая в силу различных случайных факторов (дрейф нуля интегратора, помехи) может быть не равна нулю. Сигнал ошибки подается по цепи отрицательной обратной связи на второй вход интегросумматора 13. В следующем такте преобразования осуществляется процесс коррекции ошибки интегрирования. Выходной сигнал интерполятора образуется путем алгебраического суммирования выходных сигналов всех интегрирующих блоков.

Исключение возможных перегрузок по сигналам в блоках схемы обусловлено использованием принципа распределенной обработки сигналов. Так, например, однократное интегрирование третьего приращения интерполируемой функции осуществляется тремя интегрирующими блоками, двухкратное интегрирование - двумя интегрирующими блоками и т.д. Поэтому при любой форме интерполируемого сигнала амплитуда сигналов на выходах интегрирующих блоков и выходе устройства не превышает в дискретные моменты времени амплитуду интерполируемого сигнала.

Формула из Обретения

Интерполятор, содержащий основную группу из п интегрирующих блоков, первые информационные входы которых соединены с соответствующими выходами с первого по п-й первой матрицы весовых резисторов, вторые информационные входы - с соответствующими выходами с первого по п-й второй матрицы весовых резисторов, а тактовые входы - с шиной тактовых импульсов, (п+1) последовательно соединенных регистров, информационный вход первого из которых является входом интерполятора, а выход каждого регистра подключен к входу соответствующего цифроаналогового преобразователя, прямые и инверсные выходы цифроана- логовых преобразователей соединены с соответствующими входами с первого по 2(п+1)-й первой и второй матриц весовых резисторов, шина тактовых импульсов соединена через элемент задержки с входами записи регистров, а каждый интегрирующий блок содержит интегросумматор, первый вход которого является первым информационным входом блока, а выход - выходом блока и усилитель слежения-хранения, пер

5J3

вый информационный вход которого соединен с выходом интегросумматора блока, выход соединен с вторым входом интегросумматора блока, второй информационный вход является вторым информационным входом блока, а такто- вьй вход усилителя слежения-хранения является тактовым входом блока, о т- личающийся тем, что, с целью устранения возможности перегрузки при ограниченных линейных зонах блоков у интерполятор содержит сумматор, п-1 дополнительных матриц весовых резисторов и п-1 дополнитель- ных групп интегрирующих блоков, при этом каждая.-я группа, i 1, п-1, содержит п-1 интегрирующих блоков, а i-я дополнительная матрица весовых резисторов имеет n+1-i входов и п-i выходов, выходы интегрирующих блоков основной группы соединены с соответ- ст вующими входами сумматора и первой дополнительной матрицы весовых резисторов, выходы которой соединены с первыми информационными входами соот

От блокад

Фиг.2

Составитель Г„Осипов Редактор А.Ревин Техред И,Попович Корректор С.Шекмар

Заказ 3964/46 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул„Проектная,4

676

ветствующих интегрирующих блоков первой дополнительной группы, вторые информационные входы которых соединены с выходами, с (п+1)-го по {2п-1) -1)-й, второй матрицы весовых резисторов, входы каждой 1-й дополнительной матрицы весовых резисторов, i

I

2, п-1, соединены с выходами соотI

ветствзтощих интегрирующих блоков

()-й дополнительной группы, а ее выходы - с. первыми информационными входами соответствующих интегрирующих блоков i-и дополнительной , вторые информационные входы которых подключены к соответствующим выходам второй матрицы весовых резисторов, выходы интегрирующих блоков всех дополнительных групп соединены с соответствующими входами сумматора, выход которого является выходом интерполятора, а тактовые входы интегрирующих блоков дополнительных групп соединены с шиной тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1983 |

|

SU1142848A1 |

| Интерполятор | 1981 |

|

SU987634A1 |

| Линейный интерполятор | 1982 |

|

SU1075276A1 |

| Нелинейный интерполятор | 1985 |

|

SU1267446A1 |

| Линейный интерполятор | 1978 |

|

SU698012A1 |

| Устройство для многоканального интерполирования функций | 1986 |

|

SU1377878A1 |

| Устройство для восстановления непрерывных функций по дискретным отсчетам | 1983 |

|

SU1125632A1 |

| Полиномиальный интерполятор | 1983 |

|

SU1239732A1 |

| Функциональный преобразователь | 1983 |

|

SU1145353A1 |

| Параболический интерполятор | 1986 |

|

SU1399778A2 |

Изобретение относится к вычислительной технике и может быть исполь- зовано в устройствах обработки дискретных данных. Цель изобретения - устранение возможности перегрузки при ограниченных линейных зонах блоков. Интерполятор содержит элемент задержки 1, регистры , цифро- аналоговые преобразователи 3,-3 , первую 4 и вторую 5 матрицы весовых резисторов, дополнительные матрицы весовых резисторов 6,7-, интегрирующие блоки 8, сумматор 9, вход 10, выход 11, шину 12 тактовых импульсов. Последовательность входных отсчетов, поступающая на вход интерполятора, используется для формирования интерполирующего полинома. Конечные разности соответствующего порядка интегрируются в группах интегрирующих блоков. Для предотвращения перегрузок используется принцип распределения обработки. Результаты интегрирования суммируются. В схеме предусмотрена компенсация погрешностей . 2 ил. i (Л «72 ff. со со 4; С5 r--4L.-L---ir: :i L---- , . Фиг. Г

| Параболический интерполятор | 1982 |

|

SU1070573A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Интерполятор | 1981 |

|

SU987634A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-30—Публикация

1986-04-07—Подача