I

Изобретение относится к вычисли- тельной технике и предназначено для использования в составе электронных вычислительных устройств.

Целью изобретения является повышение быстродействия устройства для деления за счет предварительной оден ки отдельных разрядов частного с последующей (в случае необходимости) коррекцией найденных разрядов.

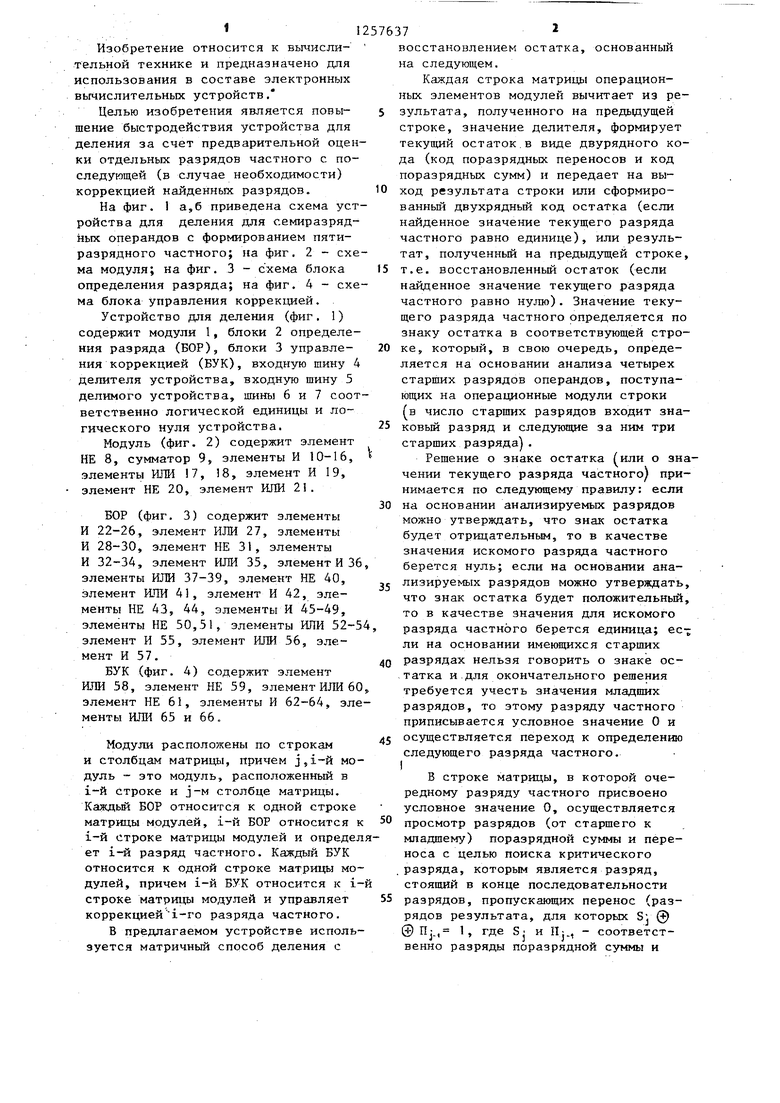

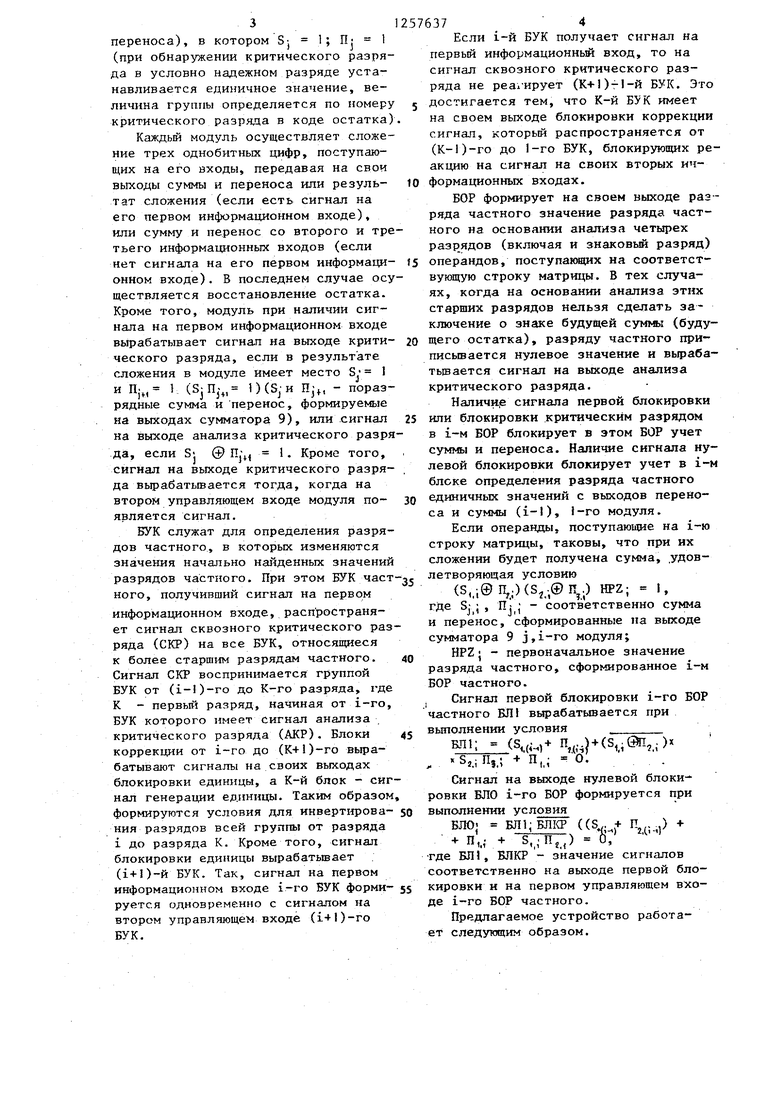

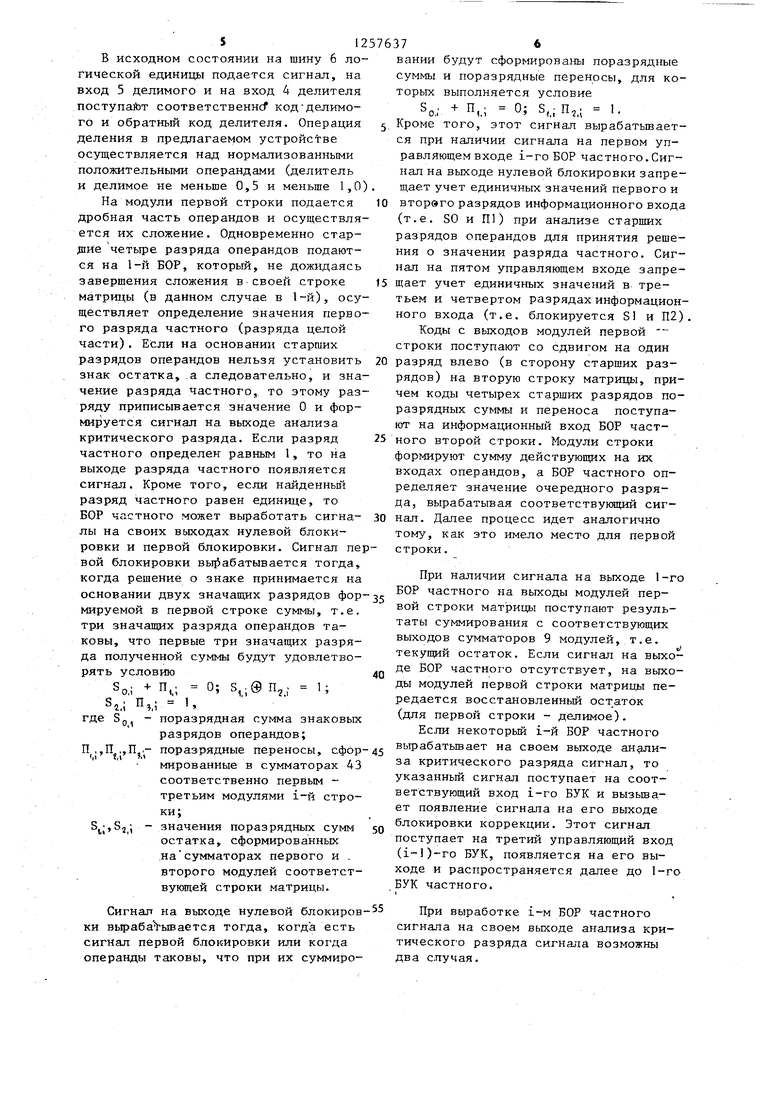

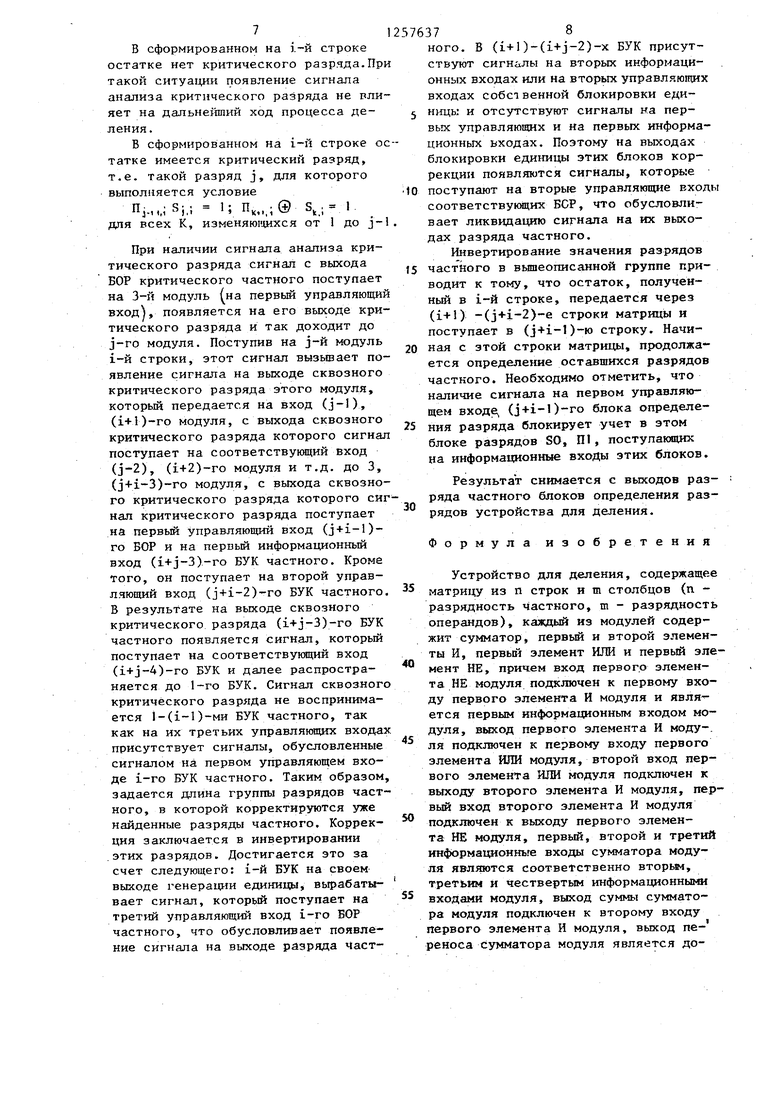

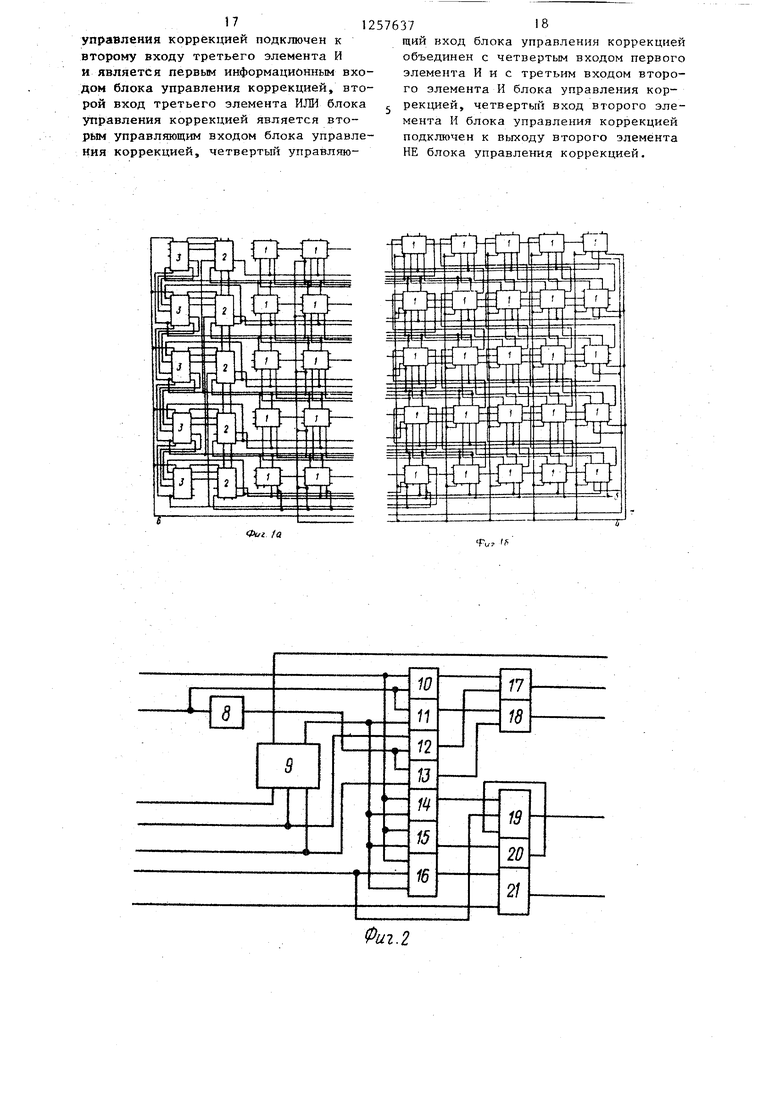

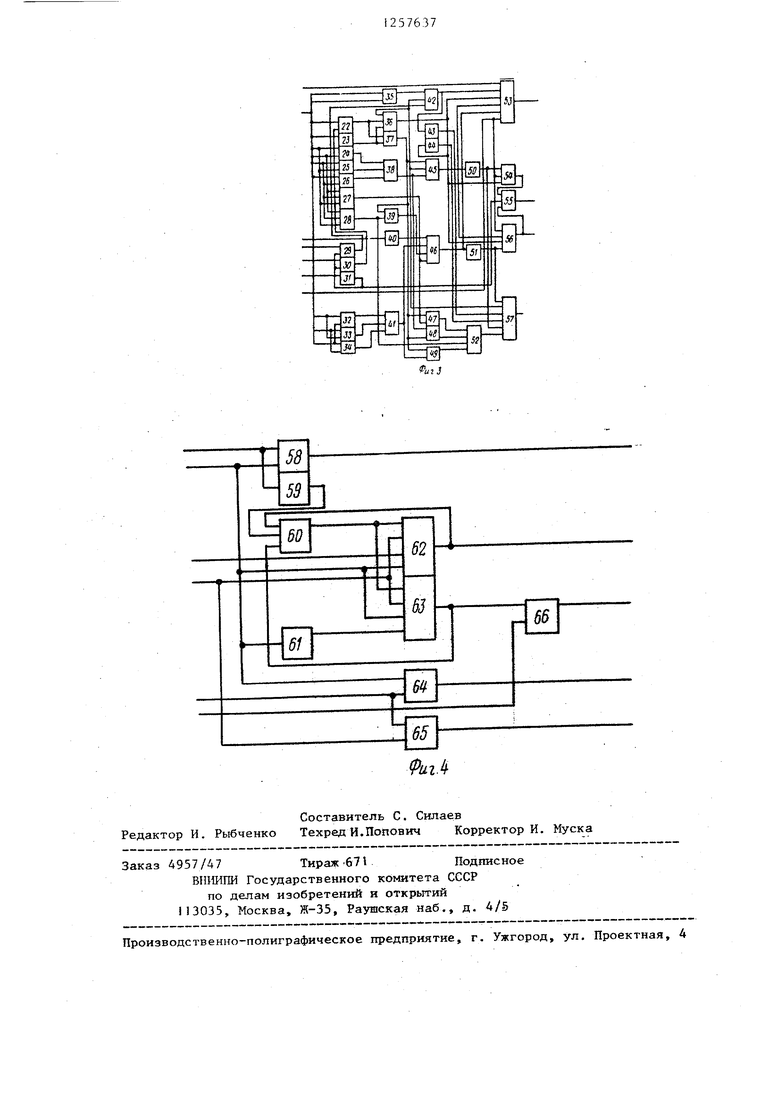

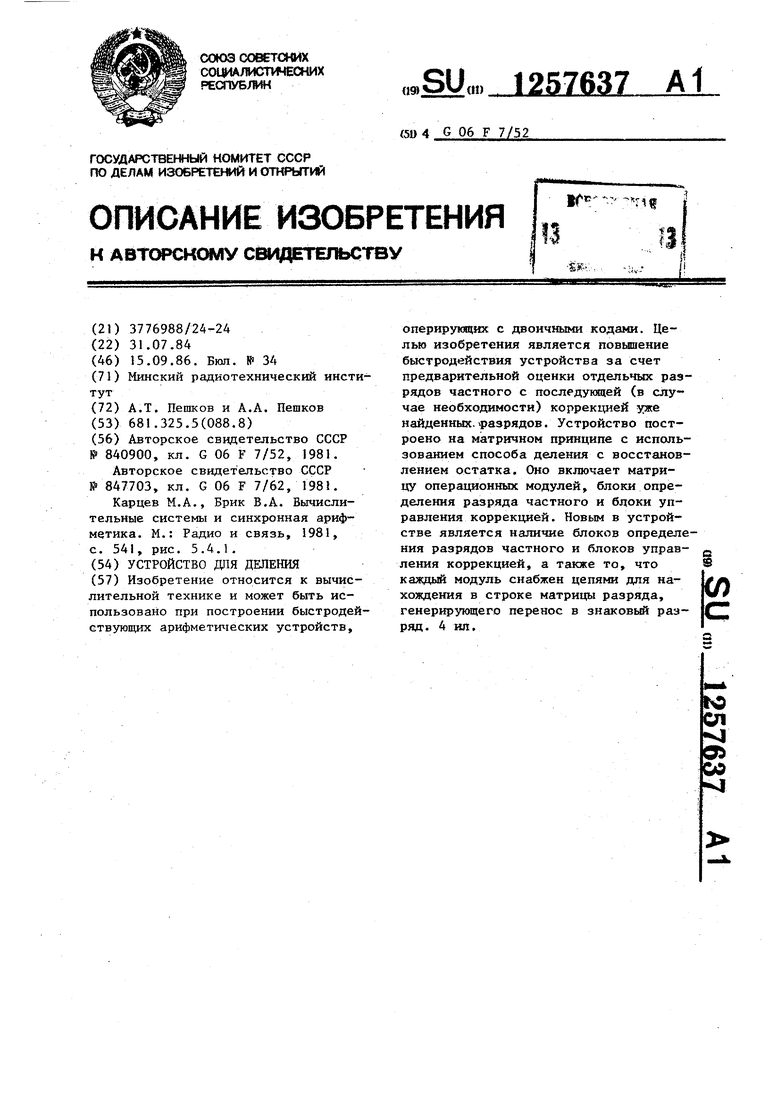

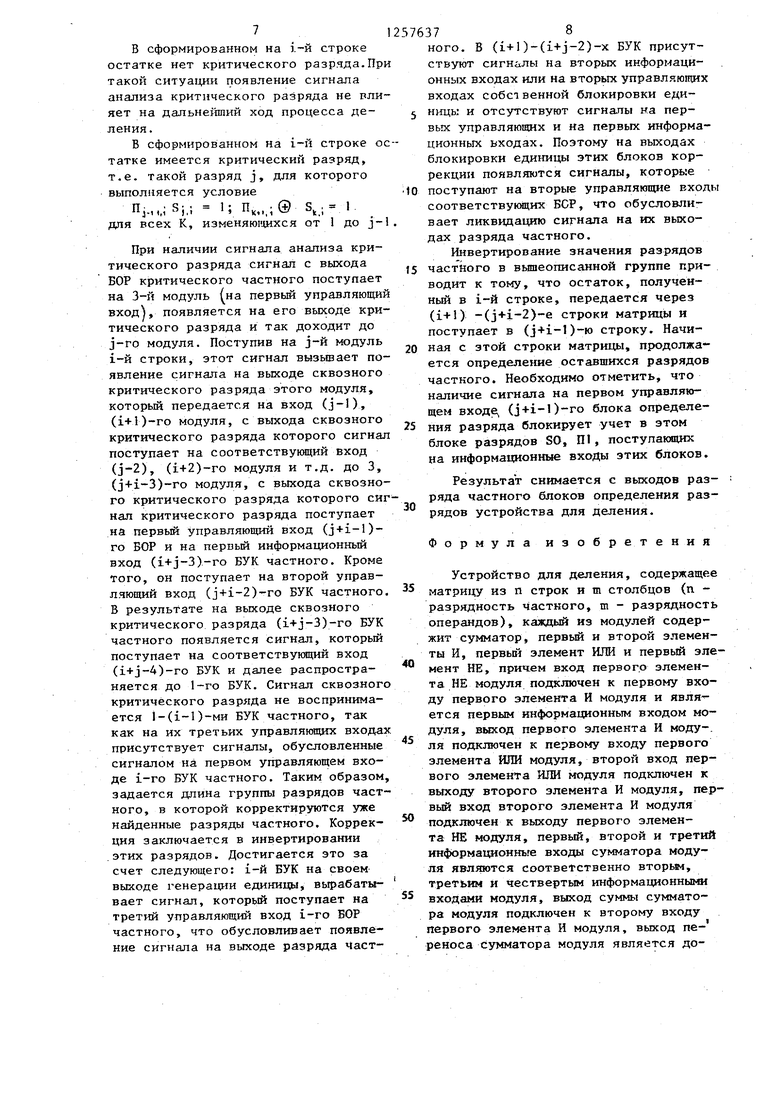

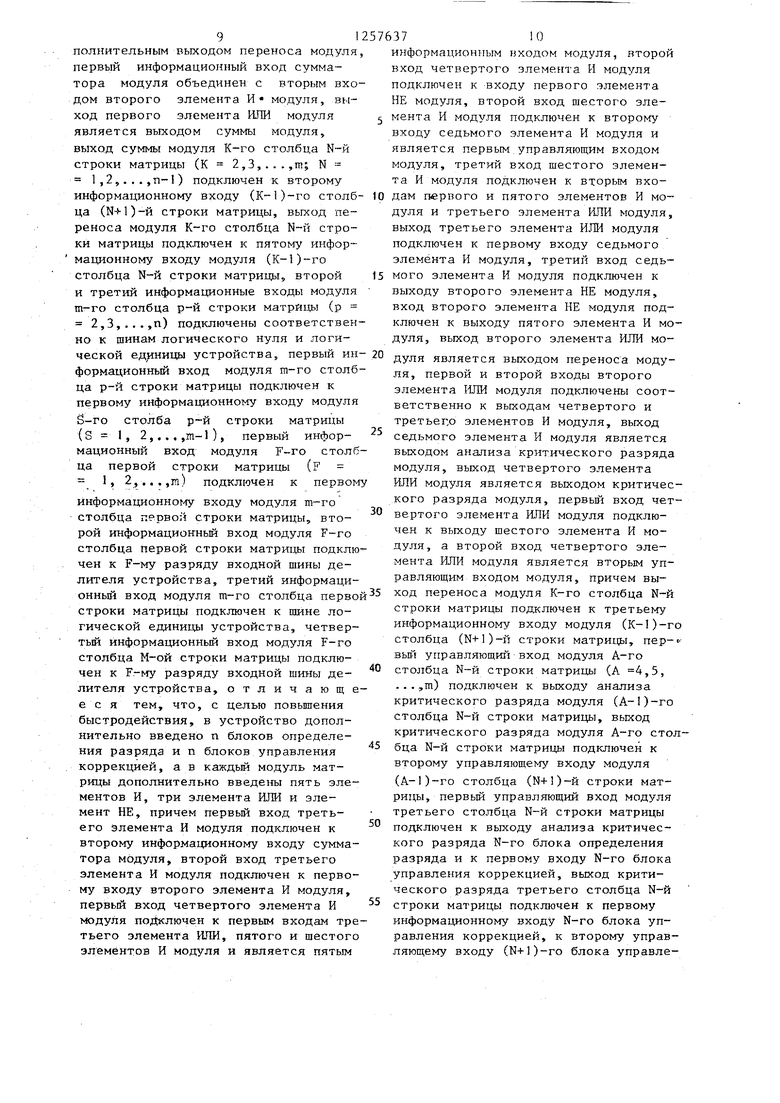

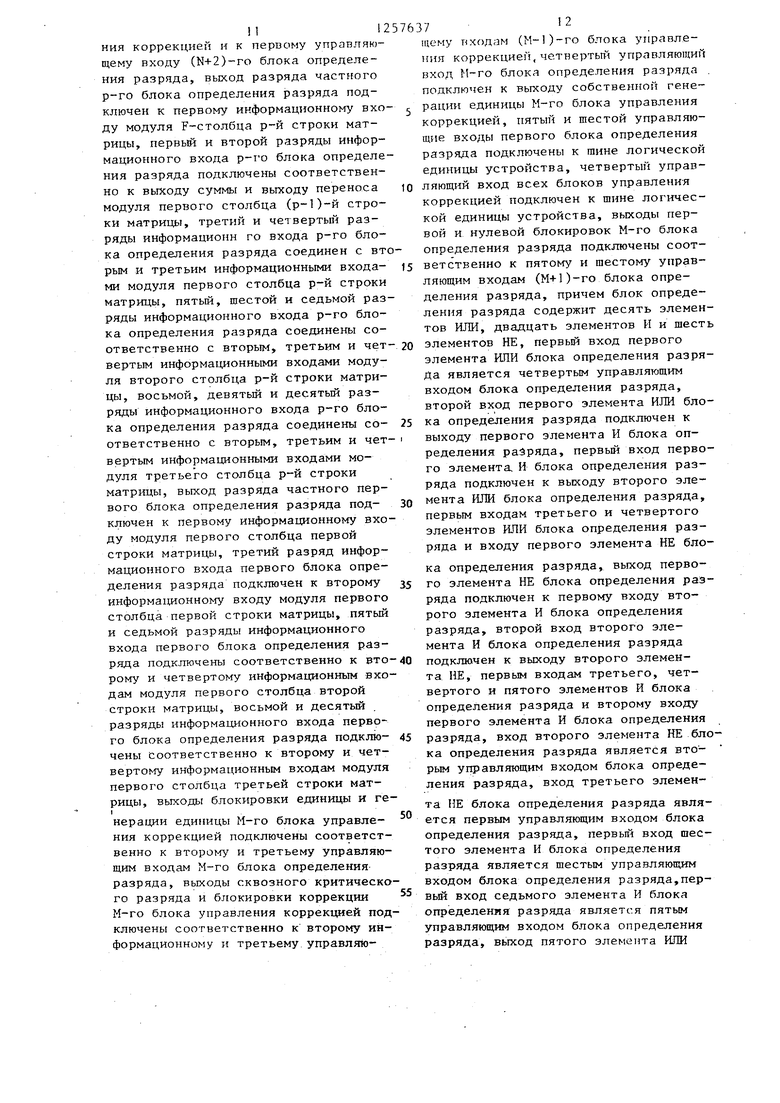

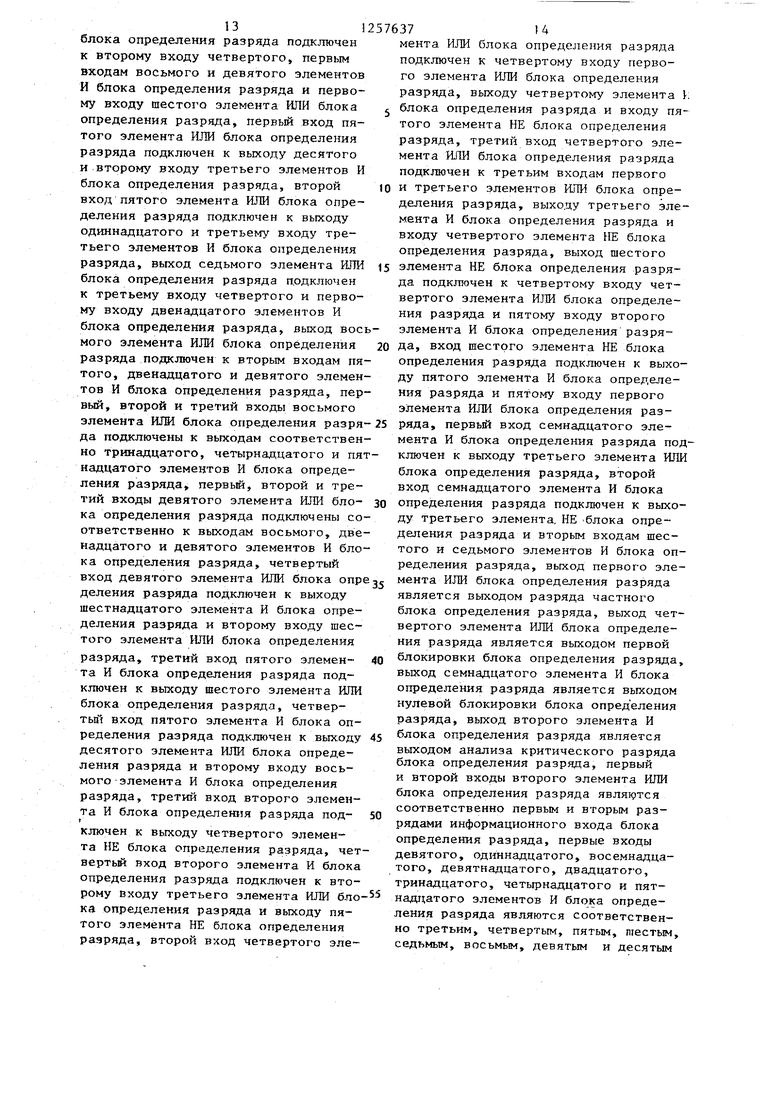

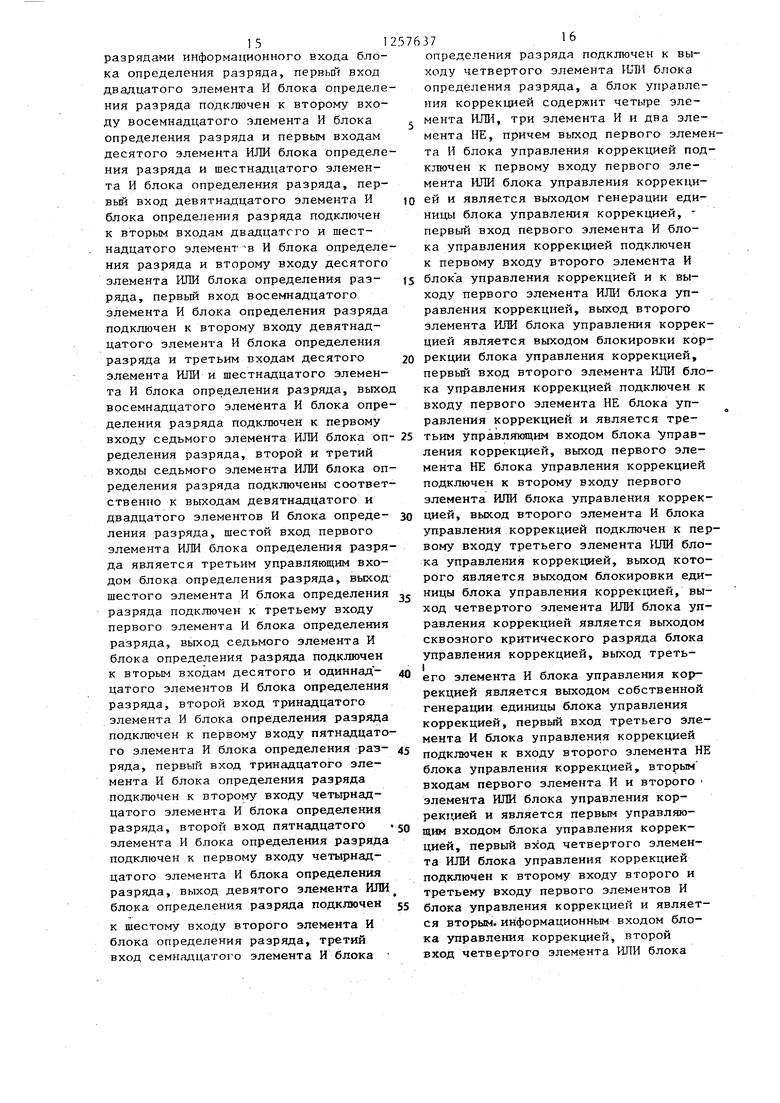

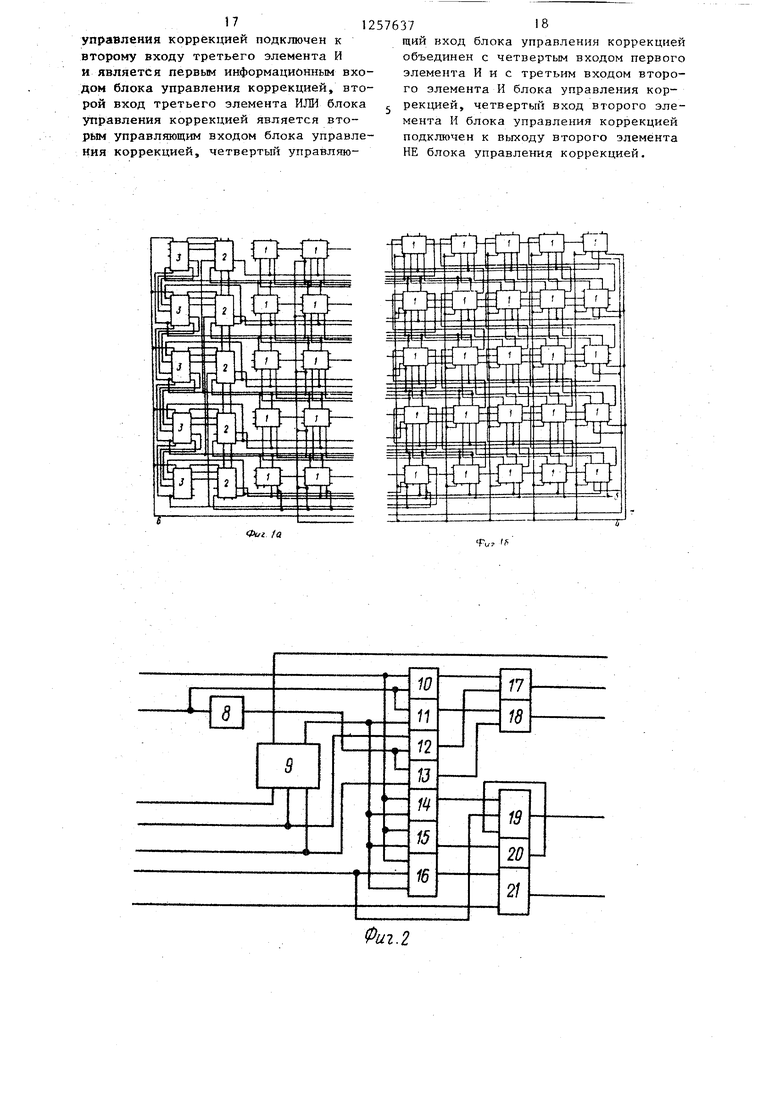

На фиг. 1 а,б приведена схема устройства для деления для семиразрядных операндов с формированием пятиразрядного частного; на фиг. 2 - схема модуля; на фиг. 3 - схема блока определения разряда; на фиг. 4 - схема блока управления коррекцией.

Устройство для деления (фиг, 1) содержит модули 1, блоки 2 определения разряда (БОР), блоки 3 управления коррекцией (БУК), входную шину 4 делителя устройства, входную шину 5 делимого устройства, шины 6 и 7 соответственно логической единицы и логического нуля устройства.

Модуль (фиг. 2) содержит элемент НЕ 8, сумматор 9, элементы И 10-16, элементы ИЛИ 17, 8, элемент И 19, элемент НЕ 20, элемент ИЛИ 2).

1

БОР (фиг. 3) содержит элементы И 22-26, элемент ИЛИ 27, элементы И 28-30, элемент НЕ 31, элементы И 32-34, элемент ИЛИ 35, элемент И 36, элементы ИЛИ 37-39, элемент НЕ 40, элемент ИЛИ 41, элемент И 42, элементы НЕ 43, 44, элементы И 45-49, элементы НЕ 50,51,, элементы ИЛИ 52-54 элемент И 55, элемент ИЛИ 56, элемент И 57.

БУК (фиг. 4) содержит элемент ИЛИ 58, элемент НЕ 59, элемент ИЛИ 60, элемент НЕ 61, элементы И 62-64, элементы ИЛИ 65 и 66.

Модули расположены по строкам и столбцам матрицы, причем ,1-й модуль - это модуль, расположенный в i-й строке и J-M столбце матрицы. Каждый ВОР относится к одной строке матрицы модулей, i-й БОР относится к i-й строке матрицы модулей и определяет i-й разряд частного. Каждый БУК относится к одной строке матрицы модулей, причем i-й БУК относится к i-й строке матрицы модулей и управляет коррекцией i-ro разряда частного.

В предлагаемом устройстве используется матричный способ деления с

, 4,

2576372

восстановлением остатка, основанный на следующем.

Каждая строка матрицы операционных элементов модулей вычитает из ре5 зультата, полученного на предьщущей строке, значение делителя, формирует текущий остаток.в виде двурядного кода (код поразрядных переносов и код поразрядных сумм) и передает на вы10 ход результата строки или сформированный двухрядный код остатка (если найденное значение текущего разряда частного равно единице), или результат, полученный на предыдущей строке,

15 т.е. восстановленный остаток (если найденное значение текущего разряда частного равно нулю). Значение текущего разряда частного определяется по знаку остатка в соответствующей стро20 ке, который, в свою очередь, определяется на основании анализа четырех старших разрядов операндов, поступающих на операционные модули строки в число старших разрядов входит зна25 ковьй разряд и следующие за ним три старших разряда).

Решение о знаке остатка (или о значении текущего разряда частного) принимается по следующему правилу: если

30 на основании анализируемых разрядов

5

0

5

0

5

можно утверждать, что знак остатка будет отрицательным, то в качестве значения искомого разряда частного берется нуль; если на основании анализируемых разрядов можно утверждать, что знак остатка будет положительный, то в качестве значения для искомого разряда частного берется единица; ес ли на основании имеющихся старших разрядах нельзя говорить о знаке остатка и для окончательного решения требуется учесть значения младших разрядов, то этому разряду частного приписывается условное значение О и осуществляется переход к определению следующего разряда частного. I

В строке матрицы, в которой очередному разряду частного присвоено условное значение О, осуществляется просмотр разрядов (от старшего к младшему) поразрядной суммы и переноса с целью поиска критического разряда, которым является разряд, стоящий в конце последовательности разрядов, пропускающих перенос (раз.J

рядов результата, для которых S @ nj., 1, где Sj и П-., - соответственно разряды поразрядной суммы и

переноса), в котором Sj 1; П: 1 (при обнаружении критического разряда в условно надежном разряде устанавливается единичное значение, величина группы определяется по номеру критического разряда в коде остатка) Каждый модуль осуществляет сложение трех однобитных цифр, поступающих на его входы, передавая на свои выходы суммы и переноса или результат сложения (если есть сигнал на его первом информационном входе), или сумму и перенос со второго и третьего информационных входов (если нет сигнала на его первом информаци- онном входе), В последнем случае осуществляется восстановление остатка. Кроме того, модуль при наличии сигнала на первом информационном входе вырабатывает сигнап на выходе критического разряда, если в результате сложения в модуле имеет место S 1 и П., К Sjnj+. П( nj, - поразрядные сумма и перенос, формируемые на выходах сумматора 9), или сигнал на выходе анализа критического разряда, если S , ® П,-ц 1. Кроме того.

если S; ® П-4 1. J

сигнал на выходе критического разряда вь1рабатьтается тогда, когда на

втором управляющем входе модуля появляется сигнал.

БУК служат для определения разрядов частного, в которых изменяются значения начально найденных значений

разрядов частного. При этом БУК час ного, получивший сигнал на первом

информационном входе, распространяет сигнал сквозного критического раряда (СКР) на все БУК, относящиеся к более старшим разрядам частного. Сигнал СКР воспринимается группой БУК от (i-l)-ro до К-го разряда, гд К - первый разряд, начиная от i-ro БУК которого имеет сигнал анализа критического разряда (АКР). Блоки коррекции от i-ro до (К+1)-го вьфа- батывают сигналы на своих выходах блокировки единицы, а К-й блок - СИ нал генерации единицы. Таким образо формируются условия для инвертирова ния разрядов всей группы от разряда i до разряда К. Кроме того, сигнал блокировки единицы вырабатьшает (i+l)-й БУК. Так, сигнал на первом информационном входе i-ro БУК форми руется одновременно с сигналом на втором управляющем входе ()-ro БУК.

637 4

Если i-й БУК получает сигнал на первьй информационньй вход, то на сигнал сквозного критического разряда не реа1 ирует (К+1)г1-й БУК. Это достигается тем, что К-й БУК имеет на своем выходе блокировки коррекции сигнап, который распространяется от (K-l)-ro до 1-го БУК, блокирующих реакцию на сигнал на своих вторых ич- формационных входах.

БОР формирует на своем выходе разряда частного значение разряда частного на основании анализа четырех разрядов (включая и знаковый разряд) операндов, поступающих на соответствующую строку матрицы. В тех случаях, когда на основании анализа этих старших разрядов нельзя сделать заключение о знаке будущей (будущего остатка), разряду частного приписывается нулевое значение и вьфаба- тывается сигнал на выходе анализа критического разряда.

Наличир сигнала первой блокировки или блокировки критическим разрядом в i-M БОР блокирует в этом БОР учет суммы и переноса. Наличие сигнала нулевой блокировки блокирует учет в i-M блоке определения разряда частного единичных значений с выходов переноса и суммы (i-l), 1-го модуля.

Если операнды, поступающие на i-ю строку матрицы, таковы, что при их сложении будет получена сумма, .удов

летворяюцая условию « . „ .

(S,,i® П,.)(8,.,®П.) HPZ; I, где S; j , E . - соответственно сумма и перенос, сформированные на выходе сумматора 9 j,i-ro модуля;

HPZ; - первоначальное значение разряда частного, сформированное i-м БОР частного.

I Сигнал первой блокировки i-ro БОР частного БЛ1 вырабатывается при выполнении условия

БЛ1;

+

«Ss.i Щ.

SI.M (,4).,,;)

П

t:

О.

Сигнал на выходе нулевой блокировки БЛО i-ro БОР формируется при выполнении условия

БЛО; БЛ1; БЛКР ((S . + П . ) +

tn - S,;nj) О, где БЛ1, БЛКР - значение сигналов соответственно на выходе первой блокировки и на первом управляющем входе i-ro БОР частного.

Предлагаемое устройство работает следующим образом.

В исходном состоянии на шину 6 логической единицы подается сигнал, на вход 5 делимого и на вход 4 делителя поступает cooTBeTCTBeHHcf код делимого и обратный код делителя. Операция деления в предлагаемом устройстве осуществляется над нормализованными положительными операндами (делитель и делимое не меньше 0,5 и меньше 1,0)

На модули первой строки подается дробная часть операндов и осуществляется их сложение. Одновременно стар- дпие четыре разряда операндов подаются на 1-й БОР, который, не дожидаясь завершения сложения в-своей строке матрицы (в данном случае в 1-й), осуществляет определение значения первого разряда частного (разряда целой части). Если на основании старших

вании будут сформированы поразрядные суммы и поразрядные переносы, для которых выполняется условие

S.;, - П,.; 0; 5,,;П,,; 1.

5 Кроме того, этот сигнал вырабатывается при наличии сигнала на первом управляющем входе i-ro БОР частного.Сигнал на выходе нулевой блокировки запрещает учет единичных значений первого и

10 вторэго разрядов информационного входа (т.е. SO и П1) при анализе старших разрядов операндов для принятия решения о значении разряда частного. Сигнал на пятом управляющем входе запре15 щает учет единичных значений в третьем и четвертом разрядах информационного входа (т.е. блокируется S1 и П2). Коды с выходов модулей первой

строки поступают со сдвигом на один разрядов операндов нельзя установить 20 разряд влево (в сторону старших раз- знак остатка, ,а следовательно, и зна- рядов) на вторую строку матрицы, при- чение разряда частного, то этому раз- чем коды четырех старших разрядов поразрядных суммы и переноса поступают на информационный вход БОР част- 25 кого второй строки. Модули строки формируют сумму действующих на их

30

ряду приписывается значение О и формируется сигнал на выходе анализа критического разряда. Если разряд частного определен равным 1, то на выходе разряда частного появляется сигнал. Кроме того, если найденньп разряд частного равен единице, то БОР частного может выработать сигналы на своих выходах нулевой блокировки и первой блокировки. Сигнал первой блокировки вырабатывается тогда, когда решение о знаке принимается: на основании двух значаш 1х разрядов фор- 35 мируемой в первой строке суммы, т.е. три значащих разряда операндов таковы, что первые три значащих разряда полученной суммы будут удовлетворять условию

40

входах операндов, а БОР частного определяет значение очередного разряда, вырабатывая соответствукшщй сигнал. Далее процесс идет аналогично тому, как это имело место для первой строки.

При наличии сигнала на выходе 1го БОР частного на выходы модулей первой строки матрицы поступают результаты суммирования с соответствующих выходов сумматоров 9 модулей,,т.е. текущий остаток. Если сигнал на выходе БОР частного отсутствует, на выходы модулей первой строки матрицы передается восстановленный (для первой строки - делимое).

где

,; S,. П

SOH

+ П,

При наличии сигнала на выходе 1БОР частного на выходы модулей первой строки матрицы поступают резуль таты суммирования с соответствующих выходов сумматоров 9 модулей,,т.е. текущий остаток. Если сигнал на вых де БОР частного отсутствует, на вых ды модулей первой строки матрицы пе редается восстановленный (для первой строки - делимое).

Если некоторый i-й БОР частного

П,,; П,;,П,.

,„ 0; S,i@n,,. 1;

,,; .

- поразрядная сумма знаковых разрядов операндов; поразрядные переносы, сфор-45 ырабатьтает на своем выходе аналимированные в сумматорах 43 соответственно первым - третьим модулями i-й строки;

,Sj; - значения поразрядных сумм $0 остатка, сформированных на сумматорах первого и . второго модулей соответствующей строки матрицы.

Сигнал на выходе нулевой блокиров-55 ки вь1раба ьшается тогда, когда есть сигнал первой блокировки или когда операнды таковы, что при их суммироза критического разряда сигнал, то указанный сигнал поступает на соответствующий вход i-ro БУК и вызьша- ет появление сигнала на его выходе блокировки коррекции. Этот сигнал поступает на третий управляющий вход (i-)-ro БУК, появляется на его выходе и распространяется далее до 1-г БУК частного.

При выработке i-м БОР частного сигнала на своем выходе анализа кри тическог о разряда сигнала возможны два случая.

вании будут сформированы поразрядные суммы и поразрядные переносы, для которых выполняется условие

S.;, - П,.; 0; 5,,;П,,; 1.

Кроме того, этот сигнал вырабатывается при наличии сигнала на первом управляющем входе i-ro БОР частного.Сигнал на выходе нулевой блокировки запрещает учет единичных значений первого и

вторэго разрядов информационного входа (т.е. SO и П1) при анализе старших разрядов операндов для принятия решения о значении разряда частного. Сигнал на пятом управляющем входе запрещает учет единичных значений в третьем и четвертом разрядах информационного входа (т.е. блокируется S1 и П2). Коды с выходов модулей первой

входах операндов, а БОР частного определяет значение очередного разряда, вырабатывая соответствукшщй сигнал. Далее процесс идет аналогично тому, как это имело место для первой строки.

При наличии сигнала на выходе 1го БОР частного на выходы модулей первой строки матрицы поступают результаты суммирования с соответствующих выходов сумматоров 9 модулей,,т.е. текущий остаток. Если сигнал на выходе БОР частного отсутствует, на выходы модулей первой строки матрицы передается восстановленный (для первой строки - делимое).

Если некоторый i-й БОР частного

ырабатьтает на своем выходе анализа критического разряда сигнал, то указанный сигнал поступает на соответствующий вход i-ro БУК и вызьша- ет появление сигнала на его выходе блокировки коррекции. Этот сигнал поступает на третий управляющий вход (i-)-ro БУК, появляется на его выходе и распространяется далее до 1-г БУК частного.

При выработке i-м БОР частного сигнала на своем выходе анализа кри- тическог о разряда сигнала возможны два случая.

в сформированном на 1-й строке остатке нет критического разряда.При такой ситуации появление сигнала анализа критического разряда не РЛИ- яет на дальне1ший ход процесса деления.

В сформированном на i-й строке ос татке имеется критический разряд, т.е. такой разряд j, для которого выполняется условие

П.,,,; Sj,; 1; П,„,;@ S,,; 1 для всех К, изменяюгчихся от 1 до j-i

При наличии сигнала анализа критического разряда сигнал с выхода БОР критического частного поступает на 3-й модуль (на первый управляющий вход, появляется на его выходе критического разряда и так доходит до j-ro модуля. Поступив на j-й модуль i-й строки, этот сигнал вызьшает появление сигнала на выходе сквозного критического разряда этого модуля, который передается на вход (j-t), ()-ro модуля, с выхода сквозного критического разряда которого сигнал поступает на соответствующий вход (J-2), (i+2)-ro модуля и т.д. до 3, (j+i-3)-ro модуля, с выхода сквозного критического разряда которого сигнал критического разряда поступает на первый управляющий вход (j+i-1)- го ВОР и на первьй информационный вход (i+j-3)-ro БУК частного. Кроме Того, он поступает на второй управляющий вход (j+i-2)-ro БУК частного. В результате на выходе сквозного критического разряда (i+j-3)-ro БУК частного появляется сигнал, который поступает на соответствующий вход (i+j-4)-ro БУК и далее распространяется до 1-го БУК. Сигнал сквозного критического разряда не воспринимается 1-(1-1)-ми БУК частного, так как На их третьих управлякяцих входах присутствует сигналы, обусловленные сигналом на первом управляющем входе i-ro БУК частного. Таким образом, задается длина группы разрядов частного, в которой корректируются уже найденные разряды частного. Коррекция заключается в инвертировании .этих разрядов. Достигается это за счет следующего: i-й БУК на своем выходе генерации единицы, вырабаты- вает сигнал, которьй поступает на третий управляющий вход i-ro БОР частного, что обусловливает появление сигнала на выходе разряда Част576378

кого. В (i+l)-(i+j-2)-x БУК присутствуют сигналы на вторых информационных входах или на вторых управляющих входах собст венной блокировки еди- 5 ницы и отсутствуют сигналы на первых управляющих и на первых информационных ьходах. Поэтому на выходах блокировки единицы этих блоков коррекции появляются сигналы, которые

10 поступают на вторые управляющие входы соответствукицих БСР, что обусловливает ликвидацию сигнала на их выходах разряда частного.

Инвертирование значения разрядов

15 частного в вышеописанной группе приводит к тому, что остаток, полученный в i-й строке, передается через (i+1) -(j+i-2)-e строки матрицы и поступает в ()-ю строку. Начи20 ная с этой строки матрицы, продолжа ется определение оставшихся разрядов частного. Необходимо отметить, что наличие сигнала на первом управляющем входе;, (j+i-l)-ro блока определе 5 НИН разряда блокирует учет в этом блоке разрядов SO, П1, поступающих на информационные входы этих блоков.

Результат снимается с выходов разряда частного блоков определения разрядов устройства для деления.

Формула изобретения

Устройство для деления, содержащее матрицу из п строк и m столбцов (п - разрядность частного, m - разрядность операндов), каждый из модулей содержит сумматор, первый и второй элементы И, первый элемент ИЛИ и первый элемент НЕ, причем вход первого элемента НЕ модуля подключен к первому входу первого элемента И модуля и явля ется первым информационным входом модуля, выход первого элемента И моду-, ля подкдпочен к первому входу первого элемента ИЛИ модуля, второй вход первого элемента ИЛИ модуля подключен к выходу второго элемента И модуля, первый вход второго элемента И модуля подключен к выходу первого элемента НЕ модуля, первый, второй и третий информационные входы сумматора модуля являются соответственно вторьм, третьим и чествертьм инфopмaциoнны ш входами модуля, выход суммы сумматора модуля подключен к второму входу первого элемента И модуля, выход пе- реноса сумматора модуля является до

полнительным выходом переноса модуля, первый информационный вход сумматора модуля объединен с вторым входом второго элемента И« модуля, выход первого элемента ИЛИ модуля является выходом суммы модуля выход суммы модуля К-го столбца N-й строки матрицы (К 2,3,..,,т; N 1,2,...,п-) подключен к второму

15

информационному входу (K-l)-ro столб- 10 дам первого и пятого элементов И мо- ца (Н+1)-й строки матрицы, выход переноса модуля К-го столбца N-й строки матрицы подключен к пятому информационному входу модуля (K-l)-ro столбца N-й строки матрицы, второй и третий информационные входы модуля т-го столбца р-й строки матрицы (р 2,3,...,п) подключены соответственно к шинам логического нуля и логической единицы устройства, первый ин- 20 формационный вход модуля т-го столбца р-й строки матрицы подключен к первому информационному входу модуля S-ro столба р-й строки матрицы {S 1, 2,..,,m-l), первый инфор мационный вход модуля F-ro столбца первой строки матрицы (F 1, 2,...,га) подключен к первому

информационног-1у входу модуля т-го столбца первой строки матрицы, второй информационньй вход модуля F-ro столбца первой строки матршда подключен к F-му разряду входной шины делителя устройства, третий информаци-,- 25

30

дуля и третьего элемента ИЛИ модуля, выход третьего элемента ИЛИ модуля подключен к первому входу седьмого элемента И модуля, третий вход седьмого элемента И модуля подключен к выходу второго элемента НЕ модуля, вход второго элемента НЕ модуля подключен к выходу пятого элемента И модуля, выход второго элемента ИЛИ модуля является выходом переноса модуля, первой и второй входы второго элемента ИЛИ модуля подключены соответственно к выходам четвертого и третьег,о элементов И модуля, выход седьмого элемента И модуля является вькодом анализа критического разряда модуля, выход четвертого элемента ИЛИ модуля является выходом критического разряда модуля, первьй вход четвертого элемента ИЛИ модуля подключен к выходу шестого элемента И модуля, а второй вход четвертого элемента ИЛИ модуля является вторым управляющим входом модуля, причем выонньй вход модуля т-го столбца первой З ход переноса модуля К-го столбца N-й

строки матрицы подключен к пшне логической единицы устройства, четвертый информационный вход модуля F-ro столбца М-ой строки матрицы подключен к F-му разряду входной шины делителя устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство дополнительно введено п блоков определения разряда и п блоков управления коррекцией, а в каждьй модуль матрицы дополнительно введены пять элементов И, три элемента ИЛИ и элемент НЕ, причем первьй вход третьего элемента И модуля подключен к второму информационному входу сумматора модуля, второй вход третьего элемента И модуля подключен к первому входу второго элемента И модуля, первьй вход четвертого элемента И модуля подключен к первым входам третьего элемента ШШ, пятого и шестого элементов И модуля и является пятым

информационным входом модуля, второй вход четвертого элемента И модуля подключен к входу первого элемента НЕ модуля, второй вход шестого элемента И модуля подключен к второму входу седьмого элемента И модуля и является первым,управляющим входом модуля, третий вход шестого элемента И модуля подключен к вторым вхо

ам первого и пятого элементов И мо-

уля и третьего элемента ИЛИ модуля, выход третьего элемента ИЛИ модуля подключен к первому входу седьмого элемента И модуля, третий вход седьмого элемента И модуля подключен к выходу второго элемента НЕ модуля, вход второго элемента НЕ модуля подключен к выходу пятого элемента И модуля, выход второго элемента ИЛИ модуля является выходом переноса модуля, первой и второй входы второго элемента ИЛИ модуля подключены соответственно к выходам четвертого и третьег,о элементов И модуля, выход седьмого элемента И модуля является вькодом анализа критического разряда модуля, выход четвертого элемента ИЛИ модуля является выходом критического разряда модуля, первьй вход четвертого элемента ИЛИ модуля подключен к выходу шестого элемента И модуля, а второй вход четвертого элемента ИЛИ модуля является вторым управляющим входом модуля, причем вы

строки матрицы подключен к третьему информационному входу модуля (K-I)-ro столбца (М+1)-й строки матрицы, пер-«- вьй управляющий вход модуля А-го столбца N-и строки матрицы (А 4,5, .....т) подключен к выходу анализа критического разряда модуля (A-I)-ro столбца N-й строки матрицы, выход критического разряда модуля А-го столбца N-й строки матрицы подключен к второму управляющему входу модуля (А-)-го столбца (N+l)-й строки матрицы, первьй управляющий вход модуля третьего столбца N-й строки матрицы подключен к выходу анализа критического разряда N-ro блока определения разряда и к первому входу N-ro блока управления коррекцией, выход критического разряда третьего столбца N-й строки матрицы подключен к первому информационному входу N-ro блока управления коррекцией, к второму управляющему входу (N+)-ro блока управления коррекцией и к первому управляющему входу (N+2)-ro блока определения разряда, выход разряда частного р-го блока определения разряда подключен к первому информационно гу вхо ду модуля F-столбца р-й строки матрицы, первый и второй разряды информационного входа р-го блока определения разряда подключены соответственно к выходу суммы и выходу переноса модуля первого столбца (р-1)-й строки матрицы, третий и четвертый разряды информационн го входа р-го блока определения разряда соединен с втрым и третьим информационными входа- ми модуля первого столбца р-й строки матрицы, пятый, шестой и седьмой разряды информационного входа р-го блока определения разряда соединены соответственно с вторым, третьим и чет вертым информационными входами модуля второго столбца р-й строки матрицы, восьмой, девятьш и десятый разряды информационного входа р-го блока определения разряда соединены со- ответственно с вторым, третьим и чет вертым информационными входами модуля третьего столбца р-й строки матрицы, выход разряда частного первого блока определения разряда под- ключей к первому информационному входу модуля первого столбца первой строки матрицы, третий разряд информационного входа первого блока определения разряда подключен к второму информа1щонному входу модуля первого столбца первой строки матрицы, пятый и седьмой разрядь информационного входа первого блока определения разряда подключены соответственно к вто- рому и четвертому информационным входам модуля первого столбца второй строки матрицы, восьмой и десятый разряды информационного входа первого блока определения разряда подклю- чены Соответственно к второму и чет- вepтo fy информационным входам модуля первого столбца третьей строки матрицы, выходы блокировки единицы и ге1цему входам (M-l)-ro блока управления коррекцией,четвертьп управляющи вход М-го блока определения разряда подключен к выходу собственной гене рации единицы М-го блока управления коррекцией, пятый и шестой управляю щие входы первого блока определения разряда подключены к шине логическо единицы устройства, четвертый управ ляющий вход всех блоков управления коррекцией подключен к шине логичес кой единицы устройства, выходы первой и нулевой блокировок М-го блока определения разряда подключены соот ветственно к пятому и шестому управ ляющим входам ()-го блока определения разряда, причем блок опреде ления разряда содержит десять элеме тов ИЛИ, двадцать элементов И и шес элементов НЕ, первый вход первого элемента ИЛИ блока определения разр да является четвертым управляющим входом блока определения разряда, второй вход первого элемента ИЛИ бло ка определения разряда подключен к выходу первого элемента И блока определения разряда, первьй вход перво го элемента, И блока определения разряда подключен к выходу второго элемента iЛИ блока определения разряда, первым входам третьего и четвертого элементов ИЛИ блока определения разряда и входу первого элемента НЕ бло ка определения разряда, выход первого элемента НЕ блока определения раз ряда подключен к первому входу второго элемента И блока определения разряда, второй вход второго элемента И блока определения разряда подключен к выходу второго элемента НЕ, nepBEJM входам третьего, четвертого и пятого элементов И блока определения разряда и второму входу первого элемента И блока определения разряда, вход второго элемента НЕ бл ка определения разряда является вторым ущ)авляющим входом блока определения разряда, вход третьего элемента НЕ блока определения разряда явля

нерации единицы М-го блока управле- ется первым управляющим входом блока

ния коррекцией подключены соответственно к второму и третьему управляющим входам М-го блока определения- разряда, выходы сквозного критического разряда и блокировки коррекции М-го блока управления корректней подключены соответственно к второму информационному и третьему управляю1цему входам (M-l)-ro блока управления коррекцией,четвертьп управляющий вход М-го блока определения разряда подключен к выходу собственной генерации единицы М-го блока управления коррекцией, пятый и шестой управляющие входы первого блока определения разряда подключены к шине логической единицы устройства, четвертый управляющий вход всех блоков управления коррекцией подключен к шине логической единицы устройства, выходы первой и нулевой блокировок М-го блока определения разряда подключены соответственно к пятому и шестому управляющим входам ()-го блока определения разряда, причем блок определения разряда содержит десять элементов ИЛИ, двадцать элементов И и шест элементов НЕ, первый вход первого элемента ИЛИ блока определения разряда является четвертым управляющим входом блока определения разряда, второй вход первого элемента ИЛИ блока определения разряда подключен к выходу первого элемента И блока определения разряда, первьй вход первого элемента, И блока определения разряда подключен к выходу второго элемента iЛИ блока определения разряда, первым входам третьего и четвертого элементов ИЛИ блока определения разряда и входу первого элемента НЕ блока определения разряда, выход первого элемента НЕ блока определения разряда подключен к первому входу второго элемента И блока определения разряда, второй вход второго элемента И блока определения разряда подключен к выходу второго элемента НЕ, nepBEJM входам третьего, четвертого и пятого элементов И блока определения разряда и второму входу первого элемента И блока определения разряда, вход второго элемента НЕ блока определения разряда является вторым ущ)авляющим входом блока определения разряда, вход третьего элемента НЕ блока определения разряда является первым управляющим входом блока

определения разряда, первьй вход шестого элемента И блока определения разряда является шестым управляющим входом блока определения разряда,первьй вход седьмого элемента И блока определения разряда является пятым управляющим входом блока определения разряда, выход пятого элемента ИЛИ

блока определения разряда подключен к второму входу четвертого, первым входам восьмого и девятого элементов И блока определения разряда и первому входу шестого элемента ИЛИ блока определения разряда, первьй вход пятого элемента ИЛИ блока определения разряда подключен к выходу десятого и второму входу третьего элементов И блока определения разряда, второй вход пятого элемента ИЛИ блока определения разряда подключен к выходу одиннадцатого и третьему входу третьего элементов И блока определения разряда, выход седьмого элемента ИЛИ блока определения разряда подключен к третьему входу четвертого и первому входу двенадцатого элементов И блока определения разряда, выход восьмого элемента ИЛИ блока определения разряда подключен к вторым входам пятого, двенадцатого и девятого элементов И блока определения разряда, первый, второй и третий входы восьмого элемента ШШ блока определения разря- да подключены к выходам соответственно тринадцатого, четырнадцатого и пятнадцатого элементов И блока определения разряда, первьй, второй и третий входы девятого элемента ИЛИ бло- ка определения разряда подключены соответственно к выходам восьмого, двенадцатого и девятого элементов И блока определения разряда, четвертый вход девятого элемента ИЛИ блока опре деления разряда подключен к выходу шестнадцатого элемента И блока определения разряда и второму входу шестого элемента ИЛИ блока определения

разряда, третий вход пятого элемен- та И блока определения разряда подключен к выходу шестого элемента ШШ блока определения разряда, четвертый вход пятого элемента И блока определения разряда подключен к выходу десятого элемента ИЛИ блока определения разряда и второму входу восьмого -элемента И блока определения разряда, третий вход второго элемента И блока определения разряда под- t

ключен к выходу четвертого элемен та НЕ блока определения разряда, четвертый вход второго элемента И блока определения разряда подключен к второму входу третьего элемента ИЛИ бло ка определения разряда и выходу пятого элемента НЕ блока определения разряда, второй вход четвертого элемента ИЛИ блока определения разряда подключен к четвертому входу первого элемента ИЛИ блока определения разряда, выходу четвертому элемента k блока определения разряда и входу пятого элемента НЕ блока определения разряда, третий вход четвертого элемента ИЛИ блока определения разряда подключен к третьим входам первого и третьего элементов ИЛИ блока определения разряда, выходу третьего элемента И блока определения разряда и входу четвертого элемента НЕ блока определения разряда, выход шестого элемента НЕ блока определения разряда подключен к четвертому входу четвертого элемента ИЛИ блока определения разряда и пятому входу второго элемента И блока определения разряда, вход шестого элемента НЕ блока определения разряда подключен к выходу пятого элемента И блока определения разряда и пятому входу первого элемента ИЛИ блока определения разряда, первый вход семнадцатого элемента И блока определения разряда подключен к выходу третьего элемента ШШ блока определения разряда, второй вход семнадцатого элемента И блока определения разряда подключен к выходу третьего элемента, НЕ -блока определения разряда и вторым входам шестого и седьмого элементов И блока определения разряда, выход первого элемента ИЛИ блока определения разряда является выходом разряда частного блока определения разряда, выход четвертого элемента ИЛИ блока определения разряда является выходом первой блокировки блока определения разряда выход семнадцатого элемента И блока определения разряда является выходом нулевой блокировки блока опред еления разряда, выход второго элемента И блока определения разряда является выходом анализа критического разряда блока определения разряда, первый и второй входы второго элемента ИЛИ блока определения разряда являк)тся соответственно первым и вторым разрядами информационного входа блока определения разряда, первые входы девятого, одиннадцатого, восемнадцатого, девятнадцатого, двадцатого, тринадцатого, четьфнадцатого и пятнадцатого элементов И блока определения разряда являются соответственно третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым и десятым

разрядами информационного входа блока определения разряда, первьпТг вход двадцатого элемента И блока определения разряда подключен к второму входу восемнадцатого элемента И блока определения разряда и первым входам десятого элемента ИЛИ блока определения разряда и шестнадцатого элемента И блока определения разряда, пер- вьм вход девятнадцатого элемента И блока определения разряда подключен к вторым входам двадцатого и шестнадцатого элемент В И блока определения разряда и второму входу десятого элемента ИЛИ блока определения разряда, первый вход восемнадцатого элемента И блока определения разряда подключен к второму входу девятнадцатого элемента И блока определения разряда и третьим входам десятого элемента ИЛИ и шестнадцатого элемента И блока определения разряда, выход восемнадцатого элемента И блока определения разряда подключен к первому

входу седьмого элемента ИЛИ блока оп- 25 тьим управляющие входом блока управределения разряда, второй и третий входы седьмого элемента ИЛИ блока определения разряда подключены соответственно к выходам девятнадцатого и

двадцатого элементов И блока опреде- зо цией, выход второго элемента И блока

ления разряда, шестой вход первого элемента ИЛИ блока определения разряда является третьим управляющим входом блока определения разряда, выход

шестого элемента И блока определения ницы блока управления коррек1щей, выразряда подключен к третьему входу первого элемента И блока определения разряда, выход седьмого элемента И блока определения разряда подключен к вторым входам десятого и одиннад - цатого элементов И блока определения разряда, второй вход тринадцатого элемента И блока определения разряда подключен к первому входу пятнадцатоего элемента И блока управления коррекцией является выходом собственной генерации единицы блока управления коррекцией, первый вход третьего элемента И блока управления коррекцией

го элемента И блока определения раз- 45 подключен к входу второго элемента НЕ

ряда, первый вход тринадцатого элемента И блока определения разряда подключен к второму входу четьфнад- цатого элемента И блока определения разряда, второй вход пятнадцатого элемента И блока определения разряда подключен к первому входу четырнадцатого элемента И блока определения разряда, выход девятого элемента ИЛИ блока определения разряда подклочен

к шестому входу второго элемента И блока определения разряда, третий вход семнадцатого элемента И блока

блока управления коррекцией, вторым входам первого элемента И и второго элемента ИЛИ блока управления коррекцией и является первым управляю50 щим входом блока управления коррекцией, первый вход четвертого элемента ИЛИ блока управления коррекцией подключен к второму входу второго и , третьему входу первого элементов И

55 блока управления коррекцией и является вторым, информационным входом блока управления коррекцией, второй вход четвертого элемента ИЛИ блока

определения разряда подключен к выходу четвертого элемента ШУИ блока определения разряща, а блок управления коррекцией содержит четыре эле- мента ИЛИ, три элемента И и два элемента НЕ, причем выход первого элемента И блока управления коррекцией подключен к первому входу первого элемента ИЛИ блока управления коррекцией и является выходом генерации единицы блока управления коррекцией, - первьш вход первого элемента И блока управления коррекцией подключен к первому входу второго элемента И

блока управления коррекцией и к выходу первого элемента ИЛИ блока управления коррекцией, выход второго элемента ИЛИ блока управления коррекцией является выходом блокировки коррекции блока управления коррекцией, первьй вход второго элемента ИЛИ блока управления коррекцией подключен к входу первого элемента НЕ блока управления коррекцией и является треления коррекцией, выход первого элемента НЕ блока Управления коррекцией подключен к второму входу первого элемента ИЛИ блока управления коррекуправления коррекцией подключен к первому входу третьего элемента ИЛИ блока управления коррекцией, выход которого является выходом блокировки еди

ход четвертого элемента ИЛИ блока управления коррекцией является выходом сквозного критического разряда блока

управления коррекцией, выход треть- I

его элемента И блока управления коррекцией является выходом собственной генерации единицы блока управления коррекцией, первый вход третьего элемента И блока управления коррекцией

подключен к входу второго элемента НЕ

блока управления коррекцией, вторым входам первого элемента И и второго элемента ИЛИ блока управления коррекцией и является первым управляющим входом блока управления коррекцией, первый вход четвертого элемента ИЛИ блока управления коррекцией подключен к второму входу второго и третьему входу первого элементов И

блока управления коррекцией и является вторым, информационным входом блока управления коррекцией, второй вход четвертого элемента ИЛИ блока

17

управления коррекцией подключен к второму входу третьего элемента И и является первым информационным входом блока управления коррекцией, второй вход третьего элемента ИЛИ блока управления коррекцией является вторим управляющим входом блока управления коррекцией, четвертый управляю12

763718

щий вход блока управления коррекцией объединен с четвертым входом первого элемента И и с третьим входом второго элемента И блока управления кор- J рекцией, четвертый вход второго элемента И блока управления коррекцией подключен к выходу второго элемента НЕ блока управления коррекцией.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Матричное устройство для деления | 1983 |

|

SU1141402A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Однородная вычислительная структура | 1985 |

|

SU1251104A1 |

| Устройство для приведения матрицы к треугольной идемпотентной форме | 1981 |

|

SU1288714A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Устройство для деления | 1983 |

|

SU1141403A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих арифметических устройств. оперирующих с двоичными кодами. Целью изобретения является повышение быстродействия устройства за счет предварительной оценки отдельных разрядов частного с ггоследукщей (в слу чае необходимости) коррекцией уже найденных, разрядов. Устройство построено на матричном принципе с использованием способа деления с восстановлением остатка. Оно включает матрицу операционных модулей, блоки определения разряда частного и блоки управления коррекцией. Новым в устройстве является наличие блоков определения разрядов частного и блоков управления коррекцией, а также то, что каждый модуль снабжен цепями для нахождения в строке матрицы разряда, генерирующего перенос в знаковый разряд. 4 ип. (П

А/г /а

Ти f

Фи1.2

62

Ш

г. 66

Составитель С. Силаев Редактор И. Рыбченко Техред И,Попович Корректор И. Муска

1 11 I г и 111,1 I ---1 и -1 -ш-г - LL Юи I- -- -- -- - 11- IL1 - 1

Заказ 4957/47 Тираж .671Подписное

ВПШПИ Государствениого комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для деления | 1979 |

|

SU840900A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР №847703, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Карцев М.А., Брик В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| М.: Радио и связь, 1981, с | |||

| Способ обработки легко рассыпающихся и плохо высыхающих осочно-тростниковых торфов при помощи разбавленных щелочей | 1922 |

|

SU541A1 |

Авторы

Даты

1986-09-15—Публикация

1984-07-31—Подача