элементов И и пятым входом j-ro анализатора, второй вход первого элемента ИЛИ соединен с вторыми входами второго элемента ИЛИ, четвертого и восьмого элементов И и четвертьм входом j-ro анализатора, третий вход которого соединен с третьими входами первого и третьего элементов ИЛИ и третьего элемента И, с входом третьего элемента НЕ, вторым входом пятого элемента ИЛИ и вторым входом седьмого элемента И, первый вхбд которого соединен с входом четвертого элемента НЕ, с первыми входами третьего и пятого элементов ИЛИ и третьего элемента И, третьим входом второго элемента ИЛИ и вторым входом j-ro анализатора, первый вход которого соединен с вторыми входами второго и шестого элементов И и первым входом первого элемента И, второй вход которого соединен с выходом первого элемента НЕ, первым входом шестого элемента И и первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, первый вход которого соединен с выходом второго элемента НЕ, первым входом шестого элемента И и третьим входом первого элемента И, выход которого соединен с четвертыми входами первого и второго элементов ИЛИ, вторым входом третьего элемента ИЛИ, входом пятого элемента НЕ и первым входом седьмого элемента ИЛИ, второй вход которого соединен 6. выходом третьего элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ-и третьим входом четвертого элемента И, четвертый вход которого соединен с выходом пятого элемента ИЛИ и третьим входом восьмого элемента И, четвертый вход которого соединен с выходом шестого элемента НЕ и вторым входом десятого элемента И, первый вход которого соединен с первым входом восьмого /элемента ИЛИ и выходом восьмого элемента НЕ, вход которого соединен t выходом шестого элемента ИЛИ и четвёртым входом пятого элемента И, первый, второй и третий входы которого соединены соответственно с выходами первого, второго и третьего элементов ИЛИ, входы первого и второго эле ментов НЕ соединены соответственно с первым и вторым выходами переноса (j-l)-ro анализатора, выход четвертого элемента И соединен с третьим входом седьмого элемента ИЛИ, выход которого является первым выходом -го анализатора, выход десятого элемента И соединен с первым входом девятого элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, а выход - с вторым входом переноса (j+1)-ro анализатора, вход шестого элемента НЕ соединен с выходом седьмого элемента И, вькоды третьего, четвертого и пятого элементов НЕ соединены соответственно с первым, вторым к третьим входами девятого элемента И, выход которого соединен с вторым входом восьмого элемента ИЛИ, выход которого соединен с первым входом переноса (j+1)го анализатора, выход пятого элемента И соединен с входом седьмого элемента НЕ, выход которого является вторым выходом j-ro анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1983 |

|

SU1141403A1 |

| Устройство для деления | 1984 |

|

SU1257637A1 |

| Устройство для деления | 1988 |

|

SU1681303A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

| Устройство для деления | 1989 |

|

SU1683009A1 |

| Устройство для деления | 1988 |

|

SU1621034A1 |

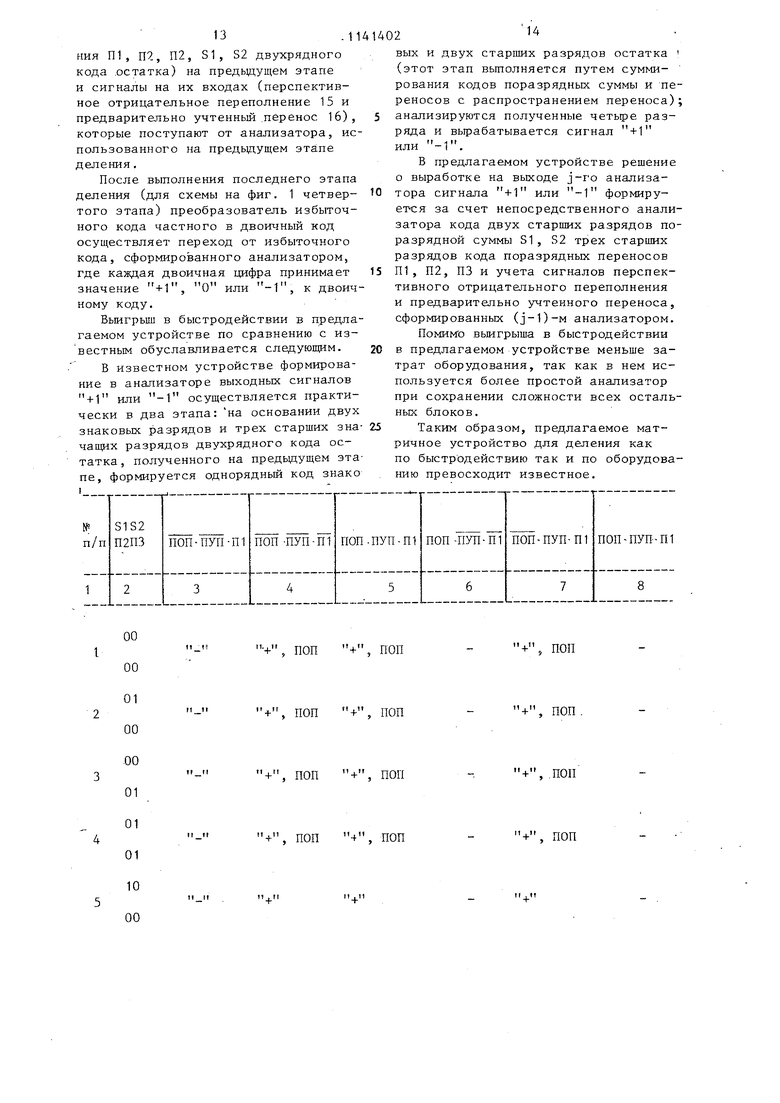

МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ, содержащее матрицу суммирующих модулей, имеющую п столбцов (п число разрядов частного) и () строк

1

Изобретение относится к вычислительной технике.

Известно устройство для деления, содержащее счетчики делимого, делителя и результата , первый и второй счетчики, переключатель, два управляющих ключа, два формирователя импульсов, триггер и элемент И П.

Недостатком устройства является малое быстродействие.

Известно устройство для умножения и деления последовательно-параллельного действия, содержащее преобразователь цифр множимого (делителя) в единичный код, реверсивные счетчики цифр -множителя (частного), ревер.сивные .счетчики произведения (делимого) , триггер реверса произведения, п групп (п - разрядность операндов) элементов И и ИЛИ t23 Недостатком данного устройства яв ляется низкое быстродействие, обуславливаемое последовательно-параллельным принципом выполнения операций. Наиболееблизким к предлагаемому по технической сущности является мат ричное устройство деления, содержащее матрицу из однотипных суммирующих модулей, расположенных по п столбцам (п - число разрядов частного) и строкам (k - число разрядов делимого) , п анализаторов (детекторов) , кодопреобразователь, формирующий двоичный код частного, раз рядные выходы частного, разрядные выходы остатка, представляемого в виде двухрядного кода, разрядные .входы кода делимого, разря дные входы делителя и управляющий вход деления, причем входы переноса, сум№1 и кратного делителя каждого (i, j)го суммирующего модуля, т.е. модуля лежащего на пересечении i-ii строки и j-ro столбца,исключая 1-й,1-е суммирующие модули и (k-f-j-1 , jj-e суммирующие модули соединены соответственно с выходом переноса (i+1, j-1)го суммирующего модуля, выходом суммы (i, j-1)-ro модуля и входом кратного делителя (i-1 , j-1)-ro модуля, входы кратного делителя (k+i-1, j)го суммирующего модуля, вход переноса которого соединен с входом вычита ния, присоединены к входу кратного делителя (k-bi-2, j-1)-ro сумт ирующего модуля, входы сумм1,1 и кратного делителя (i, 1)-го модуля, входы вычитания которого присоединены к управляющему входу деления, подключены соответственно к i-м разрядам, входы делимого и входа делителя, матричного устройства деления, первый и второй выходы i-ro разряда остатка подключены соответственно к вйходу суммы и переноса ( , п)-го суммирующего модуля матричного устройства деЛения j-й разряд выхода частного которого присоединен к j-му разряду выхода ко допреобразоватепя, j-й вход + 1 которого соединен с вьгходом + 1 j-ro анализатора и входами вычитания (i, j+1)-x суммирующих модулей, вход сложения которых подключен к j-му входу +1 кодопреобразователя и к выходу +1 j-ro анализатора, первьи второй, третий, четвертый и пятьй входы которого соединены соответст.-1 24венио с выходами переноса и суммы (i, j)-ro суммирующего модуля, с выходами переноса и суммы (i+1, j)-ro Сзммирующего модуля и выходом переноса (i-i-2, j)-ro суммирующего модуля. Особенностью данного матричного устройства для деления является то, что в его матрице выполняется суммирование с запоминанием переноса, т.е.. суммирующие модули казщого столбца формируют очередной остаток в виде двухрядного кода - кода поразрядных сумм и кода поразрядных переносов Гз . Недостатком известного устройства является малое быстродействие из-за большой задержки в анализаторе при формировании выходного сигнала +1 или -1 по результату анализа старших разрядов двухрядного кода . остатка , полученного на предыдущем этапе деления. Целью изобретения является повышение быстродействия матричного устройства для деления Поставленная цель достигается тем что в матричном устройстве для деления , содержащем матрицу сум шрующих модулей, имеющую п столбцов (п - число разрядов частного) и (n+k-l) строк (k - число разрядов делимого), преобразователь избыточного кода частного в двоичный код и п анализаторов, каждый из которых содержит первый, второй, третий, четвертый и пятый элементы И, первый, второй и третий элементы ИЛИ, первый и второй элементы НЕ, причем входы переноса, суммы и делителя каждого (i, j)-ro суммирующего модуля (i - номер строки матрицы, j - номер столбца матрицы) , .исключая (i,1)-e суммирующие модули, соединены соответственно с выходом переноса (i+1, j-1)-ro сумми рующего модуля, выходом суммы (i, j-1)-TO суммирующего модуля, входом делителя (i-1, j-1)-ro суммирующего модуля, входы суммы и дели ° суммирующего модуля соединены соответственно- с i-мы разрядами входов делимого и делителя устройства, а вход вычитания - с управляющим входом деления устройства, вход переноса (k+i-1, j)-ro суммирующего модуля соединен с входом вычитания этого суммирующего модуля, выходы суммы и переноса (n+t-1, n)-ro суммирующего модуля Соответственно с выходами двухрядного кода остатка устройства, выход j-rp разряда частного которого соеди нен с выходом j-ro разряда преобразователя избыточного кода частного в двоичный код, J-M информационным входом соединенного с первым выходом j-ro анализатора и с входом вычитания (i, j+1)-ro суммирующего модуля, вход сложения которого соединен с J-M информационным входом преобразователя избыточного кода частного в двоичный код и с вторым выходом j-ro анализатора, первый, второй, третий, четвертый и пятый входы анализатора - соответственно с выходами переноса и суммы (i, j)-ro суммирующего модуля, с выходами переноса и суммы (i+1, j)-ro суммирующего модуля и выходом переноса (i-+2, j)-ro суммирующего модуля, в каждый j-й анализатор введены дополнительно чет вертый, пятый, шестой, седьмой, вось мой и девятый элементы ИЛИ, шестой, седьмой, восьмой, девятый и десятый элементы И, третий, четвертый, пя тый, 11естой, седьмой и восьмой элементы НЕ 5 причем первый вход первого элемента ИЛИ соединен с первыми входами второго элемента ИЛИ, четвертого и восьмого элементов И и пятым входом j-ro анализатора, второй вход первого элемента ИЛИ - с вторыми вхо дами второго элемента ИЛИ, четвертого и восьмого элементов И и четвертым входом j-ro анализатора, третий вход которого соединен с третьими входами первого и Треть&го элементов ИЛИ и третьего элемента И, с входом третьего элемента НЕ, вторым входом пятого элемента ИЛИ и вторым входом седьмого элемента И, первым входом соединенного с входом четвертого элемента НЕ, с первыми входами тре тьего и пятого элементов ИЛИ и третьего элемента И, третьим входом второго элемента ИЛИ и вторым входом j-ro анализатора, первый вход которого соединен с вторыми входами второго и шестого элементов И и первьм входом первого элемента И, вторым входом соединенного с выходом первого элемента НЕ, первым входом шестого элемента И и первым входом четвер того элемента ИЖ, второй вход которого соединен с выходом второго элемента И,первьм входом соединенного с выходом второго элемента НЕ, первым входом шестого элемента И и . третьим входом первого элемента И, выход которого соединен с четвертыми входами первого и второго элементов ИЛИ, вторым входом третьего элемента ИЛИ, входом пятого элемента НЕ и первым входом седьмого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ и третьим входом четвертого элемента И, четвертым входом соединенного с выходом пятого элемента ИЛИ и третьим входом восьмого элемента И, четвертый вход которого соединен с выходом шестого элемента НЕ л вторым входом десятого элемента И, первым входом соединенного с первым входом восьмого элемента ИЛИ и выходом восьмого элемента НЕ, вход которого соединен с выходом шестого элемента ИЛИ и четвертым входом пятого элемента И, первый, второй и третий входы которого соединены соответственно с выходами первого, второго и третьего элементов ИЛИ, входы первого и второго элементов НЕ - соответственно с первым и вторым выходами переноса (j-l)-ro анализатора, выход четвертого элемента И - с третьим входом седьмого элемента ИЛИ, выход которого является первым выходом j-ro анализатора, выход десятого элемента И соединен с первым входом девятого элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, а выход - с вторым входом переноса () го анализатора, вход шестого элемента НЕ соединен с выходом седьмого элемента И, выходы третьего, четвертого и пятого элементов НЕ - соответственно с первым, вторым и третьим входами девятого элемента И, выход которого соединен с вторым входом восьмого элемента ИЛИ, выходом соединенного с первым входом переноса (j-fl)-ro анализатора, выход пятого элемента И соединен с входом седьмого элемента НЕ, выход которого явг ляется вторым выходом j-ro анализатора. на фиг. 1 приведена структурная схема матричного устройства для деления; на фиг. 2 - схема анализатора; на фиг. 3 - схема суммирующего модуля, Матричное устройство-для деления (фиг. 1) содержит суммирующие модули 1, каждый из которых имеет входы

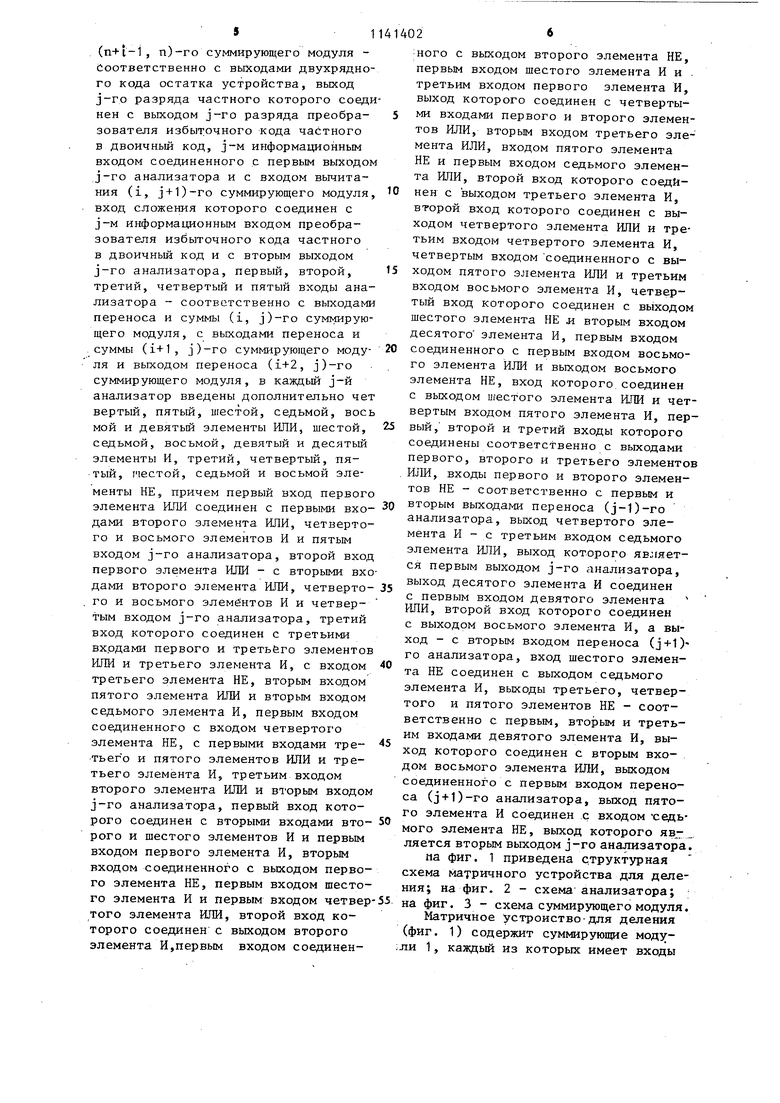

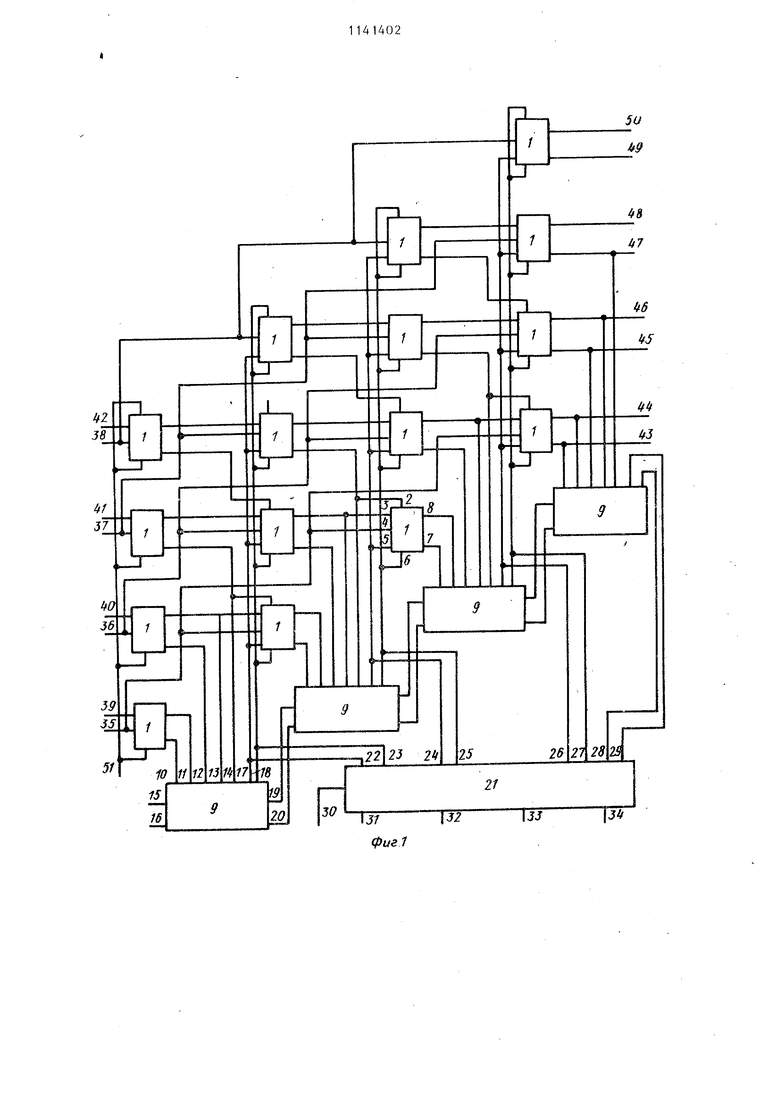

переноса 2, суммы 3, делителя 4, сложения 5 и вычитания 6, выходы переноса 7 и суммы 8, анапизаторы 9, каждый из которых имеет первый 10, второй 11, третий 12, четвертьй 13 и пятый 14 входы анализируемых разрядов остатка, первый 15 и второй 16 входы переноса, первый 17 и второй 18 выходы, первый 19 и второй 20 выходы переноса, преобразователь 21 избьпочного кода частного в двоичный код, имеющий п пар информационных входов 22 и 23, 24 и 25, 26 и 27, 28 и 29 избыточного представления частного соответственно и выходы 30 - 34 двоичного кода частного, входы делителя 35 - 38 и делимого 39 42, выходы 43 - 30 двухрядного кода остатка соответственно, управляющий 51 вход деления..

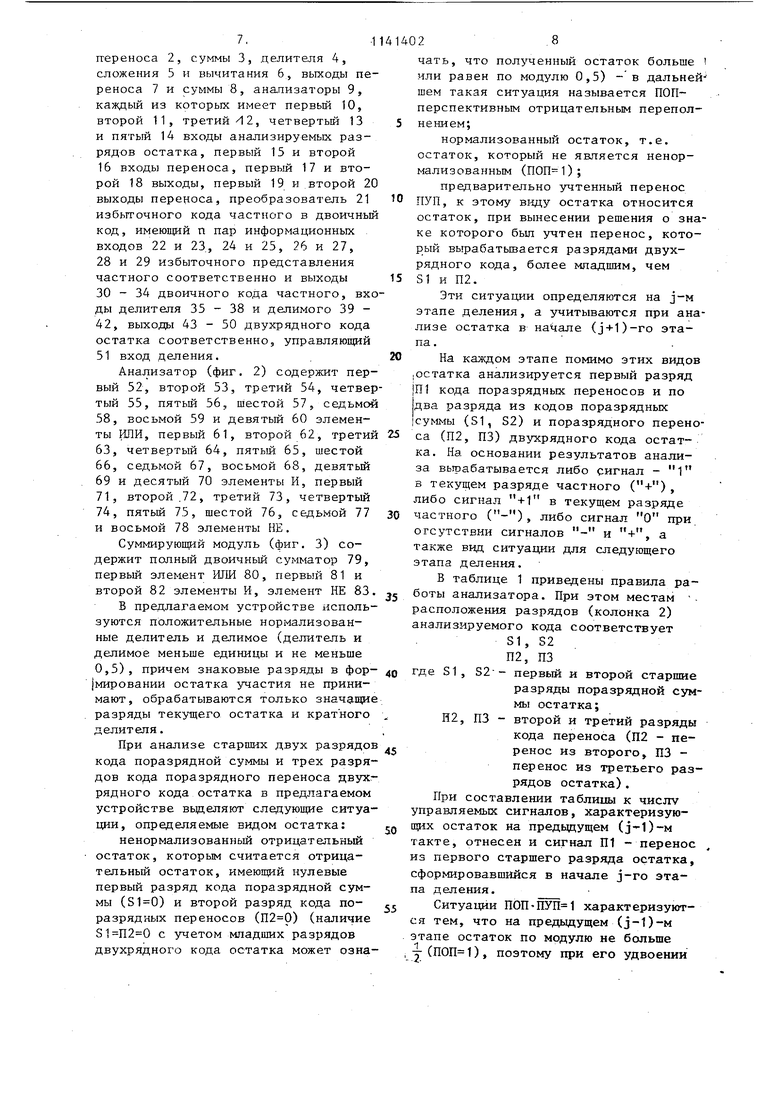

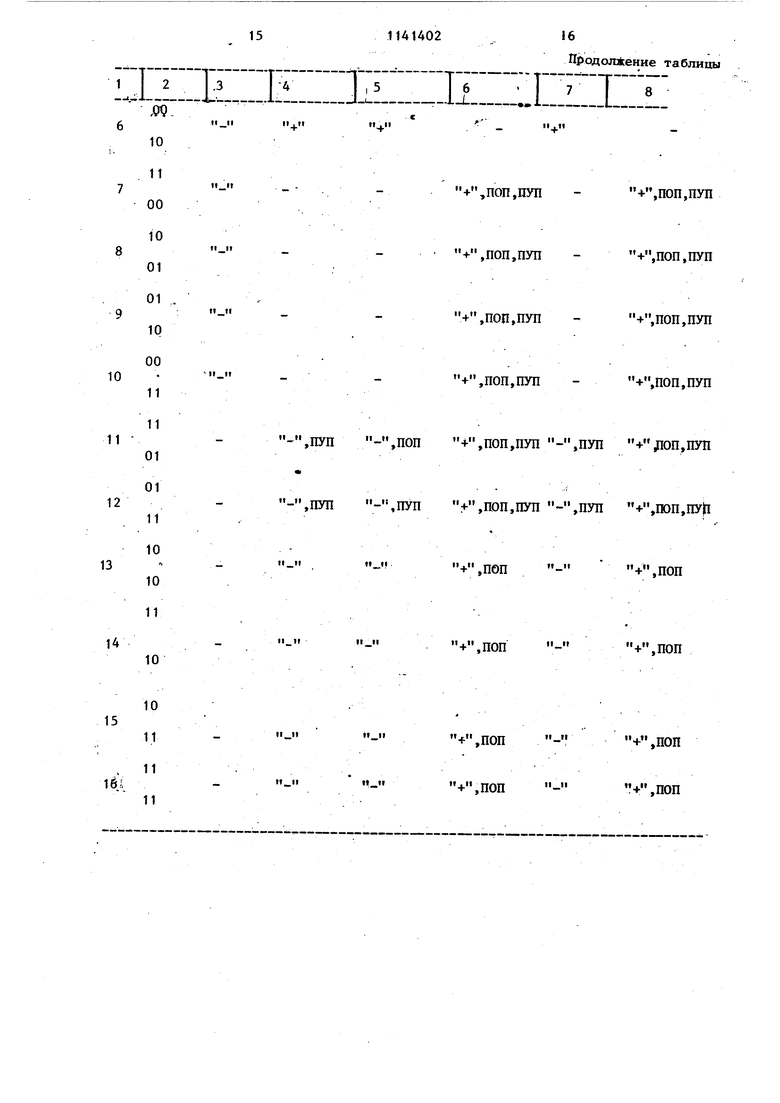

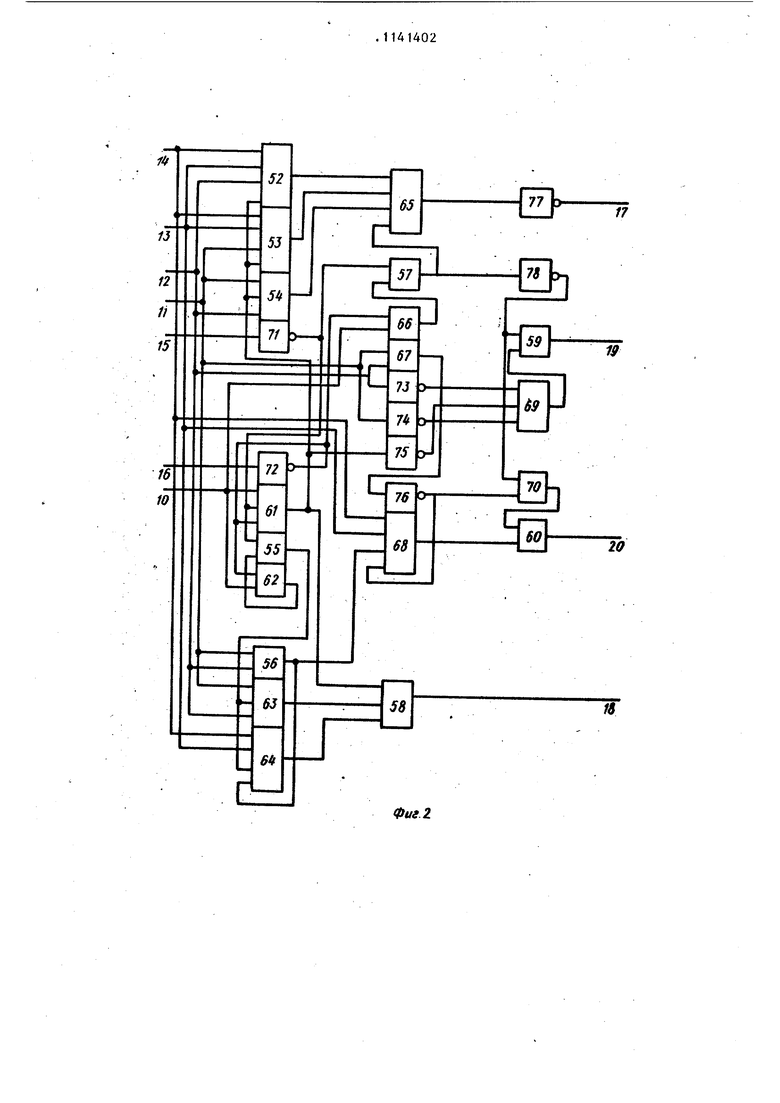

Анализатор (фиг. 2) содержит первый 52, второй 53, третий 54, четвертый 55, пятый 56,, шестой 57, седьмой 58, восьмой 59 и девятьш 60 элементы ИЛИ, первый 61, второй 62, третий 63, четвертый 64, пятый 65, шестой 66, седьмой 67, восьмой 68, девятый 69 и десятый 70 элементы И, первый 71, второй.72, третий 73, четвертый 74, пятый 75, шестой 76, седьмой 77 и восьмой 78 элементы НЕ.

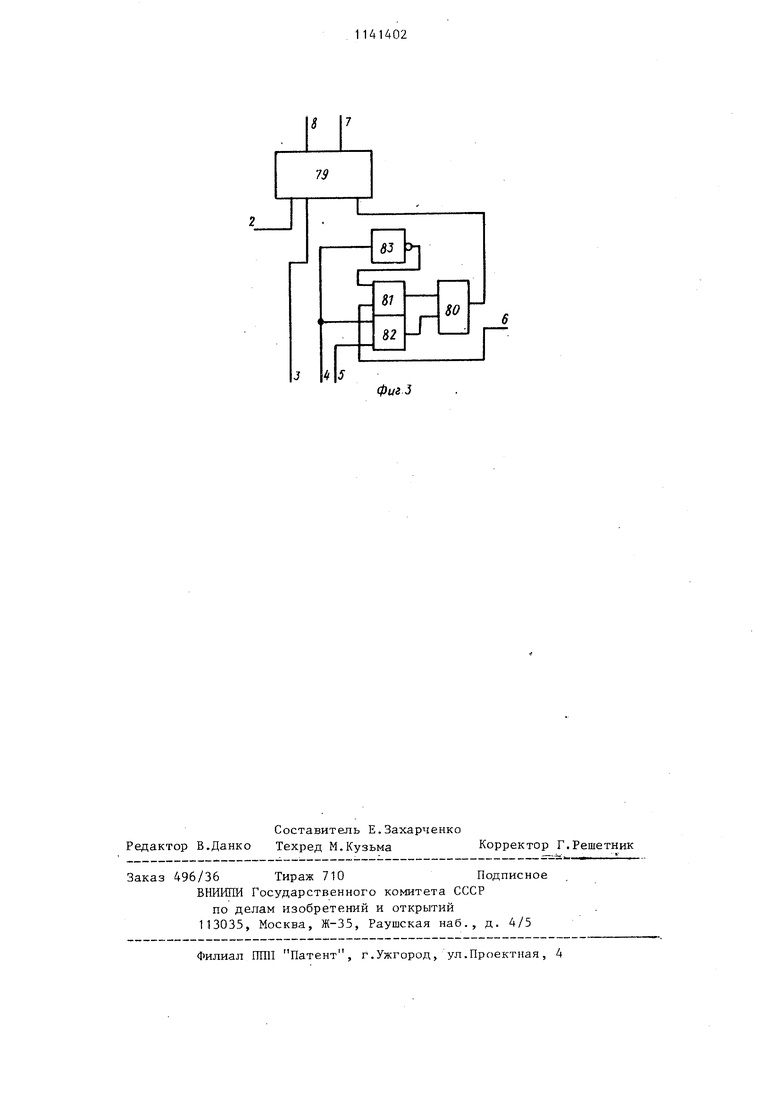

Суммируюпщй модуль (фиг. 3) содержит полный двоичный сумматор 79, первый элемент ИЛИ 80, первый 81 и второй 82 элементы И, элемент НЕ 83. В предлагаемом устройстве используются положительные нормализованные делитель и делимое (делитель и делимое меньше единицы и не меньше 0,5), причем знаковые разряды в фор|мировании остатка участия не принимают, обрабатываются только значащие разряды текущего остатка и кратного делителя.

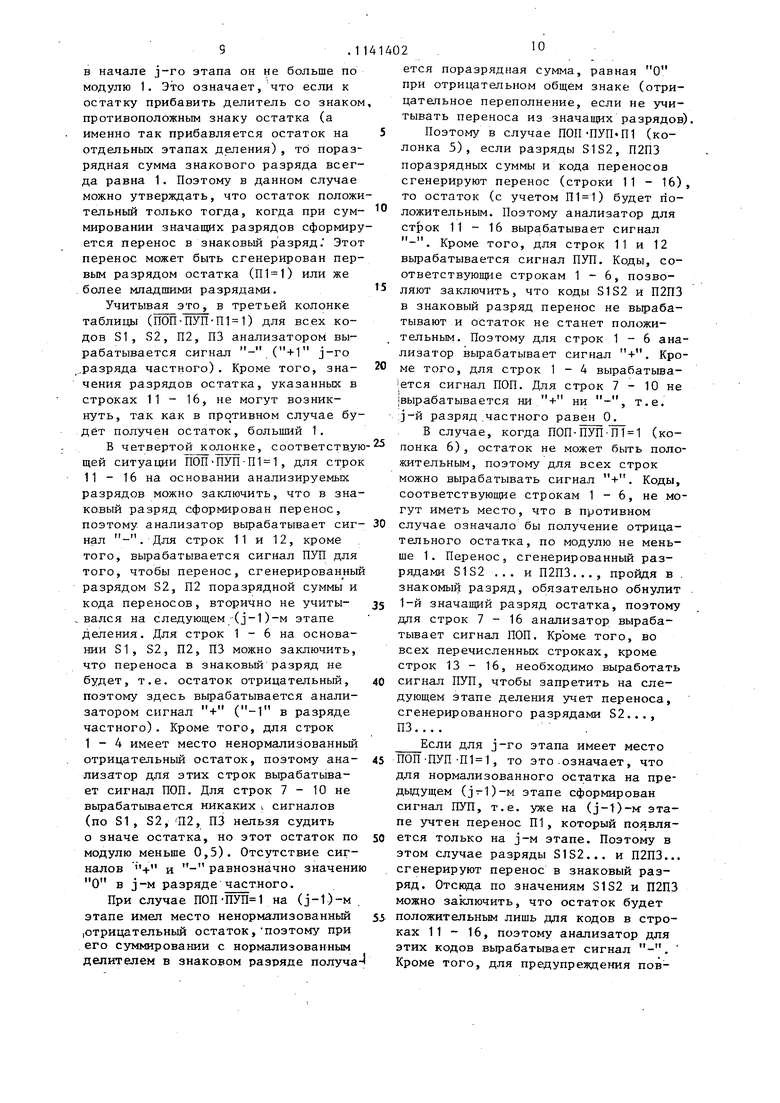

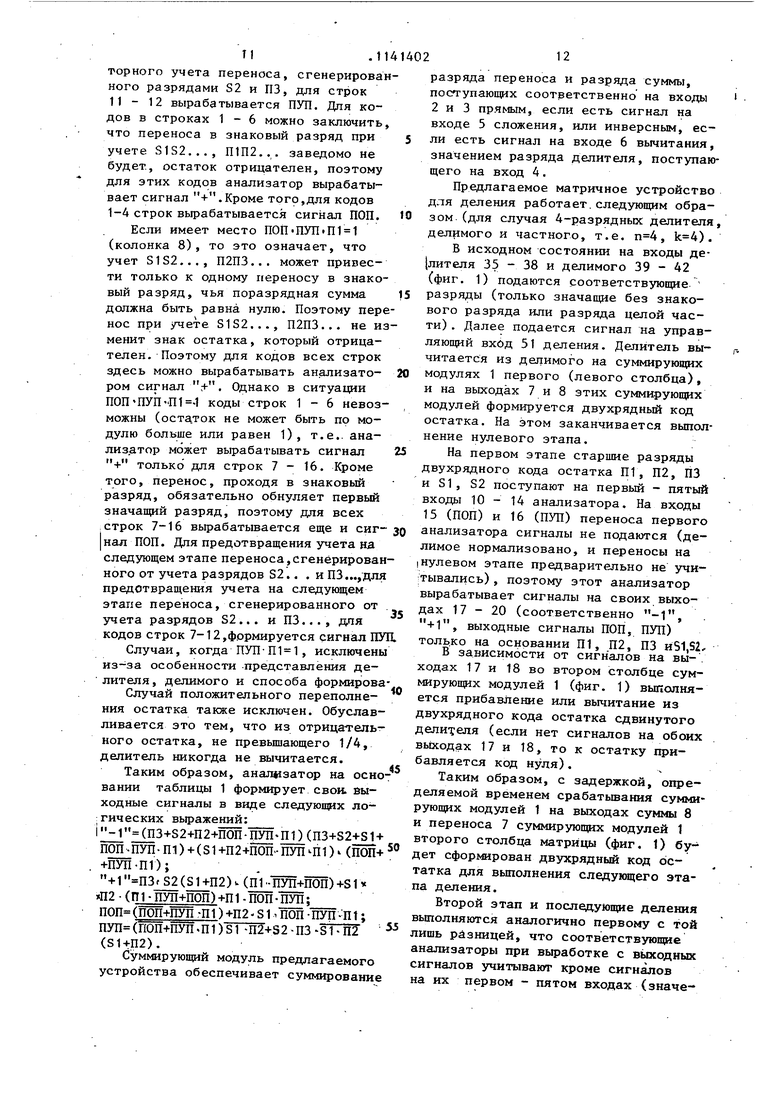

При анализе старших двух разрядов кода поразрядной суммы и трех разрядов кода поразрядного переноса двухрядного кода остатка в предлагаемом устройстве вьщеляют следующие ситуации, определяемые видом остатка:

ненормализованный отрицательный остаток, которым считается отрицательный остаток, имеющий нулевые первый разряд кода поразрядной суммы () и второй разряд кода поразрядных переносов () (наличие с учетом младших разрядов двухрядного кода остатка может означать, что полученный остаток больше или равен по модулю 0,5) -в дальней тем такая ситуация называется ПОПперспективным отрицательным переполнением;

нормализованный остаток, т.е. остаток, который не является ненормализованным ();

предварительно учтенный перенос ПУП, к этому В1еду остатка относится остаток, при вынесении решения о знаке которого был учтен перенос, который вырабатьшается разрядами двухрядного кода, более младшим, чем S1 и П2.

Эти ситуации определяются на j-м этапе деления, а учитываются при анализе остатка в начале ()-ro этапа.

На каждом этапе помимо этих видов .остатка анализируется первый разряд |П1 кода поразрядных переносов и по два разряда из кодов поразрядных суммы (S1, S2) и поразрядного переноса (П2, ИЗ) двухрядного кода остатка. На основании результатов анализа вырабатывается либо сигнал - 1 в текущем разряде частного (+), либо сигнал +1 в текущем разряде частного (-), либо сигнал О при отсутствии сигналов - и +, а также вид ситуации для следующего этапа деления.

В таблице 1 приведены правила работы анализатора. При этом местам расположения разрядов (колонка 2) анализируемого кода соответствует S1, S2 П2, ПЗ

где S1, первый и второй старшие разряды поразрядной суммы остатка;

И2, ПЗ - второй и третий разряды кода переноса (П2 - перенос из второго, ПЗ перенос из третьего разрядов остатка).

При составлении таблицы к ЧИСЛУ управляемых сигналов, характеризую1щх остаток на предьщущем (j-l)-M такте, отнесен и сигнал П1 - перенос из первого старшего разряда остатка, сформировавшийся в начале j-ro этапа деления.

Ситуации ПОП-ПУП 1 характеризуются тем, что на предыдущем (j-l)-M этапе остаток по модулю не больше у(), поэтому при его удвоении в начале j-ro этапа он не больше по модулю 1. Это означает, что если к остатку прибавить делитель со знаком противоположным знаку остатка (а именно так прибавляется остаток на отдельных этапах деления), то поразрядная сумма знакового разряда всегда равна 1. Поэто1 у в данном случае можно утверждать, что остаток положи тельный только тогда, когда при суммировании значащих разрядов сформиру ется перенос в знаковый разряд. Этот перенос может быть сгенерирован первым разрядом остатка () или же .более младшими разрядами. Учитывая это, в третьей колонке таблицы (ПОП-ПУП-П1 1) для всех кодов S1 , S2, П2, ПЗ анализатором вырабатывается сигнал - (+1 j-ro .разряда частного). Кроме того, значения разрядов остатка, указанных в строках 11 - 16, не могут возникнуть, так как в противном случае будет получен остаток, больший 1. В четвертой колонке, соответствую щей ситуапз и ПОППУП-П1 1, для строк 11 - 16 на основании анализируемых разрядов можно заключить, что в знаковый разряд сформирован перенос, поэтому анализатор вырабатывает сигнал -.Для строк 11 и 12, кроме того, вырабатывается сигнал ПУП для того, чтобы перенос, сгенерированны разрядом S2, П2 поразрядной суммы и кода переносов, вторично не учиты. вале я на следующем -(j-l )-м этапе деления. Для строк 1 - 6 на основании S1, S2, П2, ПЗ можно заключить, что переноса в знаковый разряд не будет, т.е. остаток отрицательный, поэтому здесь вырабатывается анализатором сигнал + (-1 в разряде частного). Кроме того, для строк 1 - 4 имеет место ненормализованный отрицательный остаток, поэтому анализатор для этих строк вырабатывает сигнал ПОП. Для строк 7 - 10 не вьфабатывается никаких i сигналов (по S1, S2, П2, ПЗ нельзя судить о значе остатка, но этот остаток по модулю меньше 0,5). Отсутствие сигналов + и - равнозначно значени О в J-M разряде частного. При случае ПОППУП 1 на (j-1)-M этапе имел место ненормализованньй (Отрицательный остаток,поэтому при его суммировании с нормализованным делителем в знаковом разряде получа .1 2 ,О ется поразрядная сумма, равная О при отрицательном общем знаке (отрицательное переполнение, если не учитывать переноса из значащих разрядов). Поэтому в случае П011-ПУП«П1 (колонка 5), если разряды S1S2, П2ПЗ поразрядных суммы и кода переносов сгенерируют перенос (строки 11 - 16), то остаток (с учетом П1-1) будет положительным. Поэтому анализатор для строк 11-16 вырабатывает сигнал -. Кроме того, для строк 11 и 12 вырабатывается сигнал ПУП. Коды, соответствующие строкам 1-6, позволяют заключить, что коды S1S2 и П2ПЗ в знаковый разряд перенос не вырабатывают и остаток не станет положительным. Поэтому для строк 1 - 6 анализатор вырабатывает сигнал +. Кроме того, для строк 1 - 4 вырабатыва ется сигнал ПОП. Для строк 7 - 10 не вырабатывается ни + ни -, т.е. разряд .частного равен 0. В случае, когда ПОП-ПУП- ТТ 1 (копонка 6), остаток не может быть полоясительным, поэтому для всех строк можно вырабатывать сигнал +. Коды, соответствующие строкам 1 - 6, не могут иметь место, что в противном случае означало бы получение отрицательного остатка, по модулю не меньше 1. Перенос, сгенерированный разрядами S1S2 ... и П2ПЗ..., пройдя в . знакомый разряд, обязательно обнулит . 1-й значашзий разряд остатка, поэтому для строк 7-16 анализатор вырабатывает сигнал ПОП. Кроме того, во всех перечисленных строках, кроме строк 13 - 16, необходимо выработать сигнал ПУП, чтобы запретить на следующем этапе деления учет переноса, сгенерированного разрядами S2,.. , ПЗ для j-ro этапа имеет место ПОП-ПУП П1 1, то это .означает, что для нормализованного остатка на предьщущем (j-1)-M этапе сформирован сигнал ПУП, т.е. уже на (j-O-w этапе учтен перенос П1, который появляется только на J-M этапе. Поэтому в этом случае разряды S1S2... и П2ПЗ... сгенерируют перенос в знаковый разряд. Отсвда по значениям S1S2 и П2ПЗ можно заключить, что остаток будет положительным лишь для кодов в строках 11 - 16, поэтому анализатор для этих кодов вырабатывает сигнал -. Кроме того, для предупреждения повторного учета переноса, сгенерирован ного разрядами S2 и ИЗ, для строк 11-12 вырабатывается ПУП. Для кодов в строках 1 - 6 можно заключить что переноса в знаковый разряд при учете S1S2..., П1П2... заведомо не будет, остаток отрицателен, поэтому для этих кодов анализатор вырабатывает сигнал +.Кроме того,для кодов 1-4 строк вырабатывается сигнал ПОП. Если имеет место ПОППУП П1 1 (колонка 8), то это означает, что учет S1S2..., П2ПЗ... может привести только к одному переносу в знако вый разряд, чья поразрядная сумма должна быть равна нулю. Поэтому пер нос при S1S2..., П2ПЗ... не и менит знак остатка, который отрицателен. Поэтому для кодов всех строк здесь можно вырабатывать анализатором сигнал ,+. Однако в ситуации ПОППУП П1 -1 коды строк 1 - 6 навоз можны (оста.ток не может быть по модулю больше или равен 1), т.е.. анализатор может вырабатывать сигнал + только для строк 7 - 16. Кроме того, перенос, проходя в знаковый разряд, обязательно обнуляет первый значащий разряд, поэтому для всех строк 7-16 вырабатывается еще и сиг I нал ПОП. Для предотвращения учета на следующем этапе переноса,сгенерирова ного от учета разрядов S2.. .и П3,..,дл предотвращения учета на следующем этапе переноса, сгенерированного от згчета разрядов S2.. . и ПЗ..., дня кодов строк 7-12,формируется сигнал П Случаи, когда ПУП-П1 1, исключен из-за особенности -представления делителя, делимого и способа формиров Случай положительного переполнения остатка также исключен. Обуслав ливается это тем, что из отрицатель ного остатка, не превышающего 1/4, делитель никогда не вычитается. Таким образом, анализатор на осн вании таблицы 1 формирует свои, выходные сигналы в виде следующих ло:гических выражений; (ПЗ+82+П2+ПОП-ПУП П1)(ПЗ+52-«-ЗИ ПОГЬПУП-П1) + (51+П2+ПОП-ПУПП) (ПОП +ПУП-П1);. (SJN;n2) у(П1-ПУП+ПОП)+51 П2 (П1 ПУП+ПОП) -t-n 1 - ПОП ПУП; ПОП (ПОП+ПУП -П1 ) ПОППУДЧИ; ПУП(ПОП+ПУП.П1)81-П2+32-ПЗ-81-П2 (81+П2). Суммирующий модуль предлагаемого устройства обеспечивает суммировани разряда переноса и разряда суммы, поступающих соответственно на входы 2 и 3 прямым, если есть сигнал на входе 5 сложения, или инверсным, если есть сигнал на входе 6 вычитания, значением разряда делителя, поступающего на вход 4. Предлагаемое матричное устройство для деления работает, следующим образом, (для случая 4-разрядньк делителя, делимого и частного, т.е. , ). В исходном состоянии на входы де(лителя 35 - 38 и делимого 39 - 42 (фиг. 1) подаются соответствующие разряды (только значащие без знакового разряда или разряда целой части) . Далее подается сигнал на управляющий вход 51 деления. Делитель вычитается из делимого на суммирующих модулях 1 первого (левого столбца), и на выходах 7 и 8 этих суммирующих модулей формируется двухрядный код остатка. На этом заканчивается выполнение нулевого этапа. На первом этапе старшие разряды двухрядного кода остатка П1, П2, ПЗ и S1, S2 поступают на первый - пятый входы 10 - 14 анализатора. На входы 15 (ПОП) и 16 (ПУП) переноса первого анализатора сигналы не подаются (делимое нормализовано, и переносы на нулевом этапе предварительно не учи:Тывались), поэтому этот анализатор вырабатывает сигналы на своих выходах 17-20 (соответственно -1, -И, выходные сигналы ПОП, ПУП) только на основании П1, П2, ПЗ riS1,S2. В зависимости от сигналов на вы- . ходах 17 и 18 во втором столбце суммирующих модулей 1 (фиг. 1) выполняется прибавление или вычитание из двухрядного кода остатка сдвинутого делителя (если нет сигналов на обоих вьЬсодах 17 и 18, то к остатку прибавляется код нуля). Таким образом, с задержкой, определяемой временем срабатывания суммирующих модулей 1 на выходах суммы 8 и переноса 7 суммирующих модулей 1 второго столбца матрицы (фиг. 1) бует сформирован двухрядный код остатка для выполнения следующего этапа деления. Второй этап и последук1щие деления выполняются аналогично первому с той ишь разницей, что соответствующие анализаторы при выработке с выходных игналов учитывают кроме сигналов а их первом - пятом входах (значения П1, т, П2, S1, S2 двухрядного кода .остатка) на предьщущем этапе и сигналы на их входах (перспективное отрицательное переполнение 15 и предварительно учтенный перенос 16), которые поступают от анализатора, использованного на предьщущем этапе деления.

После выполнения последнего этапа деления (для схемы на фиг. 1 четвертого этапа) преобразователь избыточного кода частного в двоичный код осуществляет переход от избыточного кода, сформированного анализатором, где каждая двоичная цифра принимает значение +1, О или -1, к двоичному коду,

Вьигрыш в быстродействии в предлагаемом устройстве по сравнению с известным обуславливается следующим.

В известном устройстве формирование в анализаторе выходных сигналов +1 или -1 осуществляется практически в два этапа: на основании двух знаковьп ; разрядов и трех старших зна чащих разрядов двухрядного кода остатка, полученного на предыдущем этапе, формируется однорядный код знако I

+, поп +, поп

Ч, поп +, поп

+, поп +, поп

Ч, поп 4, поп

вых и двух старших разрядов остатка (этот этап ньшолняется путем суммирования кодов поразрядных суммы и переносов с распространением переноса) анализируются полученные четыре разряда и вырабатывается сигнал +1 или -1,

В предлагаемом устройстве решение о выработке на выходе j-ro анализатора сигнала +1 или -1 формируется за счет непосредственного анализатора кода двух старших разрядов поразрядной суммы S1, S2 трех старших разрядов кода поразрядных переносов П1 , П2, ПЗ и учета сигналов перспективного отрицательного переполнения и предварительно учтенного переноса, сформированных (j-l)-M анализатором.

Помимо вьмгрыша в быстродействии в предлагаемом устройстве меньше затрат оборудования, так как в нем используется более простой анализатор при сохранении сложности всех остальных блоков.

Таким образом, предлагаемое матричное устройство Для деления как по быстродействию так и по оборудованию превосходит известное.

+, поп

Ч, поп

+, ЛОП

+, поп

52

5J

5tt

71

65

17

66

19

67

73

69

72

16 10

61

35 62

76

6J

IB

58

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для деления | 1979 |

|

SU840900A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Арифметика цифровых машин | |||

| М., Наука, 1969, с.515519 (прототип). | |||

Авторы

Даты

1985-02-23—Публикация

1983-08-31—Подача