Од

сд

QD Ю

1U06592

Изобретение относится к вычислительной технике и предназначено для формирования тетрады суммы частичных произведений при умножении двоичных и двоично-десятичных (в коде 8-4-2-1) чисел. Модуль целесообразно применять в быстродействующих операционных устройствах.

Цель изобретения - повьшение быст- соответственно на 1, 2, 3 разряда

родействия.

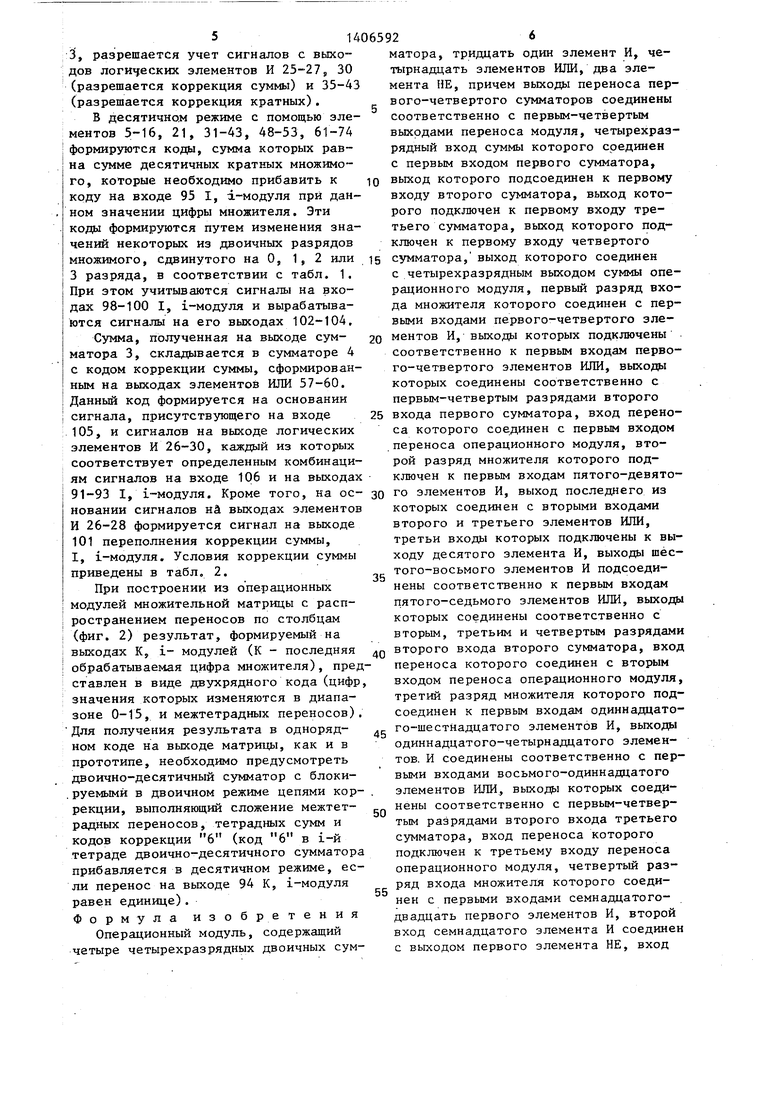

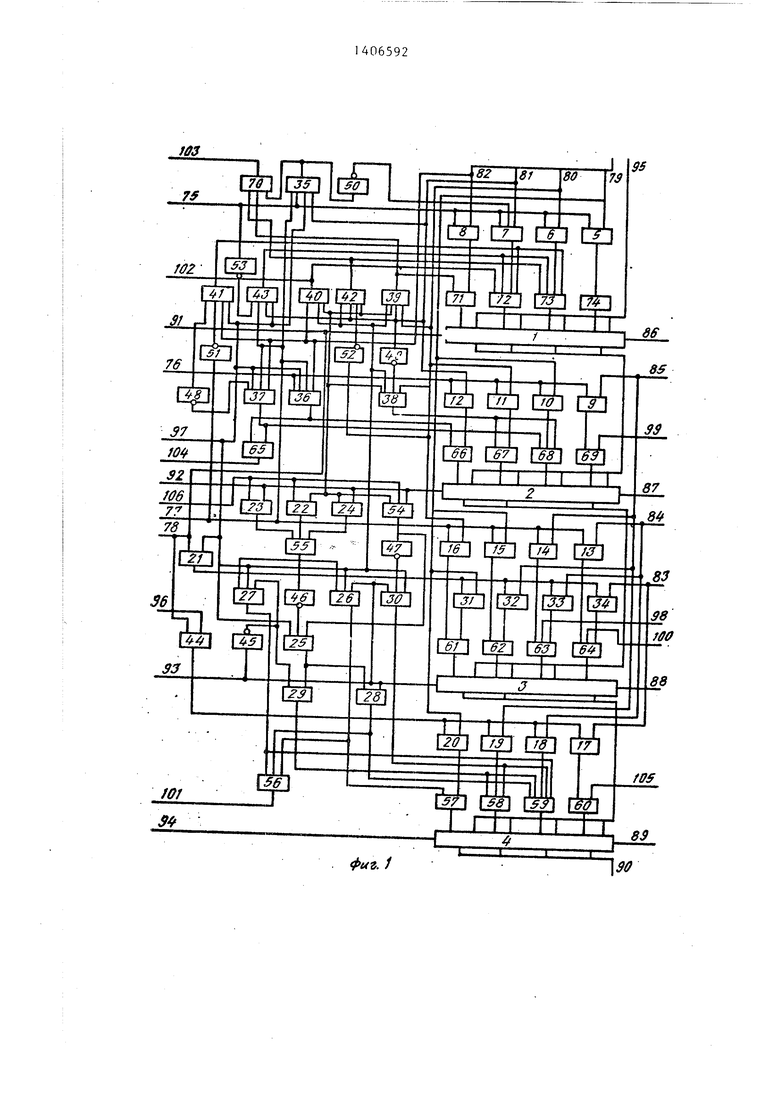

На фиг. 1 приведена структурная схема операционного модуля; на фиг.2- вариант использования модуля в составе матрицы умножения.

Операционный модуль содержит четырехразрядные сумматоры 1-4, элементы И 5-44, элементы НЕ 45-33, элементы ИЛИ 54-74, первый-четвертый разряды

влево с последующей коррекцией сдв нутого кода. При этом допускается представление цифр кратных множимо (как и сумм на выходе сумматоров) 15 диапазоне 0-15 (т.е. используются

недействительные комбинации для пр ставления десятичных цифр). Коррек ция кратных выполняется с помощью схемы коррекции, представленной ло

и ИЛИ 65-74.

Коррекция кратных осуществляется путем поправки сдвинутых десятичных кодов внутри данного модуля (К,

25 К

К.

К,

к,

75-78 входа множителя, первый-седьмой 20 ческими элементами И 35-43, НЕ 48-53 разряды 79-85 входа множимого, входы 86-89 переноса, четырехразрядный выход 90 суммы, выход 91-94 переноса, четырехразрядный вход 95 суммы, парафаз- ные входы двоичного 96 и десятичного 97 умножения, входы 98-100 поправки кратных, выход 101 переполнения коррекции суммы, выходы 102-104 поправки кратных, вход 105 переполнения коррекции суммы, вход 106 переноса входной суммы.

Операционный модуль выполняет ум- ножение тетрады множителя на тетраду множимого (с учетом значений трех старших разрядов соседней младшей его тетрады) и прибавление полученного значения к сформированной сумме частичных произведений. Результат на выходе модуля формируется в виде тет35

tt

1,-+ , ,4 Ч,Р выработки трех поправок кратных ПК1, ПК2, ПКЗ на выходах 102-104 для ближайшего старшего модуля, обслуживающего ту же цифру множителя, что и данный мо- 30 дуль. Поправки К , К g осуществляют ввод в однократное множимое единицы в разряды соответственно с весами 2, 4, 8. Поправки , У-Ч осуществляют ввод в двукратное множимое единицы в разряды с весами соответственно 2, 4, 8. Поправка блокирует единицу в разряде с весом 4 однократного множимого. Поправки ПК1, ПК2, ПКЗ с выходов 102-104 поступают в соседний старший модуль и вводят единицы:

рады суммы, четырех тетрадных переносов и трех поправок кратных.

При обработке двоично-десятичных операндов для прибавления к тетраде предадущей суммы частичных произведений кратных мно(имого М (однократ- ного М, двукратного 2М, четырехкратного 4м, восьмикратного .8М) используются сумматоры 1-73. Достигается это за счет того, что 8М и 4М учитьшаются на одном сумматоре 3 (в коде 8, 4, 2, 1 десятичная цифра не может содержать одновременно единицу в разрядах с весами 2 и 2 ). Освободившийся сумматор 4 используется для прибавления к результату двоичного суммирования на сумматорах 1-3 суммарной коррекции. Суммарный код коррекции формируется по правилу , где S - количество перено

сов, возникающих при двоичном сложении кратных М, 2м, 4М или 8М. В модуле при работе с десятичными операндами допускается представление цифр промежуточных результатов в диапазоне 0-15.

Формирование 2М, 4М и 8М осуществляется на основе сдвига множимого

влево с последующей коррекцией сдвинутого кода. При этом допускается представление цифр кратных множимого (как и сумм на выходе сумматоров) в диапазоне 0-15 (т.е. используются

недействительные комбинации для представления десятичных цифр). Коррекция кратных выполняется с помощью схемы коррекции, представленной логии ИЛИ 65-74.

Коррекция кратных осуществляется путем поправки сдвинутых десятичных кодов внутри данного модуля (К,

5 К

К.

К,

к,

0 ческими элементами И 35-43, НЕ 48-53

5

0

г

tt

1,-+ , ,4 Ч,Р выработки трех поправок кратных ПК1, ПК2, ПКЗ на выходах 102-104 для ближайшего старшего модуля, обслуживающего ту же цифру множителя, что и данный мо- 0 дуль. Поправки К , К g осуществляют ввод в однократное множимое единицы в разряды соответственно с весами 2, 4, 8. Поправки , У-Ч осуществляют ввод в двукратное множимое единицы в разряды с весами соответственно 2, 4, 8. Поправка блокирует единицу в разряде с весом 4 однократного множимого. Поправки ПК1, ПК2, ПКЗ с выходов 102-104 поступают в соседний старший модуль и вводят единицы:

ПК1 - в разряд с весом 2 четырехкратного множимого (вход 98 соседнего модуля);

ПКЗ - в разряд с весом 1 четырехкратного множимого (вход 100 соседнего юдуля),

ПК2 - в разряд с весом 1 двукратного множимого (вход 99 соседнего модуля). Особенностью реализации коррекции кратных является то, что поправка сдвинутых множимых осуществляется за счет введения или блокировки единиц в их отдельных разрядах, т.е. без суммирования.

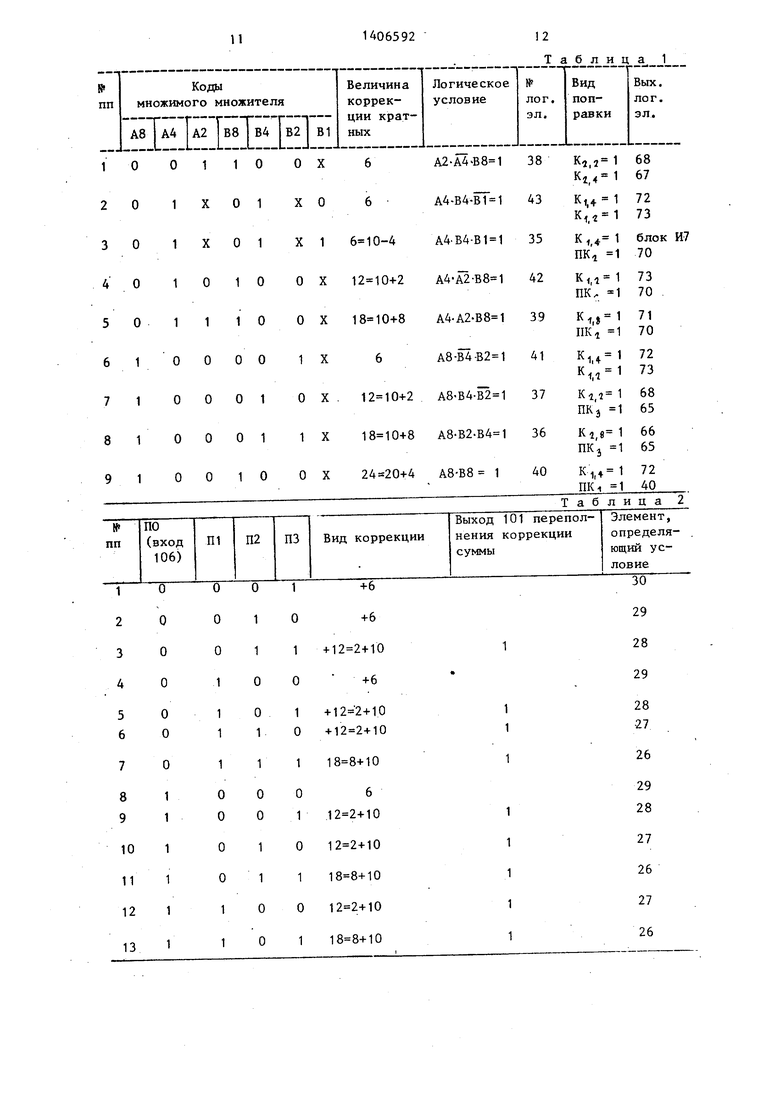

Возможные виды коррекции кратных множимого приведены в табл. 1.

Формирование коррекции суммы в модуле осуществляется на основании

0

5

3

сигнала на входе 106 переноса для входной суммы (ПО), поступающего с выхода 94 соседнего модуля, выход 90 суммы которого связан с входом 95 суммы данного модуля, а также сигна- jioB тетрадного переноса сумматоров 1-3 (соответственно выходы 91, 92, 93 (П1, П2, ПЗ).

В табл. 2 приведены возможные виды коррекции суммы. Возникновение случая ПО ПГП2 1 невозможно.

Коррекция суммы и сигнал на выходе 101 переполнения коррекции суммы формируется логической цепью, включающей элементы 22-30, 44-47, 54-60.

Модуль используется в качестве составной части матричного устройства умножения шестнадцатиричных и двоично-десятичных чисел. При применении способа умножения, начиная с младших разрядов множителя со сдвигом множимого и с распространением тетрадных переносов по столбцам, связь I, i- модуля (модуля умножения 1-й цифры множителя на i-ю цифру множимого) с соседними модулями матрицы приведена на фиг. 2. На разряды 79-85 входа множимого I, i-мо- дуля поступают соответственно двоичные разряды с внутритетрадными весами 2,°, 2 2, 2 i-й цифры множимого li и три старших разряда с внутритетрадными весами 2 2, 2 соседней младшей (1-1)-й цифры множимого Ii-1. На разряды 75-78 входа множителя 1,1-модуля поступают разряды с

2° 2 2

внутритетрадными весами 2, 2 , , 2 1-й цифры множителя X-j, Для случая двоичных кодов цифре операнда модуля соответствует группа из четырех двоичных разрядов, т.е. 16-рична цифра.

На вход суммы 95 и переноса входной суммы 106 1,1-модуля поступают соответственно сумма и перенос с выхдов 90 и 94 (1-1), (1+1)-модуля, на входы 86-89 переноса 1,1-модуля поступают соответственно сигналы с выхода 94 переноса (1-1), i-модуля, с выходов 91-93 I, (i-1)-модуля.

На входы 98-100 поправки кратных, вход 105 переполнения коррекции суммы I, i-модуля поступают сигналы с выходов 102-104 поправки и выхода 10 переполнения коррекции суммы I, (i-1)-модуля.

1,1-модуль работает в режиме двоичного или десятичного умножения.

14

я

о1

065924

Режим двоичного умножения устанавливается для случая двоичных (шест- надцатеричных) операндов за счет формирования единичного сигнала на входе 96 двоичного умножения и нулевого сигнала на входе 97 десятичного умножения. В этом случае сдвинутые на нуль, один, два, три разряда (в сто10 Рону старших) коды i-й цифры с учетом трех старших разрядов (i-1)-и цифры множимого проходят на выходы (в зависимости от значений соответствующих разрядов 1-й цифры множителя)

15 групп логических элементов И 5-8,

9-12, 13-16, 17-20. С выходов указанных групп двоичные кратные множимого поступают соответственно через элементы ИЛИ 74-71, 70-66, 64-61, 60-57

20 на разряды с весами 2°, 2, 2, 2 первого входа сумматоров 1-4. Таким образом, код, поступивший на вход 95 I, i-модуля, складывается в сумматоре 1 с переносом, поступившим на вход 86

25 I, i-модуля, и (если разряд 75 с весом 2 1-й цифры множителя равен единице, В1 1) с кодом однократного множимого М. Сумма с выхода сумматора 1 поступает на сумматор 2 и складыва30 ется с переносом, поступившим на вход 87 I, i-модуля, и (если В2 1) с двукратным множимым 2М. Сумма с выхода сумматора 2 поступает на сумматор 3 и складьшается с переносом, поступившим на вход 88 I, i-модуля, и (если ВЗ 1) с четырехкратным множимым 4М. Сумма с выхода сумматора 3 поступает на сумматор 4, где складывается с переносом, поступившим на вход 89 I, i-модуля, и (если В4 1) с восьмикратным кодом множимого 8М. С выхода сумматора 4 сумма передается на выход 90 I, i-модуля, где вместе с сигналами на выходах 91-94 переноса

45 будет представлять результат умноже35

40

50

55

кия 1-й цифры множителя на i-ю цифру множимого.

При работе в режиме десятичного умножения 1 поступает на вход 97 десятичного умножения, О - на вход 96 двоичного умножения. В этом случае запрещается прохождение сдвинутого на 3 разряда множимого через логические элементы И 17-20 и далее через ИЛИ 60-57 на первый вход сумматора 4, разрешается прохождение сдвинутого на 3 разряда множимого через логические элементы И 31-34, ИЛИ 64-61 на первый вход сумматора

3, разрешается учет сигналов с выходов логических элементов И 25-27, 30 (разрешается коррекция суммы) и 35-43 (разрешается коррекция кратных).

В десятичном режиме с помощью элементов 5-16, 21, 31-43, 48-53, 61-74 формируются коды, сумма которых равна сумме десятичных кратных множимого, которые необходимо прибавить к коду на входе 95 I, а-модуля при данном значении цифры множителя. Эти коды формируются путем изменения значений некоторых из двоичных разрядов множимого, сдвинутого на о, 1, 2 или 3 разряда, в соответствии с табл. 1. При этом учитываются сигналы на входах 98-100 I, i-модуля и вырабатываются сигна.т1Ы на его выходах 102-104.

Сумма, полученная на выходе сумматора 3, складывается в сумматоре 4 с кодом коррекции суммы, сформированным на выходах элементов ИЛИ 57-60. Данный код формируется на основании сигнала, присутствующего на входе 105, и сигналов на выходе логических элементов И 26-30, каждый из которых соответствует определенным комбинациям сигналов на входе 106 и на выходах 91-93 I, i-модуля. Кроме того, на основании сигналов на выходах элементов И 26-28 формируется сигнал на выходе 101 переполнения коррекции суммы, I, i-модуля. Условия коррекции суммы приведены в табл. 2.

При построении из операционных модулей множительной матрицы с распространением переносов по столбцам (фиг. 2) результат, формируемый на выходах К, i- модулей (К - последняя обрабатываемая цифра множителя), представлен в виде двухрядного кода (цифр, значения которых изменяются в диапазоне 0-15, и межтетрадных переносов). Для получения результата в однорядном коде на выходе матрицы, как и в прототипе, необходимо предусмотреть двоично-десятичный сумматор с блоки- руемымй в двоичном режиме цепями коррекции, выполняющий сложение межтетрадных переносов, тетрадных сумм и кодов коррекции 6 (код 6 в i-й етраде двоично-десятичного сумматора рибавляется в десятичном режиме, еси перенос на выходе 94 К, i-модуля авен единице). Формула изобретения

Операционный модуль, содержащий етыре четырехразрядных двоичных сум

5

5

матора, тридцать один элемент И, четырнадцать элементов ИЛИ, два элемента НЕ, причем выходы переноса пер- вого-четвертого сумматоров соединены соответственно с первым-четвертым выходами переноса модуля, четырехразрядный вход суммы которого соединен с первым входом первого сумматора, выход которого подсоединен к первому входу второго сумматора, выход которого подключен к первому входу третьего сумматора, выход которого подключен к первому входу четвертого сумматора, выход которого соединен с четырехразрядным выходом суммы операционного модуля, первый разряд входа множителя которого соединен с первыми входами первого-четвертого зле- 0 ментов И, выходы которых подключены соответственно к первым входам первого-четвертого элементов ИЛИ, выходы которых соединены соответственно с первым-четвертым разрядами второго входа первого сумматора, вход переноса которого соединен с первым входом переноса операционного модуля, второй разряд множителя которого подключен к первьм входам пятого-девято- го элементов И, выход последнего из которых соединен с вторыми входами второго и третьего элементов ИЛИ, третьи входы которых подключены к выходу десятого элемента И, выходы шёс- того-восьмого элементов И подсоединены соответственно к первым входам пятого-седьмого элементов ИЛИ, выходы которых соединены соответственно с вторым, третьим и четвертым разрядами второго входа второго сумматора, вход переноса которого соединен с вторым входом переноса операционного модуля, третий разряд множителя которого подсоединен к первым входам одиннадцато- го-шестнадцатого элементов И, выходы одиннадцатого-четырнадцатого элементов, И соединены соответственно с первыми входами восьмого-одиннадцатого элементов ИЛИ, выходы которых соединены соответственно с первым-четвертым разрядами второго входа третьего сумматора, вход переноса которого подключен к третьему входу переноса операционного модуля, четвертый разряд входа множителя которого соединен с первыми входами семнадцатого- двадцать первого элементов И, второй вход семнадцатого элемента И соединен с выходом первого элемента НЕ, вход

0

5

0

5

0

5

которого подключен к второму разряду входа множимого и к вторым входам второго, седьмого, четырнадцатого, восемнадцатого и девятнадцатого элементов И, третий вход которого соединен с третьим разрядом входа множимого, вторыми входами третьего, восьмого и шестнадцатого элементов И, третьим входом семнадцатого элемента И и с входом второго элемента НЕ, выход которого подключен к третьему входу восемнадцатого элемента И, четвертый вход которого подсоединен к вторым входам девятого, пятнадцатого, двад- цатого элементов И, третьему входу шестнадцатого элемента И, четвертым входам семнадцатого и девятнадцатого элементов И и к входу десятичного умножения операционного модуля, пер- вый разряд входа множимого которого соединен с вторыми входами первого, шестого, тринадцатого элементов И и первым входом двадцать второго элемента И, выход которого соединен с первым входом двенадцатого элемента ИЛИ, выход которого соединен с четвертым разрядом второго входа четвертого сумматора, третий и второй разряды которого подключены соответ- ственно к выходам тринадцатого и четырнадцатого элементов ИЛИ, первые входы которых соединены соответственно с выходами двадцать третьего и двадцать четвертого элементов И, четвертый разряд входа множимого операционного модуля подключен к второму входу четвертого элемента И, третьим входам девятого, двадцатого элементов И и пятнадцатого элемента И, вы- ход которого соединен с вторым входом седьмого элемента ИЛИ, первый вход двадцать пятого элемента И- подключен к пятому разряду входа множимого операционного модуля, шестой разряд ко- торого соединен с вторым входом одиннадцатого и первым входом двадцать четвертого элементов И, седьмой разряд входа множимого операционного модуля подсоединен к вторым входам пятого и двенадцатого элементов И и к первому входу двадцать третьего элемента И, выходы двадцать шестого и двадцать седьмого элементов И соединены соответственно с вторыми вхо- дами одиннадцатого и десятого элементов ИЛИ, третий выход переноса операционного модуля соединен с первым входом двадцать восьмого элемента .И,

о 5 Q

5

выход которого подключен к второму входу тринадцатого элемента ИЛИ,первые входы двадцать девятого и тридцатого элементов И соединены соответственно с первым и вторым выходами переноса операционного модуля, первый вход поправки кратных которого соединен с вторым входом восьмого элемента ИЛИ, выход тридцать первого элемента И подключен к второму входу пятого элемента ИЛИ, отличающийся тем, что, с целью повышения быстродействия, он содержит девять элементов И, семь элементов ИЛИ, семь элементов НЕ, причем вход переноса входной суммы операционного модуля подключен к вторым входам двадцать девятого и тридцатого элементов И и к перво гу входу пятнадцатого элемента ИЛИ, выход которого соединен с первым входом тридцать второго элемента И и с входом третьего элемента НЕ, выход которого подключен к второму входу двадцать восьмого элемента И, третий вход которого соединен с входом десятичного умножения операционного модуля, первыми входами десятого, тридцать первого, тридцат.ь третьего, тридцать четвертого и тридцать пятого элементов И и вторым входом тридцать второго элемента И, третий вход которого подключен к выходу четвертого элемента НЕ, вход которого соединен с вторыми входами тридцать третьего и тридцать четвертого элементов И и с выходом шестнадцатого элемента ИЛИ, входы которого соединены соответственно с выходами двадцать девятого, тридцатого и тридцать шестого элементов И, первый вход последнего из которых соединен с первым входом двадцать девятого элемента И и вторым входом пятнадцатого элемента ИЛИ, третий вход которого подсоединен к второму входу тридцать шестого элемента И и второму выходу пере - носа операционного модуля, третий выход переноса которого соединен с третьим входом тридцать третьего элемента И, первым входом тридцать седьмого элемента И и с входом пятого элемента НЕ, выход которого подключен к третьему входу тридцать четвертого элемента И и первому входу тридцать восьмого элемента И, второй вход ко- торого соединен с выходом тридцать второго элемента И и вторым входом тридцать седьмого элемента И, выход

которого подсоединен к первому входу семнадцатого элемента ИЛИ и второму входу четырнадцатого элемента ИЛИ, третий вход которого соединен с выходом тридцать четвертого элемента И I и вторым входом семнадцатого элемента ИЛИ, третий вход которого соедине с выходом тридцать третьего элемента И и BTopbiM входом двенадцатого эле- мента Шш, выход семнадцатого элемента ИЛИ подключен к выходу переполнения коррекции суммы операционного модуля, вход переполнения коррекции суммы которого соединен с первым вхо- дом восемнадцатого элемента ИЛИ, второй вход которого подсоединен к выходу двадцать пятого элемента И, второй вход которого соединен с вторыми I входами двадцать второго, двадцать третьего и двадцать четвертого элементов И и с выходом двадцать первого I элемента И, второй вход которого соединен с входом двоичного умножения операционного модуля, второй вход поп равки кратных которого соединен с первым входом девятнадцатого элемента ИЛИ, второй вход которого подключен |к выходу пятого элемента И,выход во- с ёмнадцатого элемента И соединен с вторым входом шестого элемента ИЛИ и третьим входом пятого элемента ИЛИ, второй вход которого подсоединен к первому входу двадцатого элемента ИЛИ, второй вход которого соединен I с выходом пятнадцатого элемента И, I четвертый вход которого подсоединен к первому входу девятого элемента И ;И к входу шестого элемента НЕ, выход iкоторого соединен с вторым входом тридцать первого элемента И, третий вход которого подключен к второму входу десятого элемента И, первому входу шестнадцатого элемента Ни входу седьмого элемента НЕ, выход которого соединен с четвертым входом девятого элемента .И, третий вход которого подключен к четвертому входу тридцать первого элемента И, выход двадцатого элемента ИЛИ соединен с

первым выходом поправки кратных операционного модуля, первьй разряд вхо5 0 5 0 Q

5

5

0

да множителя которого подсоединен к четвертому входу шестнадцатого элемента И и входу восьмого элемента НЕ, выход которого соединен с третьим входом десятого элемента И, четвертый вход которого подключен к третьему входу семнадцатого элемента И, выход которого соединен с четвертым входом второго элемента ИЛИ и первым входом двадцать первого элемента ИЛИ, выход которого соединен с вторым выходом поправки кратных операционного модуля, третий выход поправки кратных которого подсоединен к выходу двадцатого элемента И и четвертому входу третьего элемента ИЛИ, выход шестнадцатого элемента И подключен к второму входу двадцать первого элемента ИЛИ и через девятый элемент НЕ к третьему входу третьего элемента И, второй вход четвертого элемента ИЛИ соединен с третьим входом двадцать первого элемента ИЛИ и выходом девятнадцатого элемента И, первый вход которого подключен к второму входу тридцать пятого элемента И, выход которого соединен с первыми входами двадцать шестого, двадцать седьмого, тридцать девятого и сорокового элементов И, вторые входы которых подключены соответственно к первому, седьмому, шестому и пятому разрядам входа множимого операционного модуля, третий вход поправки кратных которого подсоединен к второму входу девятого элемента ИЛИ, третий вход которого Соединен с выходом тридцать девятого элемента И, выход сорокового элемента И подключен к третьему входу восьмого элемента ИЛИ, выход тридцать восьмого элемента И соединен с третьим входом тринадцатого элемента ИЛИ и с четвертым входом четырнадцатого элемента ИЛИ, пятый вход которого соединен с выходом двадцать восьмого элемента И, выходы восемнадцатого и девятнадцатого элементов ИЛИ соединены соответственно с первыми разрядами второго входа четвертого и второго сумматоров.

9S

фиг. 1

Фие.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство умножения двоично-десятичных цифр | 1982 |

|

SU1073771A1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Устройство для умножения десятич-НыХ чиСЕл | 1979 |

|

SU817704A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

Изобретение относится к вычислительной технике и предназначено для формирования тетрады суммы частичных произведений при умножении двоичных и двоично-десятичных (в коде 8-4-2-1) чисел. Целью изобретения является повьш1ение быстродействия. Операционный модуль содержит четыре .четырехразрядных сумматора, двадцать шесть двухвходовых. элементов И, шесть трехвходовых элементов И, семь четы- рехвходовых элементов И, девять элементов НЕ, одиннадцать элементов ИЛИ с соответствукщими связями между ними. 2 ил. 2 табл. S S (Л

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-30—Публикация

1984-08-13—Подача