Изобретение относится к автоматике и вычислительной технике и может быть использовано в частотно- измерительной и преобразующей аппаратуре.

Целью изобретения является расширение класса решаемых задач за счет обеспечения умножения на коэффициент , изменяющийся в зависимости от значения периода входной частоты.

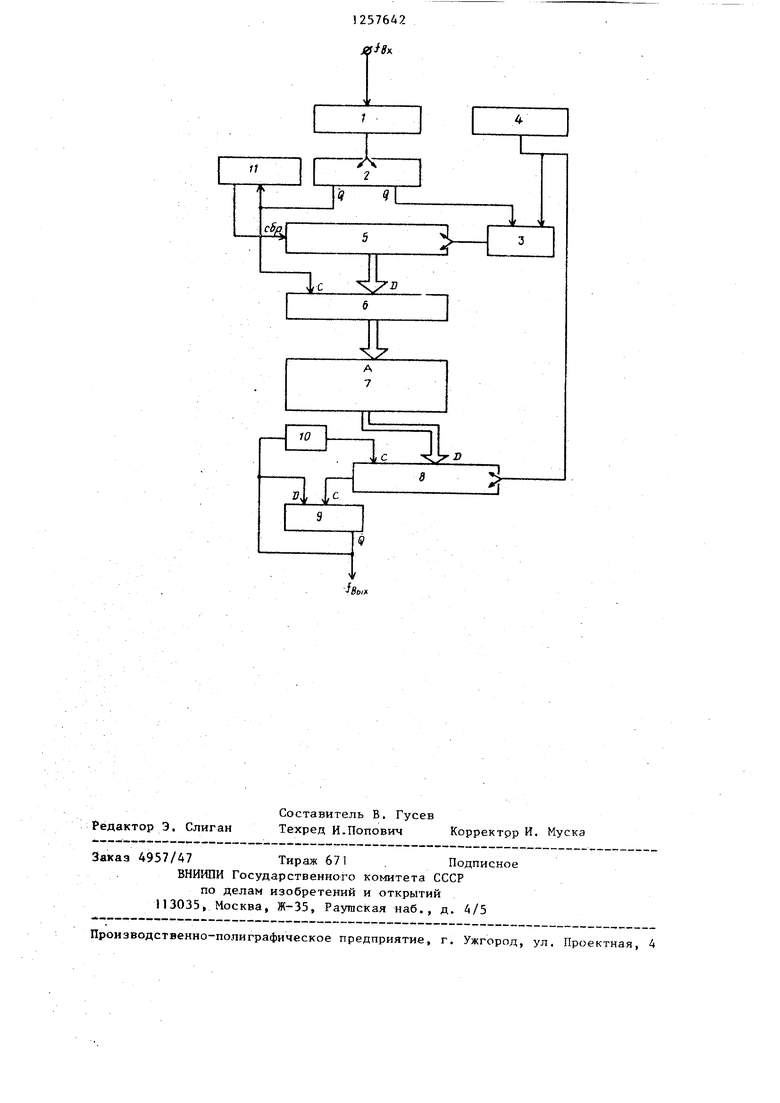

На чертеже представлена функциональная схема цифрового умножителя частоты.

Умножитель частоты содердит нуль- орган I, триггер 2, элемент И 3, генератор 4 тактовых импульсов, счетчик 5, регистр 6, блок 7 памяти, счетчик 8, триггер 9, элемент 10 задержки, генератор 11 одиночных импульсов.

Цифровой умножитель частоты работает следующим образом.

Сигнал умножаемой синусоидальной частоты fgj( поступает на нуль- орган 1, который выделяет момент прохождения входного сигнала через нуль и формирует импульсы, период повторения которых равен полупериоду частоты входного сигнала.

Импульсы с нуль-органа 1 поступают на счетный вход триггера 2, ко- Торый делит частоту нуль-органа I на два, образуя на выходе триггера 2 частоту прямоугольных импульсов, повторяющих f jji .

Выходной положительный сигнал с прямого Q-выхода триггера 2 открывает по переднему фронту элемент И 3 и разрешает прохождение импульсов частоты заполнения ,(,„ на счетный вход счетчика 5.

Счетчик 5, предварительно обнулявши сигналом от генератора 11 одиночных импульсов, производит подачу импульсов частоты заполнения f,, эа полупериод входной частоты, образуя двоичный код N, эквивалентный величине полупериода входной частота f J, .

Значение кода в счетчике 5 полупериода, принимаемое за полупериод входной частоты, равно:

ш -IlL .7 т.. f

чап

2 f

вл

(О

-ia 2 N

(2)

ах

ЯЯП

- здп

10

)5

20

57642

где Tg - период входной частоты;

частота генератора импульсов;

период частоты заполнения;f- - частота входного сигнала.

О л

Код со счетчика 5 поразрядно подается на D-входы буферного регистра 6, где фиксируется передним положительным фронтом сигнала, поступающего от Q-выхода триггера 2.

Таким образом, регистр 6 фиксирует значение полупериода входной частоты один раз за период ее следования.

Код, зафиксированный на регистре 6, поступает на адресный вход блока 7 памяти„

Постоянное запоминающее устройство (7) представляет собой матрицу постоянного или полупостоянного ЗУ, информация в которой разделяется по адресам, составляя информационное слово. Каждое информационное слово тесно связано со своим адресом, в котором оно зафиксировано. При пода че кода адреса на адресный вход ПЗУ через время выборки , информационное слово, соответствующее этому 30 адресу, поразрядно формируется на информационном выходе блока 7 памяти.

Информационные слова, зафиксированные в блоке 7, представляют собой произведение Р

Р А -К, (3). где А - содержимое кода адреса; К - коэффициент умножения.

Р N . К

Код Р с выхода ПЗУ поступает на информационный вход счетчика 8, где фиксируется передним фронтом импульса, поступающего с выхода элемента 10 задержки.

25

35

К

40

(4)

45

Со старшего разряда счетчика 8 сигнал переполнения поступает на синхронизирующий вход триггера 9, инверсный выход которого связан с собственным информационным входом. Таким образом триггер 9 образует делитель на два. Передний фронт ин- .версного выхода триггера 9, задержанный на элементе 10 задержки, вписывает новое значение произведения Р.

Счетчик 8 в рассматриваемом умножителе может выполняться вычитающим,,

с блока памяти выбирается значении, или суммирующим, с блока памяти выбирается .

к на вход счетчика поступаа f от генератора имто на выходе счетчика форчастота с периодом т1

Твх

ebfX

2 Т

Т, 2

К-Т

та

здп

К

р)

С учетом деления на триггере 9

или

еь(х

ill.

f .

ex к К

Работа, цифрового умножителя частоты иллюстрируется следующими примерами.

Пример 1 . Пусть fp, 100 кГц коэффициент умножения ,6; f 10 мГц. Тогда согласно выражению (1) счетчик.5 за 1/2 периода фиксирует код . В ячейке блока 7 памяти с адресом 50 заносится(пользо- вателем на этапе создания устройства код Р 50 X 1,6 80.

Этот код под действием адресного кода фиксируется на счетчике 8. Следовательно, период выходного сигнала счетчика 8 равен (см. вьфаже- ние 5)

80 X О, 1 В (мкс), с учетом выражения (6) TBUX (мкс), т.е вьи .5 кГц.

Пример 2. Пусть fg, 100 кГц; К 0,625; f, мГц.

При этом .

I

8ЫХ

32-2-0,1

10 179,08 кГц,

р м у л а и

4

3 о

б р е т е н и я

to

5

20

; 25 )

.

30

35

40

45

Умножитель частоты, содержавд-гй генератор тактовых импульсов, нуль- орган, первый триггер, первый счетчик, генератор одиночных импульсов, элемент И и регистр, информационные входы которого соединены соответственно с разрядными выходами первого счетчика, счетный вход которого соединен с выходом элемента И, прямой выход первого триггера соединен с первым входом элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, инверсный выход первого триггера соединен с тактовым выходом регистра и с входом запуска генератора одиночных импульсов, выход которого соединен с входом установки в О первого счетчика, тактовый вход первого триггера соединен с выходом нуль- органа, вход которого является входом умножителя, отличающий- с я тем, что, с целью расширения класса решаемых задач за счет обеспечения умножения на коэффициент, изменягацийся в зависимости от значения периода входной частоты, в него введены блок памяти, второй счетчик, второй триггер и элемент задержки, причем адресные входы блока памяти соединены соответственно с разрядньп 0{ выходами регистра, а разрядные выходы блока памяти соединены соответственно с информационными входами второго счетчика, выход переполнения которого соединен с тактовым входом второго триггера, инверсный выход второго триггера соединен с его информационным входом и входом элемента задержки, вход которого соединен с входом разрешения записи по информационным входам второго счетчика, счетный вход которого соединен с выходом генератора тактовых импулб- сов, инверсный выход второго триггера является выходом умножителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1984 |

|

SU1238070A1 |

| Многоканальный микропрограммный умножитель частоты | 1983 |

|

SU1144107A1 |

| Умножитель частоты | 1973 |

|

SU714634A1 |

| Генератор функциональных зависимостей | 1983 |

|

SU1130853A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Генератор линейного напряжения | 1986 |

|

SU1354403A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для умножения | 1984 |

|

SU1176325A1 |

| Микропрограммное устройство для обработки прерываний | 1983 |

|

SU1126956A1 |

Умножитель частоты относится к области автоматики и вычислительной техники и может быть использован в частотно-измерительной технике и преобразующей аппаратуре. Цель изобретения - расширение класса решаемых задач за счет обеспечения умножения на коэффициент, изменяю1тийся в зависимости от значения периода входной частоты. Устройство содержит нуль-орган, триггер, элемент И, генераторы тактовых и одиночного импульсов, счетчик, элемент задержки. Измеряется период входной частоты, код которого является адресным входом блока памяти, в который занесены произведения этого кода на заданный коэффициент. Это произведение преобразуется в частоту отдельным счетчиком. Такое построение устройства обеспечит умножение на любой, включая дробный, больший и меньший единицы коэффициент, 1 ил. (Л ND СД Ф to

9 ц

.3.

;

-X

Редактор Э. Слиган

Составитель В, Гусев

Техред И.Попович Корректрр И. Муска

Заказ 4957/47 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раугаская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Умножитель частоты | 1973 |

|

SU714634A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный микропрограммный умножитель частоты | 1983 |

|

SU1144107A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-15—Публикация

1984-10-15—Подача